ARENBERG DOCTORAL SCHOOL Faculty of Engineering Science

# Lightweight Roots of Trust for Modern Systems-on-Chip

**Pieter Maene**

Supervisor: Prof. dr. ir. Ingrid Verbauwhede Dissertation presented in partial fulfilment of the requirements for the degree of Doctor of Engineering Science (PhD): Electrical Engineering

October 2019

# Lightweight Roots of Trust for Modern Systems-on-Chip

#### Pieter MAENE

Supervisor: Prof. dr. ir. Ingrid Verbauwhede

Examination Committee:

Prof. dr. Adhemar Bultheel Chair

Prof. dr. ir. Yves Willems Chair

Prof. dr. ir. Frank Piessens

Prof. dr. ir. Marian Verhelst

Prof. dr. ir. Bjorn De Sutter

UGent, Belgium

Prof. Dr.-Ing. Felix Freiling

FAU Erlangen-Nürnberg, Germany Dissertation presented in partial fulfilment of the requirements for the degree of Doctor of Engineering Science (PhD): Electrical Engineering

October 2019

© 2019 KU Leuven – Faculty of Engineering Science Uitgegeven in eigen beheer, Pieter Maene, Kasteelpark Arenberg 10 bus 2452, B-3001 Leuven (Belgium)

Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt worden door middel van druk, fotokopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever.

All rights reserved. No part of the publication may be reproduced in any form by print, photoprint, microfilm, electronic or any other means without written permission from the publisher.

## Preface

§

The study at this university and obtain my engineering degree. The week before, I had joined the student organisation's welcome weekend, where I not only met some truly amazing people that would become my friends, but also remember saying that I would never consider getting a PhD. However, I believe I can now say with some confidence that eighteen-year-old me did not really know what he was talking about, and am happy to have decided differently when I graduated.

First and foremost, I therefore want to thank Prof. Ingrid Verbauwhede for extending me this incredible opportunity, and allowing us to freely explore our ideas, readily giving direction when we need it. Over the past five years, I have learned more about cryptography and software security, computer architectures, and the technologies enabling these, than I could ever have imagined.

I also want to express my sincere gratitude to Prof. Felix Freiling for his thoughtful insights, the many invitations to visit his chair in Germany, and the warm welcome every time we were there. My thanks also go out to Prof. Frank Piessens for his close collaboration, considering our solutions from a different perspective and sharing his expertise. I am also grateful to the additional members of my jury, Prof. Bjorn De Sutter and Prof. Marian Verhelst, for their valuable feedback. Finally, I want to thank the chairs of my preliminary and public defences, Prof. Yves Willems and Prof. Adhemar Bultheel.

None of this would have been possible without the many incredible co-authors I had the privilege of working with, and I am thankful to all of you for your experienced help and for looking at my proposals with a critical eye. Additionally, I want to thank our trusted computing colleagues from DistriNet for the uniquely interactive CosiNet meetings, which therefore consistently overran. I am particularly grateful to Job Noorman for his enthusiasm in helping me contribute to his projects, as well as Jan Tobias Mühlberg and Jo Van Bulck for the interesting discussions. I also want to express my gratitude to Jens Hermans

and Roel Peeters for trusting me to come along on their spin-off adventure. Furthermore, I am indebted to Johannes Götzfried for showing me a wonderful time on every visit to Erlangen, for introducing me to climbing and taking me snowshoeing, but especially for the many warm conversations.

Over the years, I've had the privilige of sharing an office with some genuinely great people. I would therefore like to acknowledge Kimmo Järvinen and Anthony Van Herrewege for their kind and helpful pointers when I was just starting out. I also want to thank Furkan Turan and Toon Purnal for their delightful company and productive discussions. However, I particularly want to mention Ruan de Clercq, who moved along with me through the different offices, and thank him for his friendship and all the exciting climbing trips.

It has also been an absolute pleasure to be a part of COSIC, and I could not have wished for a friendlier group of colleagues. I would like to recognise the members of the Hardware Group for the informative presentations and appreciated feedback, but just as much everyone else at the group, who were always ready to answer questions or give advice. I will continue to remember the entertaining lunch conversations, the deliciously generous cake events, adventurous weekends, and the relaxing evenings, sharing a beer on the castle's lawn. This group could not do without the care and assistance of its amazing technical and administrative people. In particular, I want to express my gratitude to Wim Devroye for his expert handling of our travel arrangements and equipment purchases, and especially to Péla Noé for making us feel at home.

This thesis would not have been written without the financial help of different organisations, notably the KU Leuven and the InvasIC project funded by the German Research Foundation. I also want to acknowledge the Research Foundation - Flanders for offering me an SB PhD fellowship.

After first discovering VTK during that weekend before my first year, I later joined this organisation, and I am incredibly thankful to everyone there and at Student IT for patiently bearing with me while I learned new skills. I also want to extend my appreciation to my friends, and I hope we will continue to gather regularly for many years to come. Although they are no longer all around, I am grateful to my grandparents for passing on their passions and believing in me. Furthermore, I want to thank my little sister Liesbeth for lending her ear whenever needed and showing me other points of view. Thank you, Mom and Dad, for believing in me and for always being there unconditionally, ready with help and guidance. Lastly, to my girlfriend Delphine, I could not have hoped for someone kinder by my side, and I am grateful for your gentle support.

> Pieter Maene Leuven, October 2019

## Abstract

§

ECTRONIC devices have become indispensable parts of our homes and businesses. They help us stay in touch with each other and events around the world, as well as facilitate us by controlling our appliances and driving complex manufacturing installations. Consequently, they interact with physical processes, and while they can operate stand-alone, these increasingly capable devices are commonly remotely accessible. Combined, these evolutions not only lead to advanced automation, but also expose our homes and factories to security risks. Indeed, attackers have exploited software vulnerabilities, causing fridges to send out spam, the shutdown of multi-national companies, and even the disruption of nuclear enrichment facilities.

Various defence strategies have been proposed in response, one of which is trusted computing. The core concept behind it is to ensure that an attacker cannot elicit undefined behaviour from the device. Due to the limitations of software-based approaches, countermeasures that can protect against strong adversaries have to be rooted in hardware, guaranteeing their functional integrity. Crucially, the extraction of critical functionality into self-contained modules enables many of the protection mechanisms introduced by trusted computing.

In this thesis, we present novel lightweight building blocks that contribute to the realisation of this goal at different levels of the design hierarchy. First, various hardware-based trusted computing mechanisms presented in literature are surveyed, leading to definitions of common security properties and a comparison of all considered designs. Since cryptographic primitives are at the core of these solutions, often impacting performance, we also evaluated seven block ciphers with respect to their area and latency. Our third contribution is a key distribution service for Systems-on-Chip, allowing secure management of symmetric device secrets through tight integration of efficient hardware and software components. Finally, we discuss the design and evaluation of two processor-based mechanisms, which rely on cryptographic units to protect sensitive code and data.

## Samenvatting

§

EKTRONISCHE apparaten verbinden ons niet alleen met elkaar, maar vereenvoudigen ook onze levens door zowel huishoudtoestellen als complexe industriële installaties aan te sturen. Hoewel ze alleenstaand kunnen werken, zijn deze steeds krachtigere apparaten doorgaans ook vanop afstand bereikbaar. Deze evoluties hebben niet alleen gezorgd voor verregaande automatisatie, maar maken onze woningen en fabrieken ook kwetsbaar voor veiligheidsrisico's. Zo hebben aanvallers zwakheden in software uitgebuit om koelkasten spam te laten uitsturen, de werking van multinationals plat te leggen en zelfs nucleaire verrijkingsprocessen te verstoren.

Daarop zijn verschillende verdedigingsstrategieën voorgesteld, waaronder betrouwbare berekening, met als kernidee dat de aanvaller geen ongedefinieerd gedrag mag kunnen uitlokken van het apparaat. De beperkingen van oplossingen op basis van software vereisen dat tegenmaatregelen die beschermen tegen sterke aanvallers, verankerd zijn in hardware, waar hun functionele integriteit gegarandeerd is. Hierbij maakt het onderbrengen van kritieke functies in autonome modules verscheidene van deze beveilingsmechanismes mogelijk.

In deze thesis presenteren we nieuwe goedkope bouwblokken die bijdragen aan de realisatie van dit doel op verschillende niveaus van de ontwerphiërarchie. We bouwen eerst op een overzicht en vergelijking van verscheidene hardwaregebaseerde ontwerpen uit de literatuur om definities op te stellen van gedeelde beveiligingseigenschappen. Gezien deze oplossingen steunen op cryptografische primitieven, waar ze prestaties kritisch beïnvloeden, evalueren we de oppervlakte en wachttijd van zeven blokcijfers. Onze derde bijdrage is een oplossing voor sleutelverdeling op systemen-op-chip, die veilig beheer van symmetrische apparaatgeheimen mogelijk maakt door middel van doorgedreven integratie van efficiënte hardware- en softwarecomponenten. Tot slot bespreken we het ontwerp en de evaluatie van twee processoraanpassingen die gebruik maken van cryptografische eenheden om gevoelige code en gegevens te beschermen.

§ Contents

| ostrac   | ct                                                           | iii                                                                                           |  |  |

|----------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| men      | vatting                                                      | v                                                                                             |  |  |

| Contents |                                                              |                                                                                               |  |  |

| st of    | Abbreviations                                                | xvi                                                                                           |  |  |

| st of    | Figures                                                      | xvii                                                                                          |  |  |

| st of    | Tables                                                       | xix                                                                                           |  |  |

| Intro    | oduction                                                     | 1                                                                                             |  |  |

| 1.1      | Problem Statement                                            | 2                                                                                             |  |  |

| 1.2      | Background                                                   | 3                                                                                             |  |  |

|          | 1.2.1 Computer Architecture                                  | 3                                                                                             |  |  |

|          | 1.2.2 Attacker Model                                         | 6                                                                                             |  |  |

| 1.3      | Outline                                                      | 7                                                                                             |  |  |

| 1.4      | Other Publications                                           | 9                                                                                             |  |  |

| 1.5      | Conclusion                                                   | 11                                                                                            |  |  |

|          | onten<br>st of<br>st of<br>Intro<br>1.1<br>1.2<br>1.3<br>1.4 | st of Abbreviations<br>st of Figures<br>st of Tables<br>Introduction<br>1.1 Problem Statement |  |  |

| 2 | Trus       | ted Co  | mputing Background                 | 13 |

|---|------------|---------|------------------------------------|----|

|   | 2.1        | Introd  | uction                             | 14 |

|   | 2.2        | Prelim  | inaries                            | 15 |

|   | 2.3        | Attack  | xer Model                          | 16 |

|   | 2.4        | Proper  | rties                              | 17 |

|   |            | 2.4.1   | Security Properties                | 17 |

|   |            | 2.4.2   | Architectural Features             | 19 |

|   | 2.5        | Archit  | ectures                            | 21 |

|   |            | 2.5.1   | AEGIS                              | 21 |

|   |            | 2.5.2   | Trusted Platform Module (TPM)      | 22 |

|   |            | 2.5.3   | TrustZone                          | 24 |

|   |            | 2.5.4   | Bastion                            | 27 |

|   |            | 2.5.5   | SMART                              | 28 |

|   |            | 2.5.6   | Sancus                             | 29 |

|   |            | 2.5.7   | SecureBlue++                       | 33 |

|   |            | 2.5.8   | Software Guard Extensions (SGX)    | 34 |

|   |            | 2.5.9   | Iso-X                              | 36 |

|   |            | 2.5.10  | TrustLite                          | 37 |

|   |            | 2.5.11  | TyTAN                              | 39 |

|   |            | 2.5.12  | Sanctum                            | 40 |

|   |            | 2.5.13  | TIMBER-V                           | 41 |

|   | 2.6        | Compa   | arison                             | 42 |

|   | 2.7        | Conclu  | asion                              | 46 |

| 3 | <b>C</b> : | de Cuel | a Implementations of Plack Cinkers | 47 |

| 3 | Sing       | -       | e Implementations of Block Ciphers | 47 |

|   | 3.1        |         | uction                             | 48 |

|   | 3.2        | Prelim  | ninaries                           | 49 |

| . 50                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                              |

| . 51                                                                                                                                                                                                         |

| . 51                                                                                                                                                                                                         |

| . 51                                                                                                                                                                                                         |

| . 53                                                                                                                                                                                                         |

| . 55                                                                                                                                                                                                         |

| . 56                                                                                                                                                                                                         |

| . 57                                                                                                                                                                                                         |

| . 58                                                                                                                                                                                                         |

| . 00                                                                                                                                                                                                         |

| . 59                                                                                                                                                                                                         |

|                                                                                                                                                                                                              |

| . 59                                                                                                                                                                                                         |

| . 59<br>. 60                                                                                                                                                                                                 |

| . 59<br>. 60<br>. 63                                                                                                                                                                                         |

| . 59<br>. 60<br>. 63<br><b>65</b>                                                                                                                                                                            |

| . 59<br>. 60<br>. 63<br><b>65</b><br>. 66                                                                                                                                                                    |

| . 59<br>. 60<br>. 63<br><b>65</b><br>. 66<br>. 67                                                                                                                                                            |

| . 59<br>. 60<br>. 63<br><b>65</b><br>. 66<br>. 67<br>. 67                                                                                                                                                    |

| . 59<br>. 60<br>. 63<br><b>65</b><br>. 66<br>. 67<br>. 67<br>. 68                                                                                                                                            |

| . 59<br>. 60<br>. 63<br><b>65</b><br>. 66<br>. 67<br>. 67<br>. 68<br>. 69                                                                                                                                    |

| . 59<br>. 60<br>. 63<br><b>65</b><br>. 66<br>. 67<br>. 67<br>. 68<br>. 69<br>. 70                                                                                                                            |

| <ul> <li>. 59</li> <li>. 60</li> <li>. 63</li> <li>65</li> <li>. 66</li> <li>. 67</li> <li>. 67</li> <li>. 68</li> <li>. 69</li> <li>. 70</li> <li>. 70</li> </ul>                                           |

| <ul> <li>. 59</li> <li>. 60</li> <li>. 63</li> <li>65</li> <li>. 66</li> <li>. 67</li> <li>. 67</li> <li>. 68</li> <li>. 69</li> <li>. 70</li> <li>. 70</li> <li>. 71</li> </ul>                             |

| <ul> <li>. 59</li> <li>. 60</li> <li>. 63</li> <li>65</li> <li>. 66</li> <li>. 67</li> <li>. 67</li> <li>. 67</li> <li>. 68</li> <li>. 69</li> <li>. 70</li> <li>. 70</li> <li>. 71</li> <li>. 72</li> </ul> |

|                                                                                                                                                                                                              |

\_\_\_\_\_ ix

|   | 6.1  | Contri  | butions                                | 117 |

|---|------|---------|----------------------------------------|-----|

| 6 | Con  | clusion |                                        | 117 |

|   | 5.4  | Conclu  | usion                                  | 116 |

|   |      | 5.3.3   | Evaluation                             | 114 |

|   |      | 5.3.2   | Implementation                         | 112 |

|   |      | 5.3.1   | Design                                 | 110 |

|   | 5.3  | Sancus  | s 2.0: Confidential Loading of Modules | 110 |

|   |      | 5.2.5   | Discussion                             | 108 |

|   |      | 5.2.4   | Related Work                           | 106 |

|   |      | 5.2.3   | Evaluation                             | 102 |

|   |      | 5.2.2   | Implementation                         | 97  |

|   |      | 5.2.1   | Architecture                           | 93  |

|   | 5.2  | Atlas:  | Transparent Memory Encryption          | 93  |

|   | 5.1  | Introd  | uction                                 | 92  |

| 5 | Hare | dware-E | Based Memory Protection Mechanisms     | 91  |

|   | 4.7  | Conclu  | usion                                  | 89  |

|   | 4.6  | Relate  | d Work                                 | 89  |

|   |      | 4.5.3   | Security                               | 86  |

|   |      | 4.5.2   | Area                                   | 86  |

|   |      | 4.5.1   | Performance                            | 84  |

|   | 4.5  | Evalua  | ation                                  | 84  |

|   |      | 4.4.5   | Key Derivation Mechanism               | 80  |

|   |      | 4.4.4   | Key Distribution Service               | 80  |

|   |      | 4.4.3   | Software Provider                      | 79  |

|   |      | 4.4.2   | Infrastructure Provider                | 78  |

| 6.2              | Future                 | e Work                    | 119 |  |

|------------------|------------------------|---------------------------|-----|--|

|                  | 6.2.1                  | Low-Latency Cryptography  | 119 |  |

|                  | 6.2.2                  | Capability Machines       | 119 |  |

|                  | 6.2.3                  | Control Flow Integrity    | 120 |  |

|                  | 6.2.4                  | Speculative Execution     | 121 |  |

|                  | 6.2.5                  | Hybrid CPU-FPGA Platforms | 122 |  |

| 6.3              | Concl                  | usion                     | 122 |  |

| Bibliog          | raphy                  |                           | 123 |  |

| Curriculum Vitae |                        |                           |     |  |

| List of          | List of Publications 1 |                           |     |  |

# S List of Abbreviations

| AE<br>AEAD<br>AES<br>AEX<br>AIK<br>ARC<br>ASIC<br>ASLR | Authenticated Encryption<br>Authenticated Encryption with Associated Data<br>Advanced Encryption Standard<br>Asynchronous Enclave Exit<br>Attestation Identity Key<br>Address Range Comparator<br>Application-Specific Integrated Circuit<br>Address Space Layout Randomization |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA                                                     | Certificate Authority                                                                                                                                                                                                                                                           |

| CAN                                                    | Controller Area Network                                                                                                                                                                                                                                                         |

| CFA                                                    | Control Flow Attestation                                                                                                                                                                                                                                                        |

| CFG                                                    | Control Flow Graph                                                                                                                                                                                                                                                              |

| CFI                                                    | Control Flow Integrity                                                                                                                                                                                                                                                          |

| СМР                                                    | Compartment Metadata Page                                                                                                                                                                                                                                                       |

| СМУ                                                    | Physical Page Compartment Membership Vector                                                                                                                                                                                                                                     |

| CPSR                                                   | Current Program Status Register                                                                                                                                                                                                                                                 |

| СРТ                                                    | Compartment Page Table                                                                                                                                                                                                                                                          |

| CPU                                                    | Central Processing Unit                                                                                                                                                                                                                                                         |

| CRL                                                    | Certificate Revocation List                                                                                                                                                                                                                                                     |

| СТ                                                     | Compartment Table                                                                                                                                                                                                                                                               |

| DDoS                                                   | Distributed DoS                                                                                                                                                                                                                                                                 |

| DEP                                                    | Data Execution Prevention                                                                                                                                                                                                                                                       |

| DMA                                                    | Direct Memory Access                                                                                                                                                                                                                                                            |

| DoS                                                    | Denial-of-Service                                                                                                                                                                                                                                                               |

| DPA                                                    | Differential Power Analysis                                                                                                                                                                                                                                                     |

| DRAM                                                   | Dynamic Random-Access Memory                                                                                                                                                                                                                                                    |

| DRoT                                                   | Dynamic RoT                                                                                                                                                                                                                                                                     |

**EA-MPU** Execution-Aware MPU

| ECB  | Enclave Control Block                                 |

|------|-------------------------------------------------------|

| ECC  | Elliptic Curve Cryptography                           |

| EID  | Enclave Identity                                      |

| EK   | Endorsement Key                                       |

| ELF  | Executable and Linkable Format                        |

| EM   | Execution Monitor                                     |

| EPC  | Enclave Page Cache                                    |

| EPCM | Enclave Page Cache Map                                |

| EPID | Enhanced Privacy Identifier                           |

| ETB  | Embedded Trace Buffer                                 |

| EtM  | Encrypt-then-MAC                                      |

| FPGA | Field Programmable Gate Array                         |

| GPU  | Graphics Processing Unit                              |

| HKDF | HMAC-based Extract-and-Expand Key Derivation Function |

| HMAC | Keyed-Hash Message Authentication Code                |

| HSM  | Hardware Security Module                              |

| I/O  | Input/Output                                          |

| IC   | Integrated Circuit                                    |

| IDE  | Integrated Development Environment                    |

| IDT  | Interrupt Descriptor Table                            |

| IoT  | Internet of Things                                    |

| IP   | Infrastructure Provider                               |

| IPC  | Inter-Process Communication                           |

| ISA  | Instruction Set Architecture                          |

| ISR  | Interrupt Service Routine                             |

| IU   | Integer Unit                                          |

| IV   | Initialization Vector                                 |

| KDF  | Key Derivation Function                               |

| KDM  | Key Derivation Mechanism                              |

| KDS  | Key Distribution Service                              |

| LFSR | Linear Feedback Shift Register                        |

| LLC  | Last-Level Cache                                      |

| LPC  | Low Pin Count                                         |

| LRU  | Least Recently Used                                   |

| LSB  | Least Significant Bit                                 |

| LUT  | Look-Up Table                                         |

| MAC                                                                                                    | Message Authentication Code                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAL                                                                                                    | Memory Access Logic                                                                                                                                                                                                                                                                                                                                                                                               |

| MCU                                                                                                    | Memory Control Unit                                                                                                                                                                                                                                                                                                                                                                                               |

| MEE                                                                                                    | Memory Encryption Engine                                                                                                                                                                                                                                                                                                                                                                                          |

| MitM                                                                                                   | Man-in-the-Middle                                                                                                                                                                                                                                                                                                                                                                                                 |

| MMIO                                                                                                   | Memory-Mapped IO                                                                                                                                                                                                                                                                                                                                                                                                  |

| MMU                                                                                                    | Memory Management Unit                                                                                                                                                                                                                                                                                                                                                                                            |

| MPU                                                                                                    | Memory Protection Unit                                                                                                                                                                                                                                                                                                                                                                                            |

| MRID                                                                                                   | Memory Region ID                                                                                                                                                                                                                                                                                                                                                                                                  |

| NoC                                                                                                    | Network-on-Chip                                                                                                                                                                                                                                                                                                                                                                                                   |

| NS                                                                                                     | Non-Secure                                                                                                                                                                                                                                                                                                                                                                                                        |

| OS                                                                                                     | Operating System                                                                                                                                                                                                                                                                                                                                                                                                  |

| PAR<br>PC<br>PCR<br>PL<br>PLC<br>PMA<br>PMR<br>PRM<br>PRNG<br>PROM<br>PS<br>PTBR<br>PTBR<br>PTM<br>PTR | Place and Route<br>Program Counter<br>Platform Configuration Register<br>Programmable Logic<br>Programmable Logic Controller<br>Protected Module Architecture<br>Protected Memory Region<br>Processor Reserved Memory<br>Pseudo-Random Number Generator<br>Programmable ROM<br>Processing System<br>Page Table Base Register<br>Program Trace Macrocell<br>Private and Authenticated Tamper-Resistant Environment |

| REE                                                                                                    | Rich Execution Environment                                                                                                                                                                                                                                                                                                                                                                                        |

| RNG                                                                                                    | Random Number Generator                                                                                                                                                                                                                                                                                                                                                                                           |

| ROM                                                                                                    | Read-Only Memory                                                                                                                                                                                                                                                                                                                                                                                                  |

| ROP                                                                                                    | Return-Oriented Programming                                                                                                                                                                                                                                                                                                                                                                                       |

| RoT                                                                                                    | Root of Trust                                                                                                                                                                                                                                                                                                                                                                                                     |

| RTM                                                                                                    | RoT for Measurement                                                                                                                                                                                                                                                                                                                                                                                               |

| RWP                                                                                                    | RAM Write Pointer                                                                                                                                                                                                                                                                                                                                                                                                 |

| SE                                                                                                     | Secure Executable                                                                                                                                                                                                                                                                                                                                                                                                 |

| SEID                                                                                                   | Secure Executable ID                                                                                                                                                                                                                                                                                                                                                                                              |

| SEM                                                                                                    | Security Enforcement Module                                                                                                                                                                                                                                                                                                                                                                                       |

| SEV                                                                                                    | Secure Encrypted Virtualization                                                                                                                                                                                                                                                                                                                                                                                   |

| SGX                                                                                                    | Software Guard Extensions                                                                                                                                                                                                                                                                                                                                                                                         |

| SK     | Security Kernel               |

|--------|-------------------------------|

| SM     | Software Module               |

| SME    | Secure Memory Encryption      |

| SoC    | System-on-Chip                |

| SP     | Software Provider             |

| SPID   | Secure Process ID             |

| SPM    | Scratchpad Memory             |

| SSBL   | Second Stage Boot Loader      |

| TCB    | Trusted Computing Base        |

| TCC    | Trusted Computing Group       |

| TCP    | Transmission Control Protocol |

| TE     | Tamper-Evident Environment    |

| TEE    | Trusted Execution Environment |

| TLB    | Translation Lookaside Buffer  |

| TOCTOU | Time-of-Check Time-of-Use     |

| TP     | Trusted Partition             |

| TPM    | Trusted Platform Module       |

| TRNG   | True Random Number Generator  |

| TXT    | Trusted Execution Technology  |

| UDP    | User Datagram Protocol        |

| UP     | Untrusted Partition           |

| VPN    | Virtual Private Network       |

| WSN    | Wireless Sensor Network       |

# **§** List of Figures

| 1.1 | Memory Hierarchy                            | 4  |

|-----|---------------------------------------------|----|

| 1.2 | Protection Rings                            | 5  |

| 2.1 | Protected Module Architecture               | 17 |

| 2.2 | TrustZone                                   | 25 |

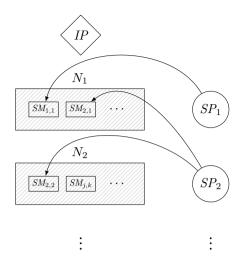

| 2.3 | System Model for Sancus                     | 30 |

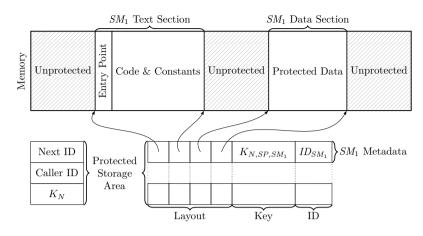

| 2.4 | Sancus Node                                 | 32 |

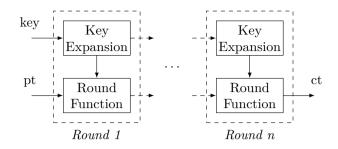

| 3.1 | Structure of Unrolled Block Ciphers         | 50 |

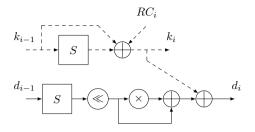

| 3.2 | Critical Path of an AES Round               | 53 |

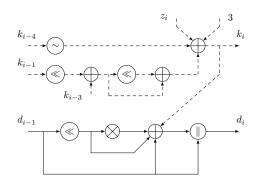

| 3.3 | Critical Path of a KATAN Round              | 54 |

| 3.4 | Critical Path of a PRESENT Round            | 55 |

| 3.5 | Critical Path of a PRINCE Round             | 57 |

| 3.6 | Critical Path of a RECTANGLE Round          | 58 |

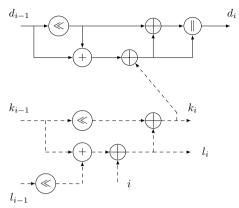

| 3.7 | Critical Path of a SIMON Round              | 59 |

| 3.8 | Critical Path of a SPECK Round              | 60 |

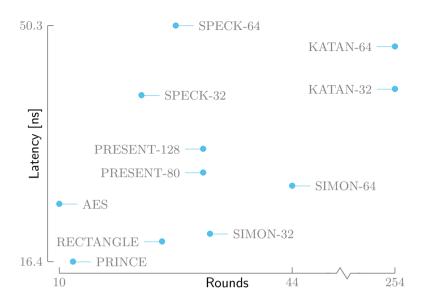

| 3.9 | Comparison of Critical Path Latency on FPGA | 63 |

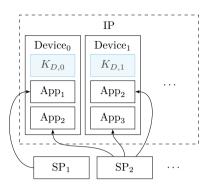

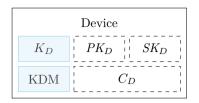

| 4.1 | System Model for Eleutheria                 | 69 |

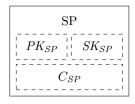

| 4.2 | Parties and Components in Eleutheria        | 70 |

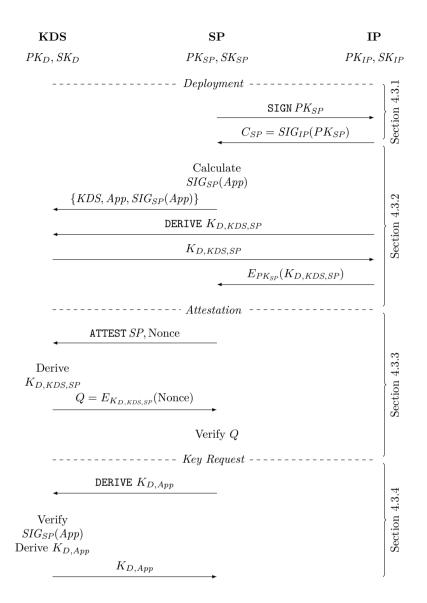

| 4.3  | Infrastructure Provider                               |

|------|-------------------------------------------------------|

| 4.4  | Software Provider                                     |

| 4.5  | Key Distribution Service                              |

| 4.6  | Deployment, Attestation, and Key Request Interactions |

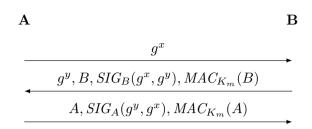

| 4.7  | SIGMA Protocol                                        |

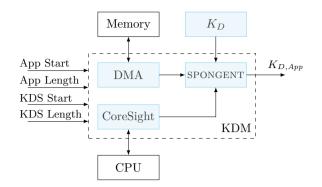

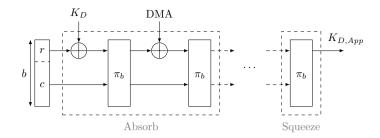

| 4.8  | Key Derivation Mechanism                              |

| 4.9  | Key Derivation Function                               |

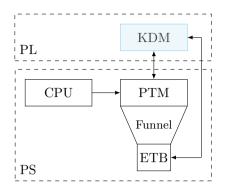

| 4.10 | CoreSight Components                                  |

|      |                                                       |

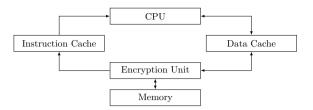

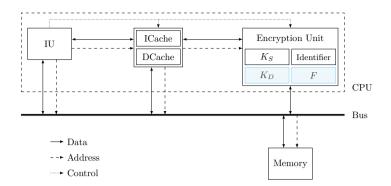

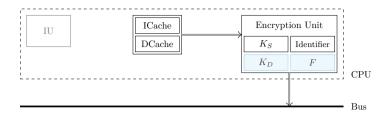

| 5.1  | Code and Data Flow in Atlas                           |

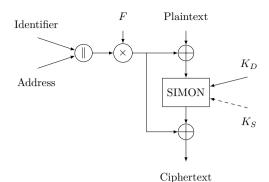

| 5.2  | Encryption Unit                                       |

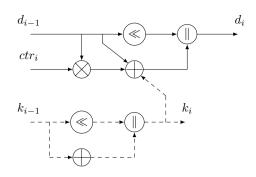

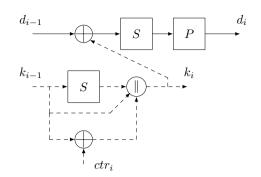

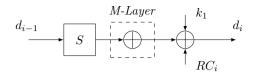

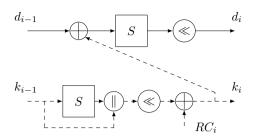

| 5.3  | LRW Mode of Operation                                 |

| 5.4  | Critical Path of Atlas 103                            |

# S List of Tables

| 2.1 | Comparison of Trusted Computing Architectures  | 43  |

|-----|------------------------------------------------|-----|

| 3.1 | Properties of Implemented Algorithms           | 52  |

| 3.2 | Block Cipher Synthesis Results on FPGA         | 62  |

| 3.3 | Block Cipher Synthesis Results on ASIC         | 62  |

| 4.1 | Performance of Local and Remote Key Requests   | 85  |

| 4.2 | Area Utilization of Eleutheria on FPGA         | 86  |

| 5.1 | Area Utilization of Atlas on FPGA              | 105 |

| 5.2 | Memory Access Rights                           | 111 |

| 5.3 | Performance Comparison of Confidential Loading | 115 |

## Introduction

1

S ECURITY and privacy increasingly gain importance as electronic devices become more present in our daily lives. Attackers are always looking for ways to exploit the software running on these devices in an attempt to obtain sensitive information. All of our devices are also more and more networked, with remote access growing the opportunity for attack considerably. This might seem innocuous when it is just about fridges sending spam, but can have significant ramifications when critical infrastructure is breached.

Discovered in 2010, Stuxnet is perhaps one of the most well-known worms, as it was responsible for disrupting Iran's nuclear program [1]. It contained a sophisticated payload for a specific Siemens Programmable Logic Controller (PLC) series, which were installed in a uranium enrichment facility and controlled centrifuges. The attackers reprogrammed the PLCs in such a way that they would vary the frequency of these centrifuges, driving down the yield of this process. However, the malware would still report that everything was operating as intended, hiding its manipulation and confusing the plant's engineers.

More recently, a power grid operator in Ukraine was locked out of his computer and saw his mouse move across the screen, flipping high-voltage breakers in local substations [2]. The attackers also compromised two other distribution centres, cutting power to several regions of the country. They even went as far as to disable the backup power supplies for the control centres themselves, leaving their operators in the dark.

Finally, the global operations of shipping giant Maersk ground to a halt as ransomware spread through the company's systems, encrypting their hard drives [3]. With the global network offline, no new cargo could be accepted or released at any of Maersk's shipping terminals. It took the company several days to restore basic functionality and employees could only resume work after two weeks. NotPeya, as the malware was called, affected several other multinational companies as well, causing an estimated ten billion dollar in damages. In each of these attacks, electronic devices were manipulated to make them deviate from their normal, intended behaviour. This brings us to the subject of trusted computing, which ensures that a device can be trusted if it cannot be made to misbehave. Given the complexity of today's software and the growing sophistication of the attacks perpetrated against it, this is not straightforward to attain. Therefore, trusted computing solutions build on Roots of Trust (RoTs), inherently trusted components that enable this trust relationship. This thesis evaluates the cryptographic primitives that are at their core, introduces novel solutions that enable the use of these strong ciphers, and proposes protection mechanisms that build on them.

### 1.1 Problem Statement

Attackers commonly target memory vulnerabilities to exploit software, abusing this weakness to access its code or leak its secrets. The former are referred to as code-reuse attacks, where execution is redirected to realise malicious functionality without adding new code. These vulnerabilities can have farreaching effects, giving attackers a foothold onto the device, that could be combined with other attack vectors and leveraged to gain privileged access or compromise secrets. In both cases, the adversary manages to make the program behave in ways that were not intended by its developers, either through the introduction of new behaviour or by leaking sensitive information.

Modern embedded and mobile devices no longer consist of discrete Integrated Circuits (ICs), but are instead built around a System-on-Chip (SoC). This single chip combines a processor with additional on-chip blocks, such as a Graphics Processing Unit (GPU), and peripheral connectivity in a single package, reducing the area and power requirements. Its tight integration has also influenced the hardware design process, as blocks from external vendors can now be combined with custom hardware in the same package. This has simplified introducing new hardware features, as all components are typically connected to a single system bus, through which they can be accessed by software or communicate with each other.

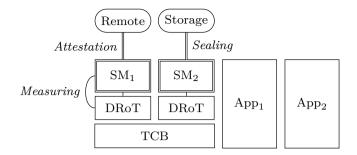

Today's programs are complex, often comprising hundreds of thousands or even millions of lines of code, which has made it increasingly difficult to guarantee that they are free of exploitable bugs. This observation was first made by McCune et al. in 2008 [4], leading to the concept of Protected Module Architectures (PMAs). They proposed to extract a program's critical functionality, such as implementations of cryptographic algorithms and protocols. These smaller modules are much more contained and can even be proven to be free of bugs.

2

Furthermore, isolation can protect these modules from other software running on the system, exposing only their public interface. Finally, PMAs also make it possible for third parties to obtain proof that the module's code was not tampered with through attestation.

These isolation and attestation mechanisms form the foundation of trusted computing, which guarantee that software cannot be made to misbehave. However, they require functionality offered by RoTs, which are inherently trusted components that validate the trust assessment. If any of them were to be compromised, the security of the system can no longer be guaranteed. RoTs can be implemented in hardware and software, but the former is more common, because the intrinsic immutability of hardware implies that their functionality cannot be tampered with. While they are essential to trusted computing architectures, RoTs themselves are also made up of multiple building blocks. We first consider these cornerstones of trusted computing, before moving up through the design hierarchy and introducing architectural security features, building on novel RoTs.

### 1.2 Background

Having outlined the motivation for designing trusted computing architectures in the previous section, we will now introduce related concepts that will return throughout this thesis. First, Section 1.2.1 discusses fundamental notions from computer architecture, such as the memory hierarchy and protection rings. Second, security solutions always make assumptions about the capabilities of the attacker they protect against, which we describe for trusted computing architectures in Section 1.2.2.

#### 1.2.1 Computer Architecture

Hennesy and Patterson note that the design of modern electronic devices has become incredibly complex, making it hard to exactly define the term computer architecture [5]. Therefore, an architect has to determine the computer's important attributes and realise a fast and energy-efficient design subject to cost, power, and availability constraints. Trusted computing mechanisms have been designed for a wide range of architectures, from lightweight microcontrollers to high-end multi-core processors. Consequently, each of our solutions will outline its required architectural features, and the following presents several foundational concepts that are relevant to this thesis.

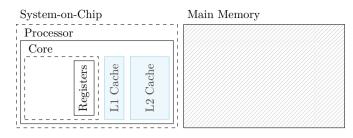

Figure 1.1: The inverse relationship between memory capacity and response times has resulted in a complex memory hierarchy, giving the processor access to a large storage area, seemingly at the latency of its internal registers.

Today's devices not only consist of hardware, but also feature system software, which is an important part of their design and integral to their operation. We therefore consider a system to comprise both the hardware and this basic software layer. Returning to the description of an SoC (Section 1.1), the hardware includes the processor, any on-chip components supporting the Central Processing Unit (CPU), and the communication bus interconnecting all of these components. Since main memory is not part of the SoC, the system boundary is found at the interface to external peripherals. Due to the heterogeneity of the platforms discussed in this thesis, we define the system software as any code that is not part of an application.

A fundamental computer architecture concept is the memory hierarchy, which is crucial to meet the performance requirements and power constraints of modern processors (Figure 1.1). Registers are the fastest type of memory and sit closest to the core's computing units, but they are also expensive in terms of area and power. Computers therefore rely on a large main memory, which is external to the CPU and connected to the system bus. However, since its response is much slower than that of the internal registers, CPUs also have one or more levels of cache. These introduce smaller and faster internal storage, which retain recently-accessed code and data. As registers, caches, and main memory are all volatile, most devices also include persistent storage (e.g., flash).

While the previous discussion focused on the main memory, it generally does not require all available addresses, especially not on 64-bit systems. Other resources, like peripherals, can therefore also be assigned a segment through which they are exposed to software. However, developers need to be aware of what resource is mapped where, as their accesses could pass through the cache, requiring manual flushing or marking these regions as non-cacheable, if supported. Finally, some architectures feature fast on-chip Scratchpad Memory (SPM) rather than caches, which is directly accessible from software instead.

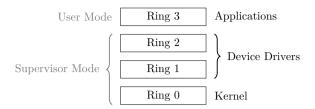

Figure 1.2: Processors have different privilege levels at which software can run, with associated capabilities. System software runs with more rights in supervisor mode, while applications are more restricted in user mode.

Rather than allowing software to access memory and peripherals through their physical addresses, computer architectures often rely on virtual addresses. Here, each application runs within its own virtual address space, isolating it from all other processes running on the system. When a virtual address is accessed, a Memory Management Unit (MMU) inside the processor will translate it to the corresponding physical one. This MMU is configured by the system software, which can typically also set the different access rights for ranges of memory. In contrast to the applications it manages, the system software therefore does have direct access to the physical address space.

As evidenced by the operation of an MMU, processors need some way to limit what software can or cannot do. To this end, most architectures implement protection rings or privilege levels, which allow the processor to control what operations are available. The number of levels and terminology varies across architectures (Figure 1.2), but CPUs generally offer at least a supervisor mode for system software and user mode for applications. Intel processors feature four rings, with the lower rings being the more privileged ones. The system software therefore runs in rings zero to two and applications are assigned to ring three [6]. In contrast, Arm cores only have two exception levels separating the system software from applications, respectively denoted by EL1 and EL0 [7].

Upon reset of the processor, a chain of software components is executed before the applications become active, initializing the system and its peripherals. Especially on more complex systems, it is common to have multiple of these socalled boot loaders, with the later stages including richer and richer functionality. This approach ensures that the boot process remains flexible, as the initial stage has to be stored in Read-Only Memory (ROM). The final boot loader will start the system software, which is in turn responsible for managing the applications. Trusted computing architectures make trust assessments about the state of these components, which is defined as their code and static data. This definition results from the requirement that this assessment should be verifiable, and can therefore only include elements that are known to the verifier.

#### 1.2.2 Attacker Model

When building security mechanisms, designers always make some assumptions about the attacker's capabilities, and their solution will only be secure as long as the adversary stays within this model. In case of trusted computing architectures, these follow from considering an attacker targeting applications running on a remote system that he might have physical access to or even manage. Since he has full control over the system's configuration and the software running there, trusted computing mechanisms therefore need to be based on trusted hardware, which is significantly harder to tamper with than code. Furthermore, having physical access to the device means that he could directly connect to main memory and the bus interface that exposes it. Finally, this also gives him the possibility to manipulate the device's network channel.

All architectures discussed in this thesis include an attacker model in their description that follows from these considerations. While each design might introduce additional assertions to cover specific design decisions or account for the protection mechanisms it introduces, the attacker models of trusted computing solutions have several elements in common, which we will now list.

- 1. The attacker has access to all untrusted code, including large parts of the system software. This is therefore a very privileged attacker who can break traditional security assumptions (e.g., he can control the virtual address map). He can also manipulate existing code or introduce new software to the system.

- 2. It is assumed that the attacker controls the device's network channels, and can therefore intercept and modify messages. While he is generally considered to have the ability to tamper with the security protocols securing this channel, the adversary does follow the Dolev-Yao model [8]. This model states that the cryptographic primitives used in these protocols, such as the encryption algorithms or hash functions, cannot be broken by the attacker.

- 3. Denial-of-Service (DoS) attacks, which compromise device availability, are also not considered. In fact, many trusted computing solutions even introduce DoS vectors, as the processor will respond to security violations and take action against the offending software, e.g., by resetting the device. Additionally, these attacks are also out of scope at the network level.

- 4. We also exclude physical attacks on the device from the model. The adversary therefore cannot access or tamper with the device's internal signals. Furthermore, this assumption also implies that he cannot read or write data on the system bus directly or to main memory.

Finally, the attacker is also assumed not to mount any side-channel attacks, neither in hardware nor software. This class of attacks observes implementation-specific metadata and uses it to infer confidential information, that would otherwise have been protected. For example, if the secret were to determine whether an expensive operation is performed or not, the attacker could measure execution time or monitor the power drawn by the device to determine if it was active, recovering the secret bit by bit [9]. At the hardware level, physical effects are measured, such as power usage [10] or electromagnetic radiation [11], while a software-based attacker observes effects of code execution, like memory access latency [12].

Recently, microarchitectural attacks have been introduced, which exploit fundamental design flaws of the computer architecture from software [13–16]. Both hardware and software implementations can be protected from these types of attacks through various countermeasures, but microarchitectural vulnerabilities require particular attention, as they should be taken into account during the architecture's design process. We therefore view side-channel attacks as orthogonal to the issues addressed by trusted computing, as their respective protection mechanisms are generally composable.

Given this attacker model, we can now also identify the extent of the system's trust boundary, which encloses all components that are security-critical, as they will have direct access to sensitive data. In addition to any trusted hardware introduced by the specific architecture, the core processor functionality, its registers, and the cache hierarchy are typically included. In contrast to the system boundary defined earlier, the main memory and system bus are also within this boundary, unless there is a mechanism protecting the bus transactions and memory contents.

### 1.3 Outline

This thesis presents different contributions that we made to the field of lightweight trusted computing. Our work covers the design spectrum of hardware-based trusted computing architectures, from basic cryptographic building blocks (Chapters 3 and 4) to novel architectural protection mechanisms (Chapter 5). We now give a short overview of each chapter, sketching the structure of this text.

**Chapter 1 – Introduction** We first describe typical attack vectors that are used to exploit applications, before considering the hardware-based protection mechanisms that can protect against them. Next, an outline of this thesis

is presented and summaries of our publications that are not included in full conclude this chapter.

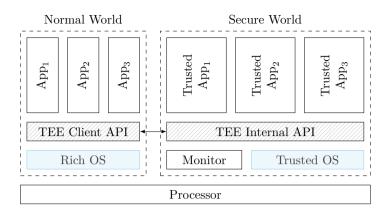

**Chapter 2 – Trusted Computing Background** For the past decade, both academia and industry have actively contributed to the field of trusted computing. In this chapter, we define the terminology that is used to describe these architectures, identify a shared attacker model, and introduce the security properties offered by them. Furthermore, we summarise thirteen existing hardware-based architectures, that offer either or both isolation and attestation mechanisms. Finally, the considered architectures are compared with respect to the considered security properties as well as traditional architectural features.

**Chapter 3 – Single-Cycle Implementations of Block Ciphers** Cryptographic primitives form a core building block of trusted computing architectures. Symmetric ciphers are particularly important for the design and implementation of lightweight architectures, as these algorithms can be implemented more efficiently in hardware. We built hardware implementations of six lightweight block ciphers and AES, in order to evaluate their latency and area requirements. Most block ciphers have an iterated design and we fully unrolled their internal structure to analyse single-cycle performance.

**Chapter 4 – Eleutheria: Lightweight Key Distribution Service** Part of the design complexity when using symmetric cryptographic algorithms arises from the fact that all communicating parties require access to a shared secret. This key distribution problem is typically solved by running a protocol based on asymmetric primitives first, which require significant hardware resources.

In this chapter, we present a key distribution mechanism which is rooted in hardware and relies on a network service implemented in software, securing the communication through asymmetric algorithms. Application-specific keys can be requested remotely and are derived in hardware from a unique device key, which is never extracted from the device or exposed to software.

**Chapter 5 – Hardware-Based Memory Protection Mechanisms** Applications often implement specific algorithms, which are valuable intellectual property, or process sensitive data. This information should therefore be secure from attackers, preventing them from obtaining the application's binary or retrieving its input and output. To this end, we present two architectural extensions that introduce hardwarebased mechanisms protecting either or both code and data in untrusted main memory. First, Atlas introduces an encryption unit in the memory hierarchy that transparently decrypts or encrypts any code or data that is read or written, including the application's identity in the encryption context, so that no code or data leaks to other software. Furthermore, the choice of cipher was driven by the observations from Chapter 3, as the memory access latency impacts system performances. Second, we designed an extension for Sancus enabling confidential loading of modules. This additional functionality required little extra hardware, as Sancus already implemented a flexible cryptographic primitive.

**Chapter 6 – Conclusion** We close this thesis with an overview of the presented solutions, highlighting their contributions, but also considering their limitations. Since our work focused on specific cryptographic primitives and trusted computing features, we also discuss possible avenues for future research.

### 1.4 Other Publications

Aside from the work discussed in this thesis, we also co-authored other publications. These papers are listed here in reverse chronological order, unless there were multiple papers on the same topic. A summary of their contributions is also included.

In Soteria: Offline Software Protection within Low-cost Embedded Devices [17], we extend Sancus with a software-based solution to protect code confidentiality. Application binaries are decrypted by a special loader module, whose identity is included in the derivation of the encryption key. Since Sancus defines the identity of a module as the combination of its memory layout and code, any modifications to the loader module will result in the derivation of an incorrect key and decryption will consequently fail. After the module has been loaded and its plaintext code is stored in memory, Soteria relies on Sancus' hardware-based isolation mechanism to ensure that it does not leak.

J. Götzfried, T. Müller, R. de Clercq, P. Maene, F. Freiling and I. Verbauwhede, "Soteria: Offline Software Protection within Low-cost Embedded Devices", in *Proceedings of the 31st Conference on Computer Security Applications*, 2015

SOFIA: Software and Control Flow Integrity Architecture [18, 19] is an architecture offering a strong Control Flow Integrity (CFI) mechanism. Control

flow attacks manipulate the original execution order of an application in an attempt to run arbitrary code. SOFIA's protection mechanism is two-fold. First, it encrypts the application's binary in such a way that it is bound to its control flow, preventing code injection and reuse attacks. Second, it introduces an integrity mechanism that dynamically calculates a Message Authentication Code (MAC) in the processor's pipeline and prevents execution from continuing if verification fails.

R. de Clercq, R. De Keulenaer, B. Coppens, B. Yang, K. De Bosschere, B. De Sutter, P. Maene, B. Preneel and I. Verbauwhede, "SOFIA: Software and Control Flow Integrity Architecture", in *Proceedings of the 19th Conference on Design, Automation and Test*, 2016

R. de Clercq, J. Götzfried, P. Maene, D. Übler and I. Verbauwhede, "SOFIA: Software and Control Flow Integrity Architecture", *Computers & Security*, vol. 68, no. 7, 2017

In Hardware Acceleration of a Software-Based VPN [20], we present an accelerator to improve the performance of Virtual Private Network (VPN) applications, which provide an encrypted network tunnel. Specifically, our architecture includes efficient hardware implementations of the Salsa20 stream cipher and Poly1305 MAC function. These hardware blocks were tightly integrated with SigmaVPN, a lightweight VPN application that runs on Linux. Our co-design for the Xilinx Zynq-7010 FPGA improves TCP and UDP bandwidth by a factor of 4.36 and 5.36 respectively.

F. Turan, R. de Clercq, P. Maene, O. Reparaz and I. Verbauwhede, "Hardware Acceleration of a Software-Based VPN", in *Proceedings of the* 26th Conference on Field Programmable Logic and Applications, 2016

SOFIA's strong guarantees stem from tight integration with a processor's pipeline. However, modern SoC design typically integrates third-party building blocks, so-called IP cores. In order to facilitate more straightforward adoption of the concepts developed by SOFIA, but with weaker security guarantees, we designed *SCM: Secure Code Memory Architecture* [21]. In this paper, we present an IP core that connects to the SoC's main memory bus and aliases part of the system's main memory. When the processor is executing from this aliased range, the introduced hardware block will decrypt the code that is being read and verify MACs that are interleaved with it. If this integrity verification fails, the processor will be reset.

R. de Clercq, R. De Keulenaer, P. Maene, B. De Sutter, B. Preneel and I. Verbauwhede, "SCM: Secure Code Memory Architecture", in *Proceedings* of the 12th Conference on Computer and Communications Security, 2017

Finally, we present a device tracking system based on Internet of Things (IoT) technology in A Privacy-Preserving Device Tracking System Using a Low-Power Wide-Area Network (LPWAN) [22]. Our design relies on the presence of Bluetooth beacons, which continuously broadcast a unique identifier. Our tracker will periodically scan for these broadcasts and store them in a local buffer. At fixed intervals, this buffer will be encrypted and uploaded to a server through LoRa, which is a low-power networking technology. This server also hosts a list with the geographical coordinates of every beacon. The tracker's owner can link his device to a mobile application, which downloads and decrypts the messages from the server. Finally, the tracker's location history is displayed by combining the identifiers from the decrypted messages with the geographical coordinates of the beacons.

T. Ashur, J. Delvaux, S. Lee, P. Maene, E. Marin, S. Nikova, O. Reparaz, V. Rožić, D. Singelée, B. Yang and B. Preneel, "A Privacy-Preserving Device Tracking System Using a Low-Power Wide-Area Network (LPWAN)", in *Proceedings of the 16th Conference on Cryptology and Network Security*, 2017

### 1.5 Conclusion

Recent attacks have clearly shown the consequences of exploitable software vulnerabilities on personal devices as well as the systems of large companies and even critical utilities infrastructure. When applications are exploited, they act in ways that the user does not expect nor as intended by the developer. The goal of trusted computing is to address exactly this behaviour, by guaranteeing that software cannot be made to misbehave.

The remainder of this thesis will focus on hardware-based trusted computing, but any changes to the architecture also require modifications to the software it executes. We will first provide more extensive background on trusted computing, defining terminology and surveying existing hardware-based architectures for isolation and attestation. We then discuss the design and implementation of such architectures, starting at the bottom of their design hierarchy by analysing the performance of block ciphers and designing a novel key distribution mechanism. Finally, we close this thesis by introducing two architectural solutions protecting the confidentiality of code and data.

## **Trusted Computing Background**