IEEE JOURNAL OF PHOTOVOLTAICS

# Dry Passivation Process for Silicon Heterojunction Solar Cells Using Hydrogen Plasma Treatment Followed by *In Situ* a-Si:H Deposition

Menglei Xu , Chong Wang, Twan Bearda, Eddy Simoen, Hariharsudan Sivaramakrishnan Radhakrishnan, Ivan Gordon, Wei Li, Jozef Szlufcik, and Jef Poortmans

Abstract—A fully dry and hydrofluoric-free low-temperature process has been developed to passivate n-type crystalline silicon (c-Si) surfaces. Particularly, the use of a hydrogen (H<sub>2</sub>) plasma treatment followed by in situ intrinsic hydrogenated amorphous silicon (a-Si:H) deposition has been investigated. The impact of H<sub>2</sub> gas flow rate and H<sub>2</sub> plasma processing time on the a-Si:H/c-Si interface passivation quality is studied. Optimal H<sub>2</sub> plasma processing conditions result in the best effective minority carrier lifetime of up to 2.5 ms at an injection level of  $1 \times 10^{15}$  cm<sup>-3</sup>, equivalent to the best effective surface recombination velocity of 4 cm/s. The reasons that enable such superior passivation quality are discussed in this paper based on the characterization of the a-Si:H/c-Si interface and c-Si substrate using transmission electron microscopy, high angle annular dark field scanning transmission electron microscopy, and deep-level transient spectroscopy.

Index Terms—Hydrogenated amorphous silicon (a-Si:H), hydrogen  $(H_2)$  plasma, passivation, silicon heterojunction (SHJ) solar cells.

## I. INTRODUCTION

SILICON heterojunction (SHJ) solar cells are the subject of strong industrial interest because of their simple device structure and capacity to achieve a very high energy conversion efficiency. A high open-circuit voltage of up to 750 mV has been demonstrated by Panasonic in an SHJ cell [1]. In early 2017, a world record efficiency of 26.7% was reported by Kaneka using

Manuscript received June 12, 2018; revised August 3, 2018 and September 13, 2018; accepted September 15, 2018. This work was supported in part by the Imec's industrial affiliation program for Si-PV and in part by the China Scholarship Council. (Menglei Xu and Chong Wang contributed equally to this work.) (Corresponding author: Menglei Xu.)

- M. Xu is with the Katholieke Universiteit Leuven, Leuven 3001, Belgium, and also with Imec, Leuven 3001, Belgium (e-mail: menglei.xu@imec.be).

- C. Wang and W. Li are with the School of Optoelectronic Information, University of Electronic Science and Technology of China, Chengdu 610054, China (e-mail: weberchong@gmail.com; wli@uestc.edu.cn).

- T. Bearda was with Imec, Leuven 3001, Belgium. He is now with ENTRAS, Mechelen 2800, Belgium (e-mail: twan.bearda@gmail.com).

- E. Simoen is with Imec, Leuven 3001, Belgium, and also with Ghent University, Gent 9000, Belgium (e-mail: eddy.simoen@imec.be).

- H. S. Radhakrishnan, I. Gordon, and J. Szlufcik are with Imec, Leuven 3001, Belgium (e-mail: sivarama@imec.be; ivan.gordon@imec.be; jozef. szlufcik@imec.be).

- J. Poortmans is with Imec, Leuven 3001, Belgium, with the Katholieke Universiteit Leuven, Leuven 3001, Belgium, and also with Hasselt University, Hasselt 3500, Belgium (e-mail: jef.poortmans@imec.be).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JPHOTOV.2018.2871329

a back-contact SHJ solar cell [2]. To achieve such impressive results, an excellent crystalline silicon (c-Si) surface passivation is required to minimize recombination at surface defects. This can be accomplished by combining a careful precleaning of the c-Si surface and an optimal hydrogenated amorphous silicon (a-Si:H) layer deposition [3]–[5]. It is commonly accepted that a wet-chemical cleaning followed by a hydrofluoric (HF) acid dip should be performed before a-Si:H deposition to remove the native silicon oxide and obtain a hydrogen-terminated c-Si surface [6], [7]. Although this process can meet the cleaning demands at the laboratory scale, using HF acid at the industrial scale can lead to economic and ecological issues due to the hazardous nature of HF. As an alternative to HF, an hydrogen (H<sub>2</sub>) plasma treatment is very promising due to the following three aspects.

- 1) It is an HF-free method to etch the silicon oxide layer on the c-Si surface [8]–[11].

- 2) It is an *in situ* process due to its capacity to carry out the H<sub>2</sub> plasma treatment and subsequent a-Si:H deposition in the same plasma reactor without breaking the vacuum.

- 3) It allows for thin wafer processing to reduce industrial production cost because no handling issues occur during the *in situ* passivation process [12].

Nevertheless, integration of such dry passivation processes into SHJ solar cell fabrication is still challenging because of the difficulty to remove the silicon oxide layer effectively while limiting the H<sub>2</sub> plasma induced damage to the c-Si surface. Up to now, several research groups have worked on this process in an either capacitively [13], [14] or inductively coupled radio-frequency plasma-enhanced chemical vapor deposition (RF-PECVD) reactor [15], [16]. Moreno et al. reported a two-step etching process (420 s) using precursor mixtures of silicon tetrafluoride and H<sub>2</sub> to replace the HF dip prior to a-Si:H deposition [14]. In comparison, Tang et al. demonstrated a rapid H<sub>2</sub> plasma etching process (20 s) and achieved comparable effective minority carrier lifetimes ( $\tau_{\rm eff}$ ) after thermal annealing of a-Si:H layer with respect to a conventional HF dip [15], [16]. However, some findings in their research still need further investigation. For instance, an ultrathin oxide layer is present at the a-Si:H/c-Si interface, which might be either the residues from H<sub>2</sub> plasma etching or formed during a vacuum break between their H<sub>2</sub> plasma etching and a-Si:H deposition. However, it is very important to determine the origin of this interfacial oxide layer because the purpose of their research is using the IEEE IOURNAL OF PHOTOVOLTAICS

| Sample no. | HF:HCl:H <sub>2</sub> O<br>(1:1:20, 60 s) | H <sub>2</sub> plasma (500 sccm, 60 s) | a-Si:H<br>(12 nm) | Anneal<br>(290 °C) | Schottky barrier height (eV) |

|------------|-------------------------------------------|----------------------------------------|-------------------|--------------------|------------------------------|

| 1          | ✓                                         |                                        |                   |                    | 0.51                         |

| 2          |                                           | ✓                                      |                   |                    | 0.50                         |

| 3          |                                           | ✓                                      | ✓                 |                    | 0.43                         |

| 4          | ✓                                         |                                        | ✓                 |                    | 0.45                         |

| 5          |                                           | ✓                                      | ✓                 | ✓                  | 0.43                         |

TABLE I

DETAILED DESCRIPTION OF THE SAMPLES FOR DLTS MEASUREMENTS

H<sub>2</sub> plasma for oxide layer etching to improve the a-Si:H/c-Si passivation [15], [16].

2

In this contribution, we developed a low damage H<sub>2</sub> plasma process using PECVD in a parallel plate AK1000 Inline system of Microsystems. The H<sub>2</sub> plasma treatment is performed in a microwave plasma reactor, followed by an intrinsic a-Si:H layer deposition in a capacitively coupled plasma (CCP) reactor without breaking the vacuum. The impact of H<sub>2</sub> gas flow rate and H<sub>2</sub> plasma processing time on the a-Si:H/c-Si interface passivation quality is investigated. The characterization of the a-Si:H/c-Si interface is carried out using quasi-steady-state photoconductance (QSSPC), transmission electron microscopy (TEM), and high angle annular dark field scanning transmission electron microscopy (HAADF-STEM) measurements. Moreover, deeplevel transient spectroscopy (DLTS) is applied to systematically study the a-Si:H/c-Si interface as well as the c-Si bulk defects induced by the H<sub>2</sub> plasma treatment.

### II. EXPERIMENTAL DETAILS

All samples were prepared using planar 200- $\mu$ m-thick n-type phosphorus-doped float zone (FZ) c-Si wafers (150 mm diameter, <100>, 3  $\Omega$ ·cm). The wafers were first exposed to an H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> (4:1) mixture for 10 min to remove organic contamination remaining on the surface, followed with rinsing in deionized (DI) water and a 2 min treatment in diluted HF:HCl:H<sub>2</sub>O (1:1:20). Then the wafers underwent cleaning (HCl:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O = 1:1:5) at room temperature for 10 min to remove metal ions on the surface. Notably, an ultrathin oxide layer of ~1.3 nm was grown on the c-Si surface during this cleaning step, which was determined by spectroscopic ellipsometry and confirmed by TEM images. The cleaned wafers were rinsed in DI water and spin dried, after which they were stored for later use.

For the passivation studies, a reference sample was dipped in HF:HCl:H $_2$ O (1:1:20) for 1 min to remove the silicon oxide layer before loading in an RF-PECVD reactor for 12-nm-thick intrinsic a-Si:H depositions on both sides. The deposition conditions are the following: substrate temperature of 200 °C, RF power density of 25 mW/cm $^2$ , pressure of 2.3 mbar, and silane and H $_2$  gas flow rates of 160 standard cubic centimeters per minute (sccm) and 640 sccm, respectively. All other samples were introduced directly into the microwave PECVD reactor.

To etch the silicon oxide layer present on those samples, we used a microwave H<sub>2</sub> plasma. Such a plasma can generate a higher flux of low-energy H<sub>2</sub> ions with respect to a typical CCP source. These low-energy ions are highly reactive to Si-O bonds and thus etch the silicon oxide layer effectively [17], [18], while, in addition, the damaging impact of the energetic ion bombardment on the c-Si surface is reduced due to the low ion energy [19]. The processing temperature and power density of the H<sub>2</sub> plasma were set to 150 °C and 0.52 W/cm<sup>2</sup>, respectively. A total of two H<sub>2</sub> gas flow rates, 500 and 800 sccm, as well as different H<sub>2</sub> plasma processing times ranging from 30 to 120 s were tested. Identical H<sub>2</sub> plasma treatment and a-Si:H deposition were performed on both sides of the samples. Note that no vacuum break exists between the H<sub>2</sub> plasma treatment and the subsequent a-Si:H deposition. The vacuum break occurs only when flipping over the wafers. The optimal condition (60 s, 500 sccm) was identified in terms of achieving the highest lifetimes  $\tau_{\rm eff}$ , which were recorded by QSSPC after a-Si:H passivation and thermal annealing at the optimal temperature of 290 °C for 3 min [15], [20]. A total of two samples with high lifetimes  $\tau_{\rm eff}$  of 2.5 ms (60 s, 500 sccm) and 1.5 ms (90 s, 500 sccm), respectively, were selected for TEM and HAADF-STEM measurements to characterize the a-Si:H/c-Si interface.

DLTS measurements were performed on the reference samples that received an HF dip as well as on samples that received the H<sub>2</sub> plasma using the optimal condition (60 s, 500 sccm). Depositions of a 12-nm-thick intrinsic a-Si:H layer were performed on only one side (HF or H<sub>2</sub> plasma treated side) of some samples after silicon oxide removal. A detailed description of the samples is presented in Table I. Metallization of all the samples was performed by thermal evaporation of aluminum (Al) using an Alcatel system. This procedure leaves the silicon surface and substrate intact, without causing additional lattice damage. A 200-nm-thick Al layer was deposited on the HF or H<sub>2</sub> plasma processed side of the samples through a shadow mask with circular openings (diameter 1mm) to form the Schottky barrier. A blanket al layer with an identical thickness was deposited on the other side to form the ohmic contact. The maximum temperature during Al depositions was less than 100 °C. It should be remarked that some time elapsed between the HF or H<sub>2</sub> plasma treatment and the Al deposition. This results in the regrowth of the native oxide layer on the c-Si surface for samples 1 and 2, as will be shown below. Current-voltage (I-V) and

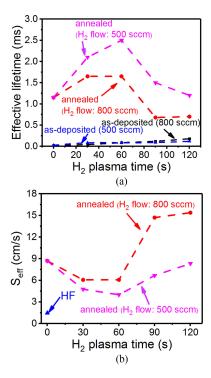

Fig. 1. (a) Effective minority carrier lifetimes  $\tau_{\rm eff}$  at an injection level of  $1\times 10^{15}~{\rm cm^{-3}}$  of the as-deposited and annealed H $_2$  plasma samples at 290 °C as a function of H $_2$  plasma processing time. (b) Calculated maximum effective surface recombination velocity  $S_{\rm eff,\,max}$  of the HF and annealed H $_2$  plasma samples as a function of H $_2$  plasma processing time. The lines are guides to the eye.

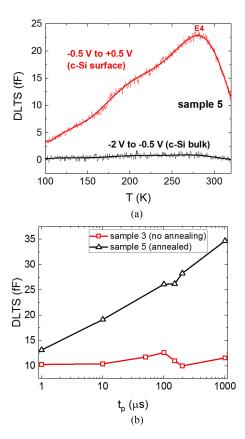

capacitance-voltage (C-V) measurements at room temperature, the latter at a fixed frequency f of 1 MHz, were performed to select samples with a good Schottky barrier (low leakage current) for DLTS. The corresponding values for the barrier height, derived from the forward *I–V* curve, are summarized in Table I. Capacitance DLTS measurements with a bridge operated at f of 1 MHz was used to characterize the deep levels. A bias pulse from depletion to accumulation was applied to the Schottky barrier, while the c-Si substrate was connected to ground. A total of two measurement pulses were used in order to distinguish the defect location, where -2 to -0.5 V was used to detect the defects in the c-Si substrate (depth up to 1  $\mu$ m) and -0.5 to +0.5 V was used to detect the defects at or close to the Schottky barrier/c-Si interface. A typical sampling period  $t_w$  of 51.2 ms was applied. Temperature-scan DLTS was performed by slow ramping (20 mK/s) from 100 to 320 K. The bias pulse duration  $t_p$  was set in the range of 1  $\mu$ s to 1 ms at room temperature to determine the defect-filling kinetics by measuring the DLTS peak amplitude as a function of  $t_p$ .

# III. RESULTS AND DISCUSSION

# A. Passivation Studies and Characterization of a-Si:H/c-Si Interface Using TEM and HAADF-STEM

As shown in Fig. 1(a), the effective lifetimes  $\tau_{\rm eff}$  at an injection level of  $1\times 10^{15}~{\rm cm^{-3}}$  are below 0.12 ms after H<sub>2</sub> plasma treatments and intrinsic a-Si:H depositions, regardless of the H<sub>2</sub> plasma processing conditions. For these H<sub>2</sub> plasma samples

after a-Si:H passivation, thermal annealing at optimal temperature of 290 °C leads to a significant improvement of  $\tau_{\rm eff}$  [15], [20]. In contrast, it is known that the optimal annealing temperature of an intrinsic a-Si:H on an HF-dipped c-Si surface for SHJ solar cells is around 200 °C [14], [15]. In our case, we observe that  $au_{\rm eff}$  at an injection level of 1 imes 10<sup>15</sup> cm<sup>-3</sup> of a reference HF sample degrades from the initial  $au_{\rm eff}$  of 6.8 ms to 1.1 ms when annealing at 290 °C. Such difference in lifetime response to the thermal annealing indicates that the H<sub>2</sub> plasma treatment induces a different a-Si:H/c-Si interface in comparison with the HF dip. Possible explanations of this finding will be further discussed in this section. The impact of H<sub>2</sub> plasma processing time and gas flow rate on lifetimes is shown for the annealed samples in Fig. 1(a). A lower H<sub>2</sub> gas flow rate of 500 sccm results in overall higher lifetimes with respect to a flow rate of 800 sccm. The highest lifetime  $\tau_{\rm eff}$  of 2.5 ms at an injection level of  $1 \times 10^{15} \text{ cm}^{-3}$  is achieved for the annealed H<sub>2</sub> plasma sample (60 s, 500 sccm). A similar dependence of lifetime on the H<sub>2</sub> gas flow rate has been reported by Tang et al. [16]. This is ascribed to insufficient etching of the silicon oxide layer, because a high H<sub>2</sub> flow rate may change the particle type in the H<sub>2</sub> plasma [21]. It has been reported that the electron temperature in the plasma is significantly reduced when the H<sub>2</sub> partial pressure is increased, resulting in less generation of monoatomic H<sub>2</sub> species that are the main etching species for the silicon oxide layer [16], [22], [23]. The untreated sample with neither H<sub>2</sub> plasma nor HF to remove the silicon oxide layer on the c-Si surface, as an extreme case, has a lifetime of 1.1 ms after a-Si:H deposition and thermal annealing at 290 °C [see Fig. 1(a)]. Compared with the best lifetime of 2.5 ms, it suggests that a rapid H<sub>2</sub> plasma treatment of 60 s can effectively modify the c-Si surface and improve the passivation quality. The effective surface recombination velocity ( $S_{\text{eff}}$ ) is calculated as follows:

$$S_{\text{eff}} = \frac{W}{2} \left( \frac{1}{\tau_{\text{eff}}} - \frac{1}{\tau_{\text{bulk}}} \right) \tag{1}$$

where W is the wafer thickness and  $\tau_{\text{bulk}}$  is the bulk lifetime of the wafer ( $\tau_{\rm bulk} > 25$  ms in our case). As shown in Fig. 1(b), the maximum  $S_{\rm eff}(S_{\rm eff, max})$  at an injection level of  $1 \times 10^{15}~{\rm cm}^{-3}$ is estimated by assuming a perfect bulk quality ( $\tau_{\text{bulk}} \to \infty$ ). The best  $S_{\rm eff, \, max}$  of 4 cm/s is obtained for the annealed  $H_2$ plasma sample. Although this is still higher than 1.5 cm/s of the reference HF sample, this is among the best reported  $S_{\rm eff, max}$ values varying from 1.3 to 8 cm/s [14], [15], [24]–[27]. For instance, Tang et al. showed  $S_{\rm eff, max}$  of 1.3 cm/s by a 25 nm intrinsic a-Si:H layer on 120-μm-thick n-type Czochralski wafers  $(125 \times 125 \text{ mm}^2, <100>, 3 \Omega \cdot \text{cm})$  [15]; de Wolf *et al.* achieved  $S_{\rm eff, max}$  of 2.5 cm/s by a 50 nm intrinsic a-Si:H layer on 300- $\mu$ m-thick n-type FZ wafers (3  $\Omega$ ·cm) [25]; Dauwe et al. showed  $S_{\rm eff, \, max}$  of 3 cm/s by a 30 nm intrinsic a-Si:H layer on 300- $\mu$ m-thick p-type FZ wafers (<100>, 1.6  $\Omega$ ·cm) [26]; Moreno et al. reported  $S_{\rm eff, \, max}$  of 8 cm/s by a 40 nm intrinsic a-Si:H layer on 280- $\mu$ m-thick n-type FZ wafers (<100>, 1–5  $\Omega \cdot \text{cm}$ ) [14].

Moreover, another interesting phenomenon should be addressed. As illustrated in Fig. 1,  $\tau_{\rm eff}$  and  $S_{\rm eff,\,max}$  of annealed  $H_2$  plasma samples show similar trends as a function of

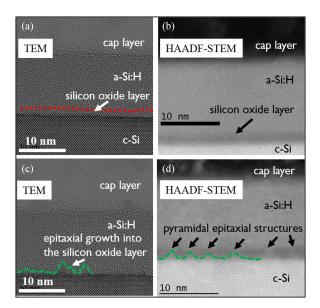

Fig. 2. (a) TEM. (b) HAADF-STEM image of the sample processed by the optimal  $\rm H_2$  plasma condition (60 s, 500 sccm). (c) TEM. (d) HAADF-STEM image of the sample processed by a slightly longer processing time (90 s, 500 sccm).

processing time, regardless of the gas flow rates. For instance, the highest  $\tau_{\rm eff}$  at the injection level of 1  $\times$  10<sup>15</sup> cm<sup>-3</sup> is always achieved on the samples treated with the H2 plasma of 60 s, whereas a slightly longer processing time of 90 s causes  $au_{

m eff}$  degradation. Hence, a sample processed by the optimal condition (60 s, 500 sccm) as well as a sample processed by a longer processing time (90 s, 500 sccm) is selected for TEM and HAADF-STEM measurements to characterize the a-Si:H/c-Si interface. Thermal annealing at 290 °C was performed on both samples before electron microscope inspection. Fig. 2(a) shows the TEM image of the sample processed by a 60 s H<sub>2</sub> plasma. A flat and atomically abrupt interface is visualized, which is required to achieve excellent passivation quality [28]. An approximately 1-nm-thick interfacial oxide layer is observed (dash-dot line), as also well recognized in the HAADF-STEM image [see Fig. 2(b)]. Since no vacuum break exists between the H<sub>2</sub> plasma treatment and the a-Si:H deposition, such ultrathin oxide layer might result from incomplete H<sub>2</sub> plasma etching. Additionally, one H<sub>2</sub> plasma treated sample without a-Si:H deposition is dipped in DI water and we observe that the H<sub>2</sub> plasma processed c-Si surface is hydrophobic in spite of the oxide layer. Such hydrophobicity is stable in the ambient environment for at least several tens of hours. This suggests that the plasma etched oxide layer is strongly hydrogenated. Therefore, H2 effusion and epitaxial growth can be prevented during a-Si:H deposition and subsequent thermal annealing, resulting in an excellent c-Si surface passivation [29]–[32]. In contrast, as shown in Fig. 2(c) and (d), a rough c-Si surface with pyramidal epitaxial structures extending through the oxide layer into the a-Si:H layer is observed for the sample processed by H<sub>2</sub> plasma of 90 s, resulting in the  $\tau_{\rm eff}$  degradation. This is because a longer H<sub>2</sub> plasma etching of 90 s may yield a slightly thinner oxide layer, which is insufficient to suppress epitaxial growth. In our case, it is challenging to determine the etch rate accurately based on the

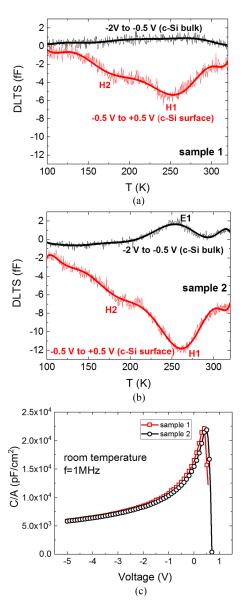

Fig. 3. DLT-spectra of (a) sample 1 and (b) sample 2, and (c) corresponding C–V characteristics.

TEM and HAADF-STEM images since the starting oxide layer thickness is only  $\sim 1.3$  nm and the etching is inhomogeneous. Approximately 0.4–0.6 nm silicon oxide layer is etched by  $H_2$  plasma in 90 s, whereas there are areas with a higher etch rate (1.3 nm/90 s) and areas with a lower etch rate (0 nm/90 s), as illustrated in Fig. 2(c).

# B. Characterization of the a-Si:H/c-Si Interface and the c-Si Bulk Using DLTS

As shown in Fig. 3(a) and (b), for the DLT spectrum from -0.5 to +0.5 V, probing the interface region, a pronounced broad deep level peak with maximum at 260 K and a shoulder at 175 K are present at the c-Si surface of samples 1 and 2 (see Table I), labeled H1 and H2, respectively, which can be assigned to point defects at the interface [33]. However, all the peaks are negative with  $\Delta C < 0$ , which is a signature of hole traps in

n-type c-Si. Normally, when applying a Schottky barrier to ntype c-Si, DLTS mainly measures the defects related to the majority carriers, i.e., electron traps in this case. The observed hole traps of samples 1 and 2 could be attributed to the presence of an inversion layer populated by free holes at the silicon oxide/c-Si interface caused by a high Schottky barrier height (listed in Table I) [34]. The intensity of the DLTS signal at 260 K for the H<sub>2</sub>-plasma sample 2 is significantly higher with respect to that of HF sample 1. According to the C-V characteristics shown in Fig. 3(c), both samples 1 and 2 behave more like a metaloxide semiconductor capacitor. This can be derived from the fact that the capacitance keeps on increasing for positive bias up to 0.5 V. Beyond that point, the measured capacitance at 1 MHz collapses due to the presence of the high forward current (conductance). For a true Schottky barrier, the capacitance will start to decrease immediately at 0 V. The delay of the capacitance collapse suggests the presence of a thin silicon oxide layer on the c-Si surface, which confirms the TEM observations of H<sub>2</sub>plasma samples. Note that for both the HF-treated sample 1 and the H<sub>2</sub>-plasma sample 2, regrowth of the native oxide due to air exposure before the Al deposition is expected to occur. This gives rise to similar broad hole traps for sample 1 but smaller in amplitude, because the oxide layer is thinner in the HF sample 1 with respect to that in sample 2 consisting of both native oxide and oxide residues from H<sub>2</sub> plasma etching. According to the literature, a native oxide layer with a thickness of several angstroms can be formed on the c-Si surface in a very short time of  $\sim 30$  s after the HF dip [35]. Assuming that the hole traps in Fig. 3(a) and (b) are related to Si/SiO<sub>2</sub> interface states, one can compare with literature data on p-type silicon, where similar spectra have been obtained [36]–[38]. The shoulder H2 could then correspond with the donor level at  $E_{\rm V}$  + 0.3 eV of the  $P_b$  dangling bond centers [37]–[40]. The main peak H1 could then correspond with the  $P_{\rm b1}$  dangling bond center at the (100) interface, giving rise to near midgap states [41]-[43]. As shown in Fig. 3(b), when applying a more negative bias pulse -2 to -0.5 V, the electron trap with label E1 is observed in the c-Si substrate of H<sub>2</sub> sample 2, while no electron trap is found in the HF sample 1 within the detection limit of about  $10^{11}$  cm<sup>-3</sup>. The peak E1 at 250 K could correspond with the phosphorusvacancy pair (E-center) [44], [45]. The formation of electron traps in H<sub>2</sub>-plasma treated n-type silicon is well-documented in the literature [46]–[48]. Displacement damage is created at the c-Si near-surface layer. These Frenkel defects (vacancies and interstitials) are quite mobile and can diffuse some distance in the silicon substrate.

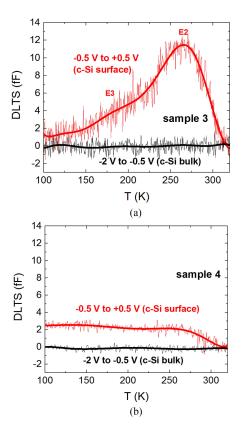

Fig. 4(a) shows the DLT-spectra of sample 3, which was processed by  $\rm H_2$  plasma (60 s, 500 sccm) followed by a-Si:H passivation. Note that the type of the traps at the c-Si surface is changed from hole traps for samples 1 and 2 to electron traps for sample 3. This is due to the reduced Schottky barrier height after a-Si:H deposition, as shown in Table I. A broad peak at 270 K with a shoulder at about 180 K is observed at the c-Si surface (-0.5 to +0.5 V spectrum), labeled E2 and E3, respectively. This spectrum looks similar to what has been found before in DLTS for a-Si:H/n-type c-Si interfaces [33]. In contrast to sample 2, no electron traps are detected in the c-Si substrate.

Fig. 4. DLT-spectra of (a) sample 3 and (b) sample 4.

This indicates that the phosphorus-vacancy pair defect is either passivated by  $\rm H_2$  released from the a-Si:H layer or annealed out during the a-Si:H deposition at 200 °C [49]. Fig. 4(b) shows the DLT spectra of the HF-treated sample 4 after a-Si:H passivation. No obvious peaks are observed in the c-Si substrate, whereas a minor broad peak between 100 and 300 K is found at the c-Si surface, indicating the presence of very limited a-Si:H/c-Si interface defects and thus corresponding to a high  $\tau_{\rm eff}$  of 6.8 ms achieved in the passivation study.

As illustrated in Fig. 5(a), broader and higher peaks of the H<sub>2</sub> plasma sample 5 after thermal annealing of a-Si:H are observed close to the c-Si surface with respect to sample 3 without annealing. Fig. 5(b) shows that the DLTS amplitude of sample 3 stays more or less constant with a longer bias pulse duration  $t_p$ , while the DLTS amplitude of sample 5 continues to increase. Such a behavior has been reported before by us for a-Si:H on c-Si and indicates that electron traps inside the a-Si:H layer are probed by tunneling of electrons between the c-Si/a-Si:H interface and the border traps [33]. They most likely correspond with the acceptor states associated with D defects in a-Si:H, i.e., a dangling bond in an amorphous environment [50]–[56]. The thermal annealing at 290 °C seems to activate the D defects in the a-Si:H layer possibly by the release of hydrogen, leading to a more defective a-Si:H layer. Such a transformation of defects in a-Si:H by thermal annealing is well-known [57]–[59] and has been explained in terms of the defect-pool model [60]. From the results in Figs. 4 and 5, it is thus concluded that by thermal annealing interface states are traded for by less recom-

Fig. 5. DLT-spectra of (a) sample 5 and (b) DLTS amplitude versus bias pulse duration  $t_p$  varying from 1  $\mu$ s to 1 ms for samples 3 and 5 at room temperature.

bination active border traps inside the a-Si:H layer. In addition, the released hydrogen from a-Si:H as well as the hydrogen incorporated during  $H_2$  plasma treatment may diffuse to the c-Si surface, and thus, the surface defects can be substantially passivated. This may explain the significant  $\tau_{\rm eff}$  improvement after thermal annealing in the passivation studies. In future work, this dry process will be further optimized to achieve a perfectly uniform  $H_2$  plasma etching process, and thus, the resulted lifetimes might be improved and comparable to the lifetimes achieved by the HF treatment. Then, such process will be applied to textured wafer surfaces in combination with intrinsic and doped a-Si:H layers for SHJ solar cell fabrication.

# IV. CONCLUSION

We have developed a dry passivation process for n-type c-Si surfaces using microwave  $\rm H_2$  plasma treatment followed by a-Si:H deposition without breaking the vacuum. The optimal  $\rm H_2$  plasma condition is identified in terms of achieving the highest lifetimes  $\tau_{\rm eff}$  after thermal annealing, giving rise to the best  $\tau_{\rm eff}$  of 2.5 ms and corresponding  $S_{\rm eff,\,max}$  as low as 4 cm/s. Characterization of the a-Si:H/c-Si interface using TEM and HAADF-STEM shows the presence of a  $\sim$ 1-nm-thick silicon oxide layer on the c-Si surface. Such  $\rm H_2$  plasma etched oxide layer is highly hydrogenated, which can prevent  $\rm H_2$  effusion and epitaxial growth during a-Si:H deposition and thermal annealing that are required to achieve excellent c-Si surface passivation. DLTS measurements indicate  $\rm H_2$ -plasma-induced electron and

hole traps at the c-Si surface as well as in the c-Si substrate, where the hole traps in the c-Si disappear after a-Si:H deposition. Thermal annealing at 290 °C yields a more defective a-Si:H layer possibly due to the release of hydrogen. However, the combination of such released hydrogen and the hydrogen introduced during  $H_2$  plasma treatment may diffuse to the c-Si surface and passivate the surface defects, leading to a significant  $\tau_{\rm eff}$  improvement after thermal annealing.

#### REFERENCES

- [1] M. Taguchi *et al.*, "24.7% record efficiency HIT solar cell on thin silicon wafer," *IEEE J. Photovolt.*, vol. 4, no. 1, pp. 96–99, Jan. 2014.

- [2] M. A. Green et al., "Solar cell efficiency tables (version 50)," Prog. Photovolt. Res. Appl., vol. 25, no. 7, pp. 668–676, 2017.

- [3] H. Angermann et al., "Passivation of textured substrates for a-Si:H/c-Si hetero-junction solar cells: Effect of wet-chemical smoothing and intrinsic a-Si:H interlayer," Mater. Sci. Eng. B, vols. 159–160, pp. 219–223, 2009.

- [4] M. Tanaka et al., "Development of new a-Si/c-Si heterojunction solar cells: ACJ-HIT (artificially constructed junction-heterojunction with intrinsic thin-layer)," Jpn. J. Appl. Phys., vol. 31, no. 11, pp. 3518–3522, 1992.

- [5] J. Ge et al., "Analysis of intrinsic hydrogenated amorphous silicon passivation layer growth for use in heterojunction silicon wafer solar cells by optical emission spectroscopy," J. Appl. Phys., vol. 113, no. 23, 2013, Art. no. 234310.

- [6] I. Martin et al., "Surface passivation of p-type crystalline Si by plasma enhanced chemical vapor deposited amorphous SiCx:H films," Appl. Phys. Lett., vol. 79, pp. 2199–2201, 2001.

- [7] M. W. M. Van Cleef, F. M. Schuurmans, A. S. H. Van der Heide, A. Schönecker, and R. E. I. Schropp, "Passivation of c-Si solar cells by low temperature H-treatments and deposited a-Si:H layers," in *Proc. 2nd World Conf. Exhib. Photovolt. Energy Convers.*, 1998, pp. 1661–1664.

- [8] H. Yamada, "Low-temperature surface cleaning method using low-energy reactive ionized species," J. Appl. Phys., vol. 65, no. 2, pp. 775–781, 1989.

- [9] T. Shibata, Y. Nanishi, and M. Fujimoto, "Low-temperature Si surface cleaning by hydrogen beam with electron-cyclotron-resonance plasma excitation," *Jpn. J. Appl. Phys.*, vol. 29, no. 7, pp. L1181–L1184, 1990.

- [10] E. A. Irene, "Applications of spectroscopic ellipsometry to microelectronics," *Thin Solid Films*, vol. 233, nos. 1–2, pp. 96–111 1993.

- [11] R. E. Thomas et al., "Carbon and oxygen removal from silicon (100) surfaces by remote plasma cleaning techniques," J. Vac. Sci. Technol. A, vol. 10, no. 4, pp. 817–822, 1992.

- [12] T. Bearda et al., "Thin epitaxial silicon foils using porous-silicon-based lift-off for photovoltaic application," MRS Adv., vol. 1, no. 48, pp. 3235– 3246, 2016.

- [13] I. Martin et al., "Improvement of crystalline silicon surface passivation by hydrogen plasma treatment," Appl. Phys. Lett., vol. 84, no. 9, pp. 1474– 1476, 2004.

- [14] M. Moreno, M. Labrune, and P. R. I. Cabarrocas, "Dry fabrication process for heterojunction solar cells through in-situ plasma cleaning and passivation," Sol. Energy Mater Sol. Cells, vol. 94, no. 3, pp. 402–405, 2010.

- [15] M. Tang et al., "Excellent passivation of thin silicon wafers by HF-free hydrogen plasma etching using an industrial ICPECVD tool," Phys. Status Solidi RRL, vol. 9, no. 1, pp. 47–52, 2015.

- [16] M. Tang et al., "Investigation of low-temperature hydrogen plasmaetching processes for silicon wafer solar cell surface passivation in an industrial inductively coupled plasma deposition tool," *IEEE J. Photo*volt., vol. 6, no. 1, pp. 10–16, Jan. 2016.

- [17] M. Delfino, S. Salimian, D. Hodul, A. Ellingboe, and W. Tsai, "Plasma cleaned Si analyzed in situ by x-ray photoelectron spectroscopy, secondary ion mass spectrometry, and actinometry," *J. Appl. Phys.*, vol. 71, no. 2, pp. 1001–1009, 1992.

- [18] W. Tsai et al., "Correlation of plasma and surface chemistry during electron cyclotron resonance hydrogen etching of native silicon oxide," J. Vac. Sci. Technol. A, vol. 11, no. 5, pp. 2525–2529, 1993.

- [19] S. Xiao, S. Xu, and K. Ostrikov, "Low-temperature plasma processing for Si photovoltaics," *Mater. Sci. Eng. R, Rep.*, vol. 78, pp. 1–29, 2014.

- [20] A. H. Mahan, J. Yang, S. Guha, and D. L. Williamson, "Structural changes ina—Si:Hfilm crystallinity with high H dilution," *Phys. Rev. B*, vol. 61, no. 3, pp. 1677–1680, 2000.

- [21] Y. Okamoto and H. Tamagawa, "Production of large area high current ion beams," Rev. Sci. Instrum., vol. 43, no. 8, pp. 1193–1197, 1972.

- [22] H. Amemiya, K. Shimizu, S. Kato, and Y. Sakamoto, "Measurements of energy distributions in ECR plasma," *Jpn. J. Appl. Phys.*, vol. 27, no. 5, 1988, Art. no. L927.

- [23] K. Shirai, T. Iizuka, and S.-I. Gonda, "Electric probe measurements in an ECR plasma CVD apparatus," *Jpn. J. Appl. Phys.* vol. 28, no. 5, pp. 897–902, 1989.

- [24] T. F. Schulze, H. N. Beushausen, T. Hansmann, L. Korte, and B. Rech, "Accelerated interface defect removal in amorphous/crystalline silicon heterostructures using pulsed annealing and microwave heating," *Appl. Phys. Lett.*, vol. 95, no. 18, 2009, Art. no. 182108.

- [25] S. D. Wolf, S. Olibet, and C. Ballif, "Stretched-exponential a-Si:H/c-Si interface recombination decay," *Appl. Phys. Lett.*, vol. 93, no. 3, 2008, Art. no. 032101.

- [26] S. Dauwe, J. Schmidt, and R. Hezel, "Very low surface recombination velocities on p- and n-type silicon wafers passivated with hydrogenated amorphous silicon films," in *Proc. 29th IEEE Photovolt. Spec. Conf.*, 2002, pp. 1246–1249.

- [27] J. Ge, Z. Ling, J. Wong, T. Mueller, and A. Aberle, "Optimisation of intrinsic a-Si:H passivation layers in crystalline-amorphous silicon heterojunction solar cells," *Energy Procedia*, vol. 15, pp. 107–117, 2012.

- [28] S. D. Wolf and M. Kondo, "Abruptness of a-Si:H/c-Si interface revealed by carrier lifetime measurements," *Appl. Phys. Lett.*, vol. 90, no. 4, 2007, Art. no. 042111.

- [29] T. Mueller, S. Schwertheim, and W. R. Fahrner, "Crystalline silicon surface passivation by high-frequency plasma-enhanced chemical-vapordeposited nanocomposite silicon suboxides for solar cell applications," *J. Appl. Phys.*, vol. 107, no. 1, 2010, Art. no. 014504.

- [30] H. Fujiwara, T. Kaneko, and M. Kondo, "Application of hydrogenated amorphous silicon oxide layers to c-Si heterojunction solar cells," *Appl. Phys. Lett.*, vol. 91, no. 13, 2007, Art. no. 133508.

- [31] A. Janotta et al., "Doping and its efficiency in a-SiO<sub>x</sub>:H," Phys. Rev. B, vol. 69, no. 11, 2004, Art. no. 115206.

- [32] J. Ge et al., "Excellent silicon surface passivation achieved by industrial inductively coupled plasma deposited hydrogenated intrinsic amorphous silicon suboxide," Int. J. Photoenergy, vol. 2014, 2014, Art. no. 752967.

- [33] E. Simoen, V. Ferro, and B. J. Osullivan, "Deep-level transient spectroscopy of Al/a-Si:H/c-Si structures for heterojunction solar cell applications," *J. Appl. Phys.*, vol. 116, no. 23, 2014, Art. no. 234501.

- [34] E. Simoen et al., "Study of metal-related deep-level defects in germanide Schottky barriers on n-type germanium," J. Appl. Phys., vol. 104, no. 2, 2008, Art. no. 023705.

- [35] W. Liu, F. Meng, X. Zhang, and Z. Liu, "Evolution of a native oxide layer at the a-Si:H/c-Si interface and its influence on a silicon heterojunction solar cell," ACS Appl. Mater. Interfaces, vol. 7, no. 48, pp. 26522–26529, 2015.

- [36] R. Beyer, H. Burghardt, I. Thurzo, D. Zahn, and T. Geßner, "A deconvolution of the transient response of (100) Si/SiO<sub>2</sub> semiconductor—insulator interface states according to small pulse excitation: Evidence of different branches of charge transition," *Solid-State Electron.*, vol. 44, no. 8, pp. 1463–1470, 2000.

- [37] C. Gong et al., "A deep-level transient spectroscopy study of silicon interface states using different silicon nitride surface passivation schemes," Appl. Phys. Lett., vol. 96, no. 10, 2010, Art. no. 103507.

- [38] E. Simoen et al., "A DLTS Study of SiO2 and SiO2/SiNx Surface Passivation of Silicon," J. Electrochem. Soc., vol. 158, no. 6, pp. H612–H617, 2011

- [39] H. G. Grimmeiss et al., "Optical and electrical studies of interface traps in the Si/SiO<sub>2</sub> system by modified junction space-charge techniques," Phys. Rev. B, vol. 39, no. 8, pp. 5175–5185, 1989.

- [40] L. Dobaczewski et al., "Energy state distributions of the P<sub>b</sub> centers at the (100), (110), and (111) Si/SiO<sub>2</sub> interfaces investigated by Laplace deep level transient spectroscopy," Appl. Phys. Lett., vol. 92, no. 24, 2008, Art. no. 242104.

- [41] N. Haneji, L. Vishnubhotla, and T. P. Ma, "Possible observation of Pb0 and Pb1 centers at irradiated (100)Si/SiO<sub>2</sub> interface from electrical measurements," *Appl. Phys. Lett.*, vol. 59, no. 26, pp. 3416–3418, 1991.

- [42] J. P. Campbell and P. M. Lenahan, "Density of states of Pb1 Si/SiO2 interface trap centers," Appl. Phys. Lett., vol. 80, no. 11, pp. 1945–1947, 2002.

- [43] P. Lenahan, N. Bohna, and J. Campbell, "Radiation-induced interface traps in MOS devices: Capture cross section and density of states of P<sub>b1</sub> silicon dangling bond centers," *IEEE Trans. Nucl. Sci.*, vol. 49, no. 6, pp. 2708–2712, Jan. 2003.

- [44] J. Garrido, E. Calleja, and J. Piqueras, "Deep centers introduced by argon ion bombardment in n-type silicon," *Solid State Electron.*, vol. 24, no. 12, pp. 1121–1126, 1981.

- [45] A. Szekeres, S. S. Simeonov, and E. Kafedjiiska, "DLTS study of deep levels in Si substrates created by plasma treatment," *Semicond. Sci. Technol.*, vol. 9, no. 10, pp. 1795–1799, 1994.

- [46] A. Szekeres, S. Simeonov, and E. Kafedjiiska, "RF hydrogen plasma influence on shallow and deep levels in crystalline silicon," *Physica B*, vol. 170, nos. 1–4, pp. 231–234, 1991.

- [47] S. Zhu et al., "Electrical characterization of Ar-ion-bombardment-induced damage in Au/Si and PtSi/Si Schottky barrier contacts," Semicond. Sci. Technol., vol. 16, no. 2, pp. 83–90, 2001.

- [48] E. Simoen et al., "Dry etch damage in n-type crystalline silicon wafers assessed by deep-level transient spectroscopy and minority carrier lifetime," J. Vac. Sci. Technol. B, vol. 36, no. 4, 2018, Art. no. 041201.

- [49] L. Kimerling, H. Deangelis, and J. Diebold, "On the role of defect charge state in the stability of point defects in silicon," *Solid State Commun.*, vol. 16, no. 1, pp. 171–174, 1975.

- [50] R. S. Crandall, "Trap spectroscopy of a-Si:H diodes using transient current techniques," J. Electron. Mater., vol. 9, no. 4, pp. 713–726, 1980.

- [51] R. S. Crandall, "Deep electron traps in hydrogenated amorphous silicon," *Phys. Rev. B*, vol. 24, no. 12, pp. 7457–7459, 1981.

- [52] J. D. Cohen, J. P. Harbison, and K. W. Wecht, "Identification of the dangling-bond state within the mobility gap of a-Si:H by depletion-widthmodulated ESR spectroscopy," *Phys. Rev. Lett.*, vol. 48, no. 2, pp. 109– 112, 1982.

- [53] D. V. Lang, J. D. Cohen, and J. P. Harbison, "Measurement of the density of gap states in hydrogenated amorphous silicon by space charge spectroscopy," *Phys. Rev. B*, vol. 25, no. 8, pp. 5285–5320, 1982

- [54] N. M. Johnson and D. K. Biegelsen, "Identification of deep-gap states in a-Si:H by photo-depopulation-induced electron-spin resonance," *Phys. Rev. B*, vol. 31, no. 6, pp. 4066–4069, 1985.

- [55] I. Thurzo et al., "Characterization of a-Si:H based metal/insulator/ semiconductor structures by feedback charge capacitance-voltage measurements and charge deep-level transient spectroscopy," J. Appl. Phys., vol. 82, no. 9, pp. 4372–4377, 1997.

- [56] I. Thurzo et al., "Small-signal deep level transient spectroscopy on hydrogenated amorphous silicon based metal/insulator/semiconductor structures," J. Appl. Phys., vol. 84, no. 12, pp. 6906–6910, 1998

- [57] T. Schulze, C. Leendertz, N. Mingirulli, L. Korte, and B. Rech, "Impact of Fermi-level dependent defect equilibration on V<sub>oc</sub> of amorphous/crystalline silicon heterojunction solar cells," *Energy Procedia*, vol. 8, pp. 282–287, 2011.

- [58] S. D. Wolf, C. Ballif, and M. Kondo, "Kinetics of a-Si:H bulk defect and a-Si:H/c-Si interface-state reduction," *Phys. Rev. B*, vol. 85, no. 11, 2012, Art. no. 113302.

- [59] A. Bidiville, T. Matsui, H. Sai, and K. Matsubara, "Role of the Fermi level in the formation of electronic band-tails and mid-gap states of hydrogenated amorphous silicon in thin-film solar cells," *J. Appl. Phys.*, vol. 122, no. 9, 2017, Art. no. 093101.

- [60] M. J. Powell and S. C. Deane, "Defect-pool model and the hydrogen density of states in hydrogenated amorphous silicon," *Phys. Rev. B*, vol. 53, no. 15, pp. 10121–10132, 1996.

Authors' photographs and biographies not available at the time of publication.