# ARENBERG DOCTORAL SCHOOL Faculty of Engineering Science

# Security Primitives for Protected-Module Architectures

Based on Program-Counter-Based Memory Access Control

### **Raoul Strackx**

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor in Engineering

### **Security Primitives for Protected-Module Architectures**

Based on Program-Counter-Based Memory Access Control

#### Raoul STRACKX

Examination committee:

Prof. dr. ir. Jean Berlamont, chair

Prof. dr. ir. Frank Piessens, supervisor

Prof. dr. ir. Wouter Joosen, co-supervisor

Prof. dr. Dave Clarke

Prof. dr. ir. Ingrid Verbauwhede

Prof. dr. ir. Bart Preneel

David Grawrock

(Intel)

Prof. dr. Andrew Martin (Oxford University) Dissertation presented in partial fulfillment of the requirements for the degree of Doctor in Engineering

| © 2014 KU Leuven – Faculty of Engineering Science<br>Uitgegeven in eigen beheer, Raoul Strackx, Celestijnenlaan 200A box 2402, B-3001 Heverlee (Belgium)                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt worden door middel van druk, fotokopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever. |

| All rights reserved. No part of the publication may be reproduced in any form by print, photoprint, microfilm, electronic or any other means without written permission from the publisher.                                                                     |

| ISBN 978-94-6018-940-1<br>D/2014/7515/163                                                                                                                                                                                                                       |

### **Preface**

This thesis is the result of 5 years of work, during which time I got a lot of help from a lot of people. I would like to take this opportunity to thank them here.

Foremost, I would like to thank my supervisor, Frank Piessens who constantly exceeded any expectations a PhD student may have of his supervisor. Frank, thank you for allowing me to discover where my interests lay, for every time you took up the role of "devil's advocate" (and apologized for having to do so) and for your endless support when I hardheadedly wanted to resubmit my paper to the next big conference. Also thank you for all the stimulating discussions over the years, even at times when you lacked the time.

I would also like to thank the members of my PhD jury: Frank Piessens, Wouter Joosen, Dave Clarke, Bart Preneel, Ingrid Verbauwhede, David Grawrock, Andrew Martin, and Jean Berlamont.

Also a thank you to Pieter Agten, Niels Avonds, Dave Clarke, Wilfried Daniels, Ruan de Clercq, Christophe Huygens, Niels Lambrigts, Job Noorman, Marco Patrignani, Frank Piessens Bart Preneel, Dries Schellekens, Anthony Van Herrewege, Gijs Vanspauwen, Ruben Vandevelde, and Ingrid Verbauwhede for sharing my interest in protected-module architectures and our interesting discussions. I hope that we can continue our collaboration in the near and distant future.

A special thanks to my 05.18 version 1.0 colleagues, Pieter Philippaerts and Frédéric Vogels. Sharing an office often felt like appearing in a live Monthy Python sketch (especially "The Argument Clinic" comes to mind) but I have great memories of those times.

To all the members of 05.18 version 1.1 and the "lunch buddies," a special thanks for all their jokes, sass and support of the last few years. Milica Milutinović, you seem to possess a remarkable amount of energy. I hope that some of it will rub off on me, eventually. Rula Sayaf, your lighthearted nature at all times

i

ii \_\_\_\_\_\_ PREFACE

is remarkable and an example to us all. Pieter Agten, we shared some of my greatest travels and hope that many more will follow in the next few years. Frédéric Vogels, thanks for all the moelleux that you brought over the years. Because of all your (in your own words) "extravagances" I had to "endure" over the years, I know that one of the first things you will do when you read this text, is to look for spelling and grammar mistakes. Even with all your vices you're a good friend, so I will even make it eazie for you. Mathy Vanhoef, since you started working here, you have been corrupted by Frédéric. He trained you well. Thanks for all the sass that we have exchanged. Jesper Cockx, you are everything a colleague and friend could wish for. Marco, it is great to have you joining us for lunch, even though your real Italian lunches often makes us jealous. Our sincere apologies if our jealousy ever turns violent. Jan Tobias, thanks for all your weird, but interesting stories of the last few months. They make for entertaining discussions over lunch.

I would also like to specifically thank some people for their support. Dominique Devriese, thank you for all the unexpected coffee breaks, and for all the interesting discussions that usually followed. It has been my pleasure.

Nick Nikiforakis, it was a lot of fun being able to share the excitement of imminent arrivals of paper notifications over the years. I hope we can continue to do so in the future, regardless of the continent where we live.

Gowri Suryanarayana, thanks for all the Indian sweets over the years, they were very tasty.

Marleen Somers, thank you for all your help over the years. You always made sure that conference registrations and hotel bookings were correct and handled quickly, even when you had a lot of other work and already were working overtime. Also your compassion and help when my luggage was permanently lost, was greatly appreciated.

Also to the other people of the secretariat, administration, and business office, thank you for all the fun conversations at the coffee machine and to try to keep all the paper work to a bare minimum. Unfortunately some of you have left the last few months, you're truly missed. To the new colleagues, I hope that you'll stay at least as long at the department as your predecessors because you're great to be around with.

Yolande Berbers, thank you for your trust in my didactic abilities. Also the large amount of freedom has been greatly appreciated.

Also a special thanks to all the students that were forced to attend my exercise sessions. I have tried to make most lessons interesting and challenging, I hope I succeeded.

PREFACE \_\_\_\_\_\_ ii

Work at the department for the last years has been great and I would also like to thank the many people who made that happen. With the grave risk of leaving somebody out: Yolande Berbers, Pieter Agten, Jasper Bogaerts, Ronald Cools, Dave Clarke, Jesper Cockx, Bart De Decker, Willem De Groef, Philippe De Ryck, Lieven Desmet, Dominique Devriese, Francesco Gadaleta, Tom Holvoet, Danny Hughes, Christophe Huygens, Bart Jacobs, Katrien Janssens, Fred Jonker, Wouter Joosen, Bert Lagaisse, Jef Maerien, Milica Milutinović, Jan Tobias Mühlberg, Syeda Nayyab Zia Naqvi, Nick Nikiforakis, Job Noorman, Steven Op de beeck, Marco Patrignani, Willem Penninckx, Pieter Philippaerts, Frank Piessens, Davy Preuveneers, José Proença, Andreas Put, Anne-Sophie Putseys, Esther Renson, Ghita Saevels, Rula Sayaf, Ilya Sergey, Jan Smans, Marleen Somers, Karen Spruyt, Eric Steegmans, Gowri Suryanarayana, Klaas Thoelen, Steven Van Acker, Rinde van Lon, Inge Vandenborne, Annick Vandijck, Mathy Vanhoef, Dries Vanoverberghe, Gijs Vanspauwen, Karen Verresen, Frédéric Vogels, Kim Wuyts and Yves Younan.

Last but definitely not least, I would also like to thank my family for their never-ending support. A special thanks to my dad for the long hours of making me do those language and mathematical exercises. They paid off in the end. To my mother, thank you for all the unexpected desserts when I was studying for exams and the encouraging words. They really helped to fight through tough times. To my sister, thank you for showing to me that an academic diploma may not always be easy, perseverance will always get you where you want to end up. To Gert, your funny stories and bad jokes always made me laugh, even when I was working against a deadline. Thank you for that. Also to my grandparents, thank you all for your never-ending support. It is very sad that some of you are not here to celebrate with us. And a very special thanks to Louis Swinnen, for having the foresight and courage to buy a computer and letting his grandchildren play with it.

I would also like to thank the following projects and scholarships for their financial support:

- The Agency for Innovation by Science and Technology in Flanders (IWT)

- The Intel Lab's University Research Office

- The Research Council KU Leuven: GOA TENSE (GOA/11/007)

### **Abstract**

Our society increasingly depends on computing devices. Customers rely on laptops and mobile devices to access security sensitive applications such as online banking. Companies have to protect their trade secrets. And governments have to guard their country's critical infrastructure against espionage and sabotage.

Security of computing devices in such use cases is paramount and various security measures have been developed that raise the bar significantly for attackers. However, vulnerabilities in such systems still exist and are frequently exploited successfully. A common pitfall is that software security takes a layered approach where privileged layers keep getting extended with new components over the system's lifetime. This results in a snowball effect on the size of these privileged levels and this in turn increases the likelihood of software vulnerabilities. As all applications running on the device rely on the integrity of these layers, increasing the size of their code base has a negative impact on security of the overall device.

Many security measures have been proposed to automatically harden the most privileged software layer, but they all fail to provide strong security guarantees. In this thesis, we considered a different approach. We developed three security primitives that can be applied at most privilege levels. Unlike related approaches, this set of primitives is fixed. Software components can be added easily at any privilege level, but no additional primitives will be required. Moreover, these security primitives can provide provable security guarantees.

The most important security primitive is a program-counter-based access control mechanism. By enforcing different access rights on physical memory depending in which code module the processor is executing, sensitive parts of an application can be strongly isolated. For instance, a cryptographic key can be isolated to a protected module implementing a certificate-signing service. Since the key cannot be accessed by any other code than the module's, it cannot be stolen even if malware was already present on the platform. The access control mechanism

vi \_\_\_\_\_\_ ABSTRACT

also guarantees that the module is only accessible through the interface that it exposes explicitly.

Second, we enable protected modules to limit which protected modules can access their services. Unrestricted access to modules may still allow a large range of attacks. While an attacker may no longer be able to access a well-isolated cryptographic key, for example, the exposed interface may still allow her to sign forged certificates. We prevent such attacks using a capability-based access control mechanism; a module can only be accessed if the caller ever received the capability to do so.

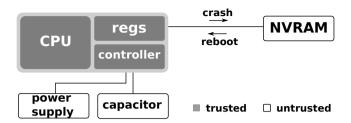

Third, we propose a fast and practical state-continuity system. Using cryptographic properties, protected modules can use many services of the unprotected, legacy system while providing strong security guarantees. Unfortunately, these security guarantees only are ensured while the system is up and running. In practice systems crash, loose power or need to reboot. Integrity and confidentiality protecting the module's state before it is stored on disk is insufficient in such cases. Care must be taken that an attacker cannot present a stale state of a protected module as being fresh. Practical implementations are hindered by the substantial economical costs to add non-volatile storage to the processor. Many computing devices are already shipped with access-controlled non-volatile storage off-chip, but this memory is slow, very limited in size and wears out quickly. We propose an algorithm based on a simple hardware component to avoid all these shortcomings.

During this dissertation we also focused on how these newly-added security primitives can be applied to provide strong security guarantees. A fully-abstract compilation scheme was developed that ensures that software-level abstractions provided to programmers cannot be broken; for every low-level attack, there also exists an attack at source-code level. This significantly simplifies reasoning about the security guarantees that protected modules provide and increases security of the overall system.

## **Beknopte samenvatting**

Onze samenleving hangt steeds meer af van haar computersystemen. Consumenten vertrouwen op laptops en mobiele toestellen om gevoelige toepassingen te raadplegen zoals internetbankieren. Bedrijven dienen hun (digitale) handelsgeheimen te beschermen. En overheden moeten de kritische infrastructuur van hun land waarborgen tegen spionage en sabotage.

Beveiliging van computersystemen in dergelijke toepassingen is van cruciaal belang. Talloze beschermingsmaatregelen zijn dan ook reeds ontwikkeld die succesvolle aanvallen aanzienlijk moeilijker maken. Kwetsbaarheden in software komen echter nog steeds voor en worden nog altijd frequent uitgebuit. Een veelvoorkomende valkuil is dat softwareontwikkeling een gelaagde structuur volgt waarbij geprivilegieerde lagen steeds groter worden wanneer nieuwe componenten worden toegevoegd tijdens de levensduur van het systeem. Dit resulteert in een sneeuwbaleffect van de grootte van deze geprivilegieerde lagen, wat op zijn beurt de kans op softwarekwetsbaarheden sterk vergroot. Aangezien alle applicaties die op het systeem uitvoeren op de integriteit van deze lagen steunen, heeft een toename in de grootte ervan een negatieve invloed op de veiligheid van het geheel van het systeem.

Talloze beschermingsmaatregelen zijn voorgesteld om de meest geprivilegieerde laag automatisch te beschermen, maar geen enkele biedt sterke veiligheidsgaranties. In deze thesis hebben we voor een andere aanpak geopteerd. We hebben drie beveiligingsprimitieven ontwikkeld die op bijna elke geprivilegieerde laag kunnen worden toegepast. In tegenstelling tot andere aanpakken, zijn deze primitieven niet veranderlijk. Nieuwe softwarecomponenten kunnen worden toegevoegd aan het systeem, zonder dat nieuwe primitieven moeten worden ontwikkeld. Bovendien bieden deze primitieven bewijsbare beveiligingsgaranties.

Het belangrijkste beveiligingsprimitief is het toegangscontrolemechanisme op basis van de *program counter*. Door verschillende toegangsrechten op fysiek geheugen af te dwingen op basis van de codemodule die de processor aan

het uitvoeren is, kunnen gevoelige delen van het programma sterk geïsoleerd worden. Neem als voorbeeld een beschermde module die certificaten digitaal ondertekent. De cryptografische sleutel van die module kan sterk geïsoleerd worden. Aangezien het controlemechanisme toegang tot deze sleutel van buiten de module verhindert, kan deze niet gestolen worden door kwaadaardige software. Hetzelfde mechanisme zorgt er ook voor dat de module enkel aangesproken kan worden via de interface die het expliciet beschikbaar stelt.

Een tweede beveiligingsprimitief laat beschermde modules toe om te beperken vanaf waar ze aangesproken kunnen worden. Ongelimiteerde toegang tot modules zou een brede waaier aan aanvallen niet kunnen verhinderen. Zo zou een aanvaller nog steeds zelf gefabriceerde certificaten kunnen laten ondertekenen, ook al heeft zij geen toegang tot de cryptografische sleutel. We verhinderen dergelijke aanvallen door het gebruik van een capabilitygebaseerde toegangscontrole; modules kunnen enkel aangesproken worden indien de aanroeper ooit de mogelijkheid hiervoor heeft gekregen.

Tot slot hebben we een snel en praktisch state-continuity systeem ontwikkeld. Door cryptografische primitieven toe te passen, kunnen beschermde modules gebruikmaken van onbetrouwbare toepassingen zonder dat dit een sterke invloed heeft op de geboden veiligheidsgaranties. Spijtig genoeg kunnen deze garanties enkel gegarandeerd worden zolang het systeem aan het uitvoeren is. Maar in de praktijk crashen systemen, verliezen ze plots hun stroomtoevoer of moeten deze opnieuw opstarten. Het beschermen van de integriteit en confidentialiteit van de status van modules is in deze gevallen onvoldoende. Maatregelen moeten genomen worden om ervoor te zorgen dat een aanvaller geen oude status als nieuw kan presenteren. Praktische implementaties worden hierbij gehinderd doordat niet-volatiel geheugen om economische redenen niet aan de processor kan worden toegevoegd. Veel computersystemen beschikken reeds over nietvolatiel geheugen met een toegangscontrolemechanisme naast de processor maar dit is echter traag, klein en het slijt snel. We hebben een alternatief ontwikkeld op basis van een eenvoudige hardwarecomponent en een algoritme dat deze tekortkomingen ontwijkt.

Tijdens deze dissertatie hebben we ook aandacht besteed aan hoe deze ontwikkelde beveiligingsprimitieven praktisch gebruikt kunnen worden om sterke veiligheidsgaranties te bieden. Er werd een volledig abstract compilatieproces ontwikkeld dat ervoor zorgt dat abstracties die aan programmeurs aangeboden worden op broncodeniveau, niet doorbroken kunnen worden. Zo bestaat voor elke aanval tegen modules die gebruik maken van de beveiligingsprimitieven, een overeenkomstige aanval op het niveau van de gebruikte programmeertaal. Dit vereenvoudigt de redenering over de aangeboden beveiligingsgaranties van modules enorm en zorgt voor een sterkere beveiliging van het systeem in het algemeen.

# **Contents**

| Αŀ  | ostrac | ct      |                                         | V    |

|-----|--------|---------|-----------------------------------------|------|

| Cd  | onten  | ts      |                                         | ix   |

| Lis | st of  | Figures |                                         | χV   |

| Lis | st of  | Tables  |                                         | xvii |

| Lis | st of  | Acrony  | ms                                      | xix  |

| 1   | Intro  | oductio | o <b>n</b>                              | 1    |

|     | 1.1    | Attacl  | king Software                           | 2    |

|     | 1.2    | Existi  | ng Security Measures                    | 5    |

|     |        | 1.2.1   | More Secure Libraries                   | 5    |

|     |        | 1.2.2   | Hardening Legacy Software Automatically | 5    |

|     |        | 1.2.3   | Memory-Safe Languages                   | 6    |

|     |        | 1.2.4   | Software Verification                   | 7    |

|     |        | 1.2.5   | OS Protection Features                  | 8    |

|     |        | 1.2.6   | Hardware Security Modules               | 9    |

|     | 1.3    | Why S   | Software Security Is Still a Mess       | . 11 |

|     | 1.4    | A Nev   | v Deal: Protected-Module Architectures  | 13   |

× \_\_\_\_\_\_ CONTENTS

|   | 1.5  | Buildi  | ng Secure Subsystems: Contributions to the Research Area | 16 |

|---|------|---------|----------------------------------------------------------|----|

|   | 1.6  | Indepe  | endent Research Results by Industry                      | 20 |

|   | 1.7  | Thesis  | Outline                                                  | 21 |

| 2 | Fide | s: Sele | ctively Hardening Software Application Components        | 23 |

|   | 2.1  | Introd  | uction                                                   | 24 |

|   | 2.2  | Object  | tives                                                    | 26 |

|   |      | 2.2.1   | Attacker Model                                           | 27 |

|   |      | 2.2.2   | Security Properties                                      | 27 |

|   | 2.3  | Overv   | iew of the approach                                      | 29 |

|   |      | 2.3.1   | Layout of a Self-Protecting Module                       | 29 |

|   |      | 2.3.2   | Primitive Operations                                     | 31 |

|   |      | 2.3.3   | Life Cycle of a Self-Protecting Module                   | 32 |

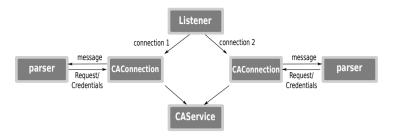

|   |      | 2.3.4   | Secure Local Communication                               | 33 |

|   |      | 2.3.5   | Updating SPMs                                            | 36 |

|   |      | 2.3.6   | The Vault                                                | 36 |

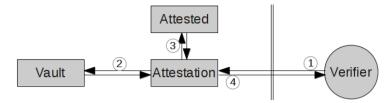

|   |      | 2.3.7   | Remote Attestation                                       | 37 |

|   | 2.4  | A Pro   | totype Implementation                                    | 38 |

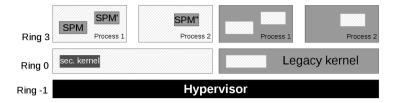

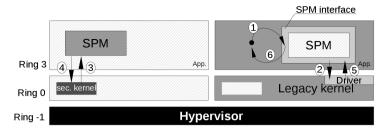

|   |      | 2.4.1   | The Fides architecture                                   | 38 |

|   |      | 2.4.2   | Automated Compilation of Modules                         | 42 |

|   | 2.5  | Evalua  | ation                                                    | 44 |

|   |      | 2.5.1   | Security Evaluation                                      | 44 |

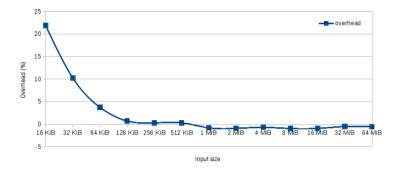

|   |      | 2.5.2   | Performance Evaluation                                   | 45 |

|   | 2.6  | Relate  | d Work                                                   | 49 |

|   | 2.7  | Conclu  | isions                                                   | 51 |

|   | 2.8  | Post-F  | Publication Remarks                                      | 51 |

| 3 | Salu | ıs: Non | -Hierarchical Memory Access Rights to Enforce PoLP       | 55 |

CONTENTS \_\_\_\_\_\_xi

|   | 3.1 | Introd | luction                                       | 56   |

|---|-----|--------|-----------------------------------------------|------|

|   | 3.2 | Attacl | ker Model & Security Properties               | 60   |

|   | 3.3 | Overv  | riew of the Approach                          | . 61 |

|   |     | 3.3.1  | Compartments of Least Privilege               | . 61 |

|   |     | 3.3.2  | Provided Services                             | 64   |

|   |     | 3.3.3  | Life Cycle of a Compartmentalized Application | 65   |

|   |     | 3.3.4  | Secure Communication                          | 66   |

|   |     | 3.3.5  | Unforgeable references                        | 68   |

|   |     | 3.3.6  | Writing Compartmentalized Applications        | 70   |

|   | 3.4 | Imple  | mentation                                     | . 71 |

|   |     | 3.4.1  | Program Counter-Based Access Control          | . 71 |

|   |     | 3.4.2  | System Call API                               | 72   |

|   |     | 3.4.3  | Conflicting System Calls                      | 73   |

|   |     | 3.4.4  | Unforgeable references                        | 74   |

|   | 3.5 | Evalua | ation                                         | 75   |

|   |     | 3.5.1  | Security Evaluation                           | 75   |

|   |     | 3.5.2  | Performance Evaluation                        | 77   |

|   | 3.6 | Relate | ed Work                                       | 80   |

|   | 3.7 | Concl  | usion                                         | 82   |

|   | 3.8 | Post-I | Publication Remarks                           | 82   |

| 4 | ICE | A D-   | arian High Count Chats Continuin Colors       | 83   |

| 4 |     |        | ssive, High-Speed, State-Continuity Scheme    |      |

|   | 4.1 |        | luction                                       | 84   |

|   | 4.2 |        | em Definition                                 | 87   |

|   |     | 4.2.1  | Attacker Model                                | 87   |

|   |     | 4.2.2  | Security Properties                           | 88   |

|   |     | 4.2.3  | Applicability                                 | 88   |

xii \_\_\_\_\_\_CONTENTS

| Α | Intel | Softw   | are Guard eXtensions                      | 135   |

|---|-------|---------|-------------------------------------------|-------|

|   | 5.3   | Long-   | Term Ambitions                            | 133   |

|   |       | 5.2.3   | Applications                              | . 131 |

|   |       | 5.2.2   | Writing Modules                           | 130   |

|   |       | 5.2.1   | New Security Guarantees                   | 128   |

|   | 5.2   | Near I  | Future                                    | 128   |

|   | 5.1   | Contri  | ibutions                                  | 123   |

| 5 | Con   | clusion |                                           | 123   |

|   | 4.10  | Post-P  | Publication Remarks                       | 120   |

|   | 4.9   | Conclu  |                                           | 120   |

|   | 4.8   |         | ed Work                                   | 118   |

|   | 4.7   | _       | rations Towards Hardware Security Modules | 117   |

|   | 4.6   |         | mance Evaluation                          | 114   |

|   |       | 4.5.2   | Liveness Properties                       | 113   |

|   |       | 4.5.1   | Safety Properties                         | 106   |

|   | 4.5   | Securi  | ty Evaluation                             | 106   |

|   |       | 4.4.3   | Distant Future Architectures              | 105   |

|   |       | 4.4.2   | SGX-Based Implementation                  | 104   |

|   |       | 4.4.1   | ICE on Commodity Hardware                 | 102   |

|   | 4.4   | Impler  | mentations                                | . 101 |

|   |       | 4.3.4   | ICE Libraries                             | 94    |

|   |       | 4.3.3   | ChkPassword: A Running Toy Example        | 92    |

|   |       | 4.3.2   | Guards: Storing Freshness Info            | 92    |

|   |       | 4.3.1   | Architecture                              | 90    |

|   | 4.3   | State-  | Continuity as a Library                   | 89    |

CONTENTS \_\_\_\_\_\_xiii

| В   | Protected-Module Architectures vs Microkernels 1 |                                                    |     |  |  |

|-----|--------------------------------------------------|----------------------------------------------------|-----|--|--|

|     | B.1                                              | Why Microkernels Failed                            | 138 |  |  |

|     | B.2                                              | Why PMAs Won't Share the Same Fate as Microkernels | 139 |  |  |

| ·   |                                                  | 141                                                |     |  |  |

| Lis | List of Publications                             |                                                    |     |  |  |

# **List of Figures**

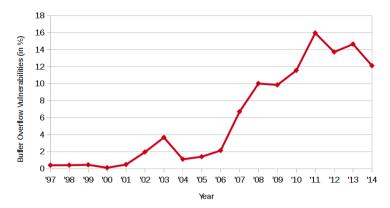

| 1.1 | The number of buffer overflow vulnerabilities has seen a significant increase since 2006                                       | 4  |

|-----|--------------------------------------------------------------------------------------------------------------------------------|----|

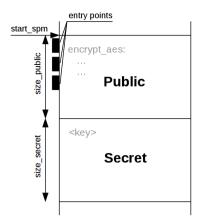

| 2.1 | The layout of an SPM                                                                                                           | 30 |

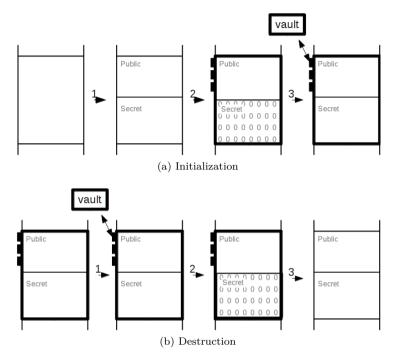

| 2.2 | The life cycle of an SPM from (a) initialization to (b) destruction.                                                           | 32 |

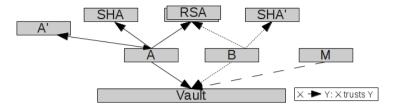

| 2.3 | Fides enables the creation of complex trust networks                                                                           | 33 |

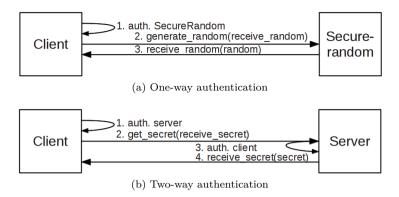

| 2.4 | Communication protocols between two SPMs                                                                                       | 35 |

| 2.5 | Fides supports attestion easily and transparently                                                                              | 38 |

| 2.6 | Layout of the Fides architecture                                                                                               | 39 |

| 2.7 | Implementation of the Fides architecture                                                                                       | 43 |

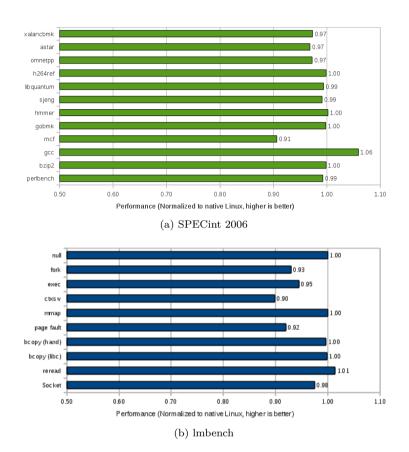

| 2.8 | The performance impact of Fides on the overall system                                                                          | 47 |

| 3.1 | Salus' compartmentalization enables strong isolation of security-<br>sensitive data possibly vulnerable code                   | 58 |

| 3.2 | Layout of compartments in Salus                                                                                                | 62 |

| 3.3 | The life cycle of a protected compartment from creation to destruction                                                         | 66 |

| 3.4 | By enforcing that compartments can only be accessed via unforgeable references, stronger security guarantees can be guaranteed | 69 |

| 3.5 | Salus' performance overhead on the gzip macro benchmark drops significantly as the input file size increases                   | 79 |

xvi \_\_\_\_\_LIST OF FIGURES

| 4.1 | ICE provides state-continuity guarantees to isolated modules while trusting only a few key components | 90   |

|-----|-------------------------------------------------------------------------------------------------------|------|

| 4.2 | Architecture of guarded memory                                                                        | . 91 |

| 4.3 | Stored states are confidentiality and integrity protected. Freshness is based on the enclosed guard   | 95   |

| 4.4 | Depending on the timing of a crash, three distinct situations can occur                               | 98   |

| 4.5 | ICE can provide state-continuity guarantees to isolated modules of many state-of-the-art PMAs         | 102  |

| 4.6 | Microbenchmarks of various TPM operations                                                             | 115  |

## **List of Tables**

| 2.1 | The enforced memory access control model                             | 30  |

|-----|----------------------------------------------------------------------|-----|

| 2.2 | The TCB consists of only 7K lines of code                            | 44  |

| 2.3 | SPM vs. driver access overhead                                       | 47  |

| 2.4 | Microbenchmarks measuring the cost of calling an (authenticated) SPM | 48  |

| 2.5 | HTTPS-server performance                                             | 49  |

| 3.1 | Salus' access control model                                          | 61  |

| 3.2 | Compartment access overhead                                          | 78  |

| 3.3 | Performance of a compartimentalized, TLS-enabled webserver.          | 78  |

| 4.1 | Breakdown of lines of codes for libice0 and libicen                  | 104 |

| 4.2 | Microbenchmarks for libice0 and libicen (time in ms)                 | 117 |

## **List of Acronyms**

ABI Application Binary Interface AES Advanced Encryption Standard

AES-NI Advanced Encryption Standard New Instruc-

tions

AIK Attestation Identity Key

AMT Active Management Technology API Application Programming Interface

BIOS Basic Input/Output System

CA Certificate Authority

CMOS Complementary Metal Oxide Semiconductor

CPU Central Processing Unit

DMA Direct Memory Access

DRM Digital Rights Management

DRTM Dynamic Root of Trust for Measurement

EPT Extended Page Table

HSM Hardware Security Module

I/O Input/Output

IOMMU Input/Output Memory Management Unit

IPC Inter-Process Communication

LOC Lines of Code LPC Low Pin Count

MAC Message Authentication Code

xx \_\_\_\_\_\_LIST OF ACRONYMS

MMU Memory Management Unit MTM Mobile Trusted Module

NVRAM Non-Volatile Random Access Memory

PAL Piece of Application Logic PCR Platform Configuration Register PMA Protected-Module Architecture

PUF Physical Unclonable Function

RAM Random Access Memory

rPUF Reconfigurable Physical Unclonable Function

RSA Rivest Shamir Adleman

SHA Secure Hash Algorithm SLB Secure Load Block

SMI System Management Interrupt SMM System Management Mode SPI Serial Peripheral Interface SPM Self-Protecting Module

SRNG Secure Random Number Generator SRTM Static Root of Trust for Measurement

TCB Trusted Computing Base

TOCTOU Time-of-Check Time-of-Use

TPM Trusted Platform Module

TXT Trusted Execution Technology (a.k.a. LaGrande

Technology)

UPS Uninterruptible Power Supply

VM Virtual Machine

VMM Virtual Machine Monitor

### Chapter 1

### Introduction

As of January 1, 2014, the International Tennis Federation allows tennis players to use Player Analysis Technology (PAT) [58]. This will make the sport significantly more technological, far exceeding Hawk-Eye, the ball-tracking software that is already in use at some big tournaments. By incorporating motion sensors in tennis rackets [59], for example, coaches can analyze the force the tennis ball is hit with, its average position on the racket, etc. and use this information to better instruct their players. However, if this data falls in the hands of the player's opponent, signs of fatigue of certain muscle groups may also be deduced from it and give an unfair advantage.

Player Analysis Technology is only one of many examples of how our society increasingly relies on (the security<sup>1</sup> of) computing devices, even in case of seemingly low-tech undertakings such as playing tennis. Other examples include smartcards that support over-the-air updates, programmable sensor-networks, setup boxes and internet-connected TVs. Also infrastructure critical to our society depend on software. SCADA (Supervisory Control And Data Acquisition) systems are used to detect line voltage and take parts of our electrical grid online and offline. They also control water flow and pipe pressure of our water system and have many other critical applications. Of course also more obvious examples can be added to this list, such as online banking, e-government and cloud computing where multiple, mutual distrusting virtual servers execute on the same physical server.

As these devices are increasingly becoming interconnected and support

<sup>&</sup>lt;sup>1</sup>In this dissertation we will following the definitions of terms (e.g., security, safety, system, etc.) of Avizienis et al. [9] as much as possible but make an exception for standard terminology (e.g., type safety, memory-safe language, etc.).

2 \_\_\_\_\_\_ INTRODUCTION

software extensibility, the chances of them being successfully exploited increase significantly. This raises important research questions. How can we protect sensitive information from falling into the wrong hands? What architectural support is required to provide strong security guarantees while supporting interconnected, extensible devices? How can we deal with software extensions of stakeholders that do not necessarily trust one another? How do we deal with legacy software in such a system that may be vulnerable to attacks? Can we reduce the impact that such vulnerabilities can have?

To situate work accomplished during this PhD, we start this chapter with a brief overview how software can be attacked and which kind of security measures already exist. In Section 1.3 we discuss why, in spite of a large body of security measures, software vulnerabilities are still exploited daily. Next, we discuss the core idea of "Protected-Module Architectures" (PMAs), a promising novel research direction, and give a short overview of our own contributions to this area of research (Sections 1.4 and 1.5). Finally, we give a short overview of independent research results by industry and give an overview of the remainder of this dissertation text (Sections 1.6 and 1.7).

Readers already familiar with low-level software security may want to skip to Section 1.3.

### 1.1 Attacking Software

Recent advantages in artificial intelligence show very interesting results. Many will remember IBM's Deep Blue computer defeating reigning chess champion Garry Kasparov in 1997 [55]. Or, more recently, IBM's Watson computer winning a game of "Jeopardy!" in 2011 [45]. While the hardware capacity of Deep Blue and Watson were impressive (at least at their time), they architecturally don't differ that much from an average laptop or mobile phone; the hardware only accepts simple, basic instructions such as fetch the memory contents at address x, add the contents of register r1 and r2, etc.

Artificial intelligence emerges from how these basic instructions are combined. Writing these hardware instructions directly by hand would be a very tedious and error prone task. Instead, applications are written in a programming language that provides the programmer with a much more abstract representation of the platform. She can, for example, specify that the code requires a square board of 8 by 8 without having to specify exactly where it needs to be stored in memory. Moving a pawn can then be represented as swapping the contents of two memory cells. Deep Blue's software uses such more abstract views of the game and computes all possible steps that can be taken (to a certain limit)

TTACKING SOFTWARE

starting from the current setup of the chess board. Next it analyses and grades every resulting setup and finally outputs the step leading to the best outcome.

Software written in a programming language cannot be understood directly by a processor. First, it needs to be passed to another application, the compiler, that will translate the source code to machine instructions.

Vulnerabilities can originate at any level of this development process. A programmer can make a mistake when, for example, implementing the allowed steps a pawn may take. Or the compiler may have been written incorrectly, causing the application to sometimes behave incorrectly. Or even the hardware itself may be faulty. Not every programming mistake may be exploitable for attack. Certain bugs may only lead to undesirable side-effects such as a chess game that allows players to make illegal moves. Others are more severe and enable attackers to gain complete control over the application; they may be able to inject their own code inside the application and force its execution. This may lead to a large set of capabilities ranging from overwriting high scores of a chess game, to inspecting and modifying files on disk and even to operating the webcam without the user's knowledge.

**Buffer Overflows.** One of the most notorious software vulnerabilities are buffer overflows. According to the NIST National Vulnerability Database [86], the percentage of buffer overflow vulnerabilities of all vulnerabilities in publicly available software reported, increased dramatically from a mere 2.13% in 2006 to 15.95% in 2011. Since then the percentage of reported vulnerabilities dropped slightly to 12.10% for the first quarter of 2014.

Buffer overflows occur when a program tries to write past the boundaries of a memory buffer. Just as an overflowing bucket of water may cause a nearby electrical circuit to shortcut, the application may exhibit unexpected behavior. In general there are two possible attack targets. Most commonly, an attacker will attempt to overwrite control flow data. By, for example, overwriting the memory location containing the return address of a function – the address where execution should be resumed after the function completed – an attacker is able to redirect execution to her own injected code.

A second attack target is non-control data. Such attacks do not attempt to force the execution of injected code, but overwrite data stored by the application. Obvious targets of this kind of attack are variables keeping track of which user is logged in. Once data has been overwritten, the application executes normally, but operates on incorrect data, possibly giving users elevated privileges. 4 \_\_\_\_\_\_INTRODUCTION

Figure 1.1: The NIST National Vulnerability Database [86] reports a significant increase in the portion of buffer overflow vulnerabilities in publicly available software since 2006. In 2013 (the last full year figures are available of) they accounted for 14.6% of all software vulnerabilities reported.

**Buffer Overreads.** Data does not always have to be overwritten to cause security issues. Early 2009, we demonstrated [122] that buffer overreads are a realistic threat. While similar to a buffer overflow, during a buffer overread attack data is only read passed the bounds of a memory region, it is *not* overwritten. Passing unintended data to an attacker may be a security issue for two reasons: (1) valuable information may be deducible from the data leaked and used to bypass security measures relying on the secrecy of memory [13, 32, 33], or (2) the outputted information itself can be sensitive such as passwords or cryptographic keys belonging to different users of the application.

Probably the most well-known example of the latter is Heartbleed. This buffer overread vulnerability was discovered in the OpenSSL library [28, 83] and disclosed on April 7, 2014. The OpenSSL library is intended to guarantee integrity and confidentiality of network connections, but a missing bounds check could result in sensitive memory contents being leaked to an attacker. As private user information on a webserver, including login credentials, could be extracted and given the widespread use of the vulnerable library, the security incident received world-wide attention. Later it also became apparent that even private SSL keys may have leaked [48].

### 1.2 Existing Security Measures

Given the ever increasing dependence of modern society on software and the impact software vulnerabilities may have, a large body of security measures has been developed. To situate the research contributions of this PhD, we discuss here very briefly different areas of research. For a more elaborate overview, we refer the reader to other work [42, 146].

#### 1.2.1 More Secure Libraries

Programming languages such as C or C++ do not automatically store the size of allocated memory regions in memory. It is up to the programmer to keep track of this information. This is often cumbersome and simply omitted. Especially older library functions such as strcpy that copies a string (an array of characters) from one location to another, do not require a programmer to specify the maximum number of characters that can be copied. After buffer overflow vulnerabilities received more attention, such functions have since been updated. Older functions are still available for backward-compatibility reasons.

Interestingly enough, the "more secure" version is often still susceptible to a buffer overread. Consider, for example, strncpy that, contrary to its older and less secure variant, takes an additional argument specifying the length of the output buffer. While it prevents the destination buffer from overflowing, it does not guarantee that the newly written string is terminated by a ' $\0$ ' character. Most string functions, however, will rely upon this character to mark the end of the string and data located after the string in memory may be outputted to an attacker. It is unclear how often such vulnerabilities occur in practice.

### 1.2.2 Hardening Legacy Software Automatically

Writing software is a very time-consuming undertaking. Hence, one important line of research focuses on minor compiler or operating system updates to harden possibly vulnerable software. Such research proposals do not remove the vulnerabilities at hand, but they prevent that vulnerabilities can be exploited or, at least, significantly raise the bar for attackers.

One class of security measures tries to detect that a buffer overflow has taken place. StackGuard [32,33] and ProPolice [44] take this approach and are two of the most widely applied security measures against buffer overflows. StackGuard enables the detection of a stack-based buffer overflow by placing a random value, called a *canary*, before sensitive control data on the stack. A buffer overflow

6 \_\_\_\_\_\_INTRODUCTION

trying to overflow the return address of the current function, will also overwrite the canary. By checking the integrity of the canary before returning from the current function, a buffer overflow attack may be detected and the application can be stopped before any harmful event can occur.

ProPolice [44] operates similar to StackGuard but also re-orders local variables, avoiding that a buffer overflow can overwrite valuable data such as pointers before the canary is overwritten.

Other security measures defending legacy software do not try to detect buffer overflows, but make it significantly more difficult to execute attacks successfully. Address Space Layout Randomization (ASLR) [13], one of the most applied security measures of this class, randomizes the memory layout of applications at launch-time. Every time an application is started, different memory locations are assigned to valuable data. This does not prevent buffer overflows, but makes it much harder for an attacker to overflow a buffer with sensible data. Redirecting control flow, for instance, is much harder as the location of injected code at runtime is unknown to the attacker.

StackGuard, ProPolice and ASLR rely on the memory secrecy assumption: an attacker cannot read unintended memory contents prior to an attack. But in the event of a buffer overread this assumption does not always hold [122]. Data or code pointers may leak to the attacker and enable her to derandomize the memory layout.

Multistack [148] takes another approach without relying on the memory secrecy assumption. It partitions the program stack into multiple stacks, separating likely attack vectors (e.g., buffers of characters) from likely attack targets (e.g., return addresses or function pointers). Using hardware memory protection, it avoids that a buffer overflow on one stack can overflow onto another. Benchmarks show that multistack can be implemented with almost no overhead on x86 processors. In 2010 we evaluated Multistack on ARM processors and proposed some optimizations to reduce overhead on this platform as well [121].

### 1.2.3 Memory-Safe Languages

In the previous paragraphs we focused mainly on buffer overflow vulnerabilities because they are the most exploited type of low-level software vulnerabilities. But also other memory errors exists such as double freeing an allocated memory region or dereferencing a pointer after it has been freed. Such vulnerabilities can occur in older languages (e.g., C and C++) because they rely on the programmer to avoid such errors. Failure to comply may result in security vulnerabilities.

Detailed knowledge of the application, compiler, linker and operating system is required to determine whether these vulnerabilities are practically exploitable.

Most modern languages such as Java, C#, Haskell and OCaml, avoid such vulnerabilities altogether by relying on a sound type system. Before a Java application is compiled, for example, it is checked that it complies with the type system at hand. Errors such as writing to a memory region before it is allocated, will be detected before the application can be executed. Other errors such as writing past the bounds of an array, are more difficult to detect at compile time and dynamic checks are inserted.

While memory-safe languages are clearly superior in terms of security, non-memory-safe languages are still widely used. For instance, the C programming language is still the most widely used language according to the TIOBE Programming Community [130]. The reason for this is threefold: (1) Many legacy applications and libraries are written in C and form the base for newer versions. Rewriting them in a memory-safe programming language usually is not economically viable. (2) While many languages have clear advantages from an academic point of view, they require a different thought process and highly-skilled programmers in these languages are hard to find. (3) Operating systems or other applications require close interaction with the hardware. This is much easier to accomplish in low-level languages such as C. Moreover, some low-end devices are significantly resource constrained and the increased performance, memory and energy costs of memory-safe languages may not be acceptable.

#### 1.2.4 Software Verification

The use of a memory-safe programming language can avoid exploitable memory-error vulnerabilities in an application. But also other implementation errors may enable successful attacks. Insufficient input validation in a web application may lead to SQL injection or Cross Side Scripting (XSS) attacks. Use of unsanitized user-provided paths may enable an attacker to traverse the entire file system and access sensitive files. Or unexpectedly large input data may cause the application to stop responding.

Such vulnerabilities (as well as memory errors) can be detected using formal software verification. Tools aiding in formal verification, enable programmers to specify key properties of the application and guarantee with mathematical certainty that they always hold. Unfortunately formal verification of even simple applications can only be done by highly-skilled users and is very time consuming. Verification of large applications is almost infeasible in practice. Instead, significant assumptions are often made such as that a library always

8 \_\_\_\_\_\_ INTRODUCTION

behaves correctly or that the underlying operating system cannot be attacked. Nonetheless, verification tools such as VeriFast [60] and VCC [29] are promising.

#### 1.2.5 OS Protection Features

In practice an attacker may be able to gain access to a computing system in two ways. Either a vulnerable application could be exploited, or the user can be tricked into executing the attacker's provided code (e.g., by sending her an obfuscated executable via e-mail). Security measures need to be taken to ensure that once an attacker gained execution privileges on the platform, she does not have full control over the system. Two important features of modern operating systems play a key role, with limited success.

First, the introduction of protection rings significantly increased security. Protection rings enable a strict separation between the kernel – the more privileged piece of software that can directly access hardware such as the hard disk and decides which application can run – and applications that take advantage of hardware abstractions provided by the kernel. If a user-level application attempts to issue an instruction that requires kernel privileges, this will cause a trap to the kernel where it will be handled accordingly (e.g., by terminating the application). Similarly, the hardware will prevent a user-level application from accessing kernel memory directly. The kernel can only be accessed using a specific interface of system calls that it provides. Using this separation of protection rings, applications can also be isolated from one another; an attacker who successfully attacked an application is not able to directly read or write memory locations belonging to another process.

The arrival of protection ring hardware sparked the question of what should be included in the kernel and what should execute at user-level.<sup>2</sup> A number of different operating system architectures have been proposed, but most fall in one of two groups. One group, the monolithical kernels, implement process isolation, memory management, device drivers, etc. in the kernel. The other group, the microkernels, only implement a minimal amount of features at the highest privilege level. Components such as memory management and device drivers are offloaded to services executing at user-level. While this has clear advantages from a security perspective, most modern operating systems are monolithical systems. We elaborate further on microkernels in Appendix B.

Second, the operating system is able to define an access control policy on resources. While most computing devices today are truly *personal* computers,

<sup>&</sup>lt;sup>2</sup>Some researchers even proposed the use of more than two privilege level. The influential MULTICS operating system [52], for example, called for 64 privilege rings.

most devices used to be shared. Hence, there was a need to prevent files belonging to one user from being accessed by another. This sparked the development of access control policies which are widely implemented. Unfortunately most applications today execute with full user privileges and an attacker who exploited such an application can access all the user's files, even if access to those files is not required for the correct working of the application.

#### 1.2.6 Hardware Security Modules

Some applications require extremely strong security guarantees. For instance, private cryptographic keys used to sign government-issued electronic identity cards or website certificates must not, under any circumstances, leak to an attacker. To protect such high-value data, they are often stored in a hardware security module (HSM). These secure co-processors protect sensitive data against two types of attacks. First, to protect against software attacks, they only provide limited functionality and usually do not allow third-party code to run on its processor. Untrusted software running on the main processor can only access the HSM via a secure interface that prevents unintended behavior. An HSM, for example, may provide an interface to create and use cryptographic keys (e.g., to sign certificates), but should prevent that cryptographic keys can be exported from the HSM in plaintext.

Second, security measures are taken to prevent hardware attacks against the HSM. While software attacks are often the easiest attacks to execute – and thus usually the preferable option for attackers – there may not be any exploitable vulnerability in the software of the HSM. In such situations a determined attacker may target the HSM's hardware directly. Hardware attacks can be divided in two categories. In invasive attacks the hardware chip is directly physically accessed. An attacker may, for example, ground signals preventing correct execution of instructions. Invasive attacks do not always actively modify the behavior of the chip. In passive attacks of this category data buses may be probed to intercept sensitive information that pass over them. A variety of countermeasures exist to defend against invasive attacks, ranging from covering hardware components in epoxy making them harder to access to continuous monitoring the integrity of a protective mesh over the chip.

Non-invasive attacks on the other hand, preserve the chip's physical integrity. Passive attacks in this category only monitor information that can be observed externally such as timing differences, power consumption or electromagnetic radiation. When this information can be correlated with the internal state of the chip, sensitive information may leak to an attacker. An attacker may however also actively modify the chip's physical environment. Providing spikes in the

10 \_\_\_\_\_\_INTRODUCTION

power supply, for example, may cause unintended behavior of the chip and (indirectly) leak sensitive information. Sensors onboard the chip may mitigate such attacks.

To boost security of commodity computing devices, most modern desktop and laptops are also equipped with an HSM, called the Trusted Platform Module (TPM). While this chip is very resource constrained and operates at very low speeds, it has a number of interesting security primitives. We briefly discuss some of these primitives we will use throughout the text but refer to other work for a more elaborate discussion [49,76,95].

**Platform Configuration Registers.** One of the key components of the TPM chip are its Platform Configuration Registers (PCRs). PCRs are a set of registers that can be used to securely collect the state of the platform. To ensure that malicious software cannot tamper with the contents of PCR registers, they cannot be set to a specific value. A  $PCR_i$  can only be extended with measurement m by hashing its current content appended with m:

$$PCR_i^{new} \leftarrow SHA-1(PCR_i^{old}||m)$$

There are two types of PCR registers. Static PCRs are initialized to 0 at boot time and cannot be reset afterwards. Dynamic PCRs, in contrast, are set to -1 at boot time and can be reset to 0 after the system booted. The different initial values enable a third party to distinguish between reboots and PCR resets.

To collect the state of the platform, every component in the boot process first computes the hash of the next boot component, extends a PCR register with the result and only then hands over control. Modification of one of these components, for example to provide a persistent backdoor to an attacker, will result in a different PCR value. Hence, when PCR content remains unchanged, the system has booted to a pristine state.

**Attestation.** In a number of use cases it is desirable that a user can prove certain properties to a third party. Employees connecting to a company network, for example, may need to prove that their operating system was not compromised and runs the latest software updates. Or users of a public network may need to prove that they run an up-to-date anti-virus scanner. The TPM chip can be used to provide such attestations; the TPM chip can sign the contents of one or more PCR registers that can be presented to the third party. As the used private key cannot be extracted from the TPM chip and PCR contents cannot be set to a specific value by an attacker, this attests the state of the platform.

**Sealed Storage.** Sensitive data can also be tied to a specific state of the platform. Software can provide sensitive data to the TPM chip and request that it is sealed to the contents of one or more PCR registers. The resulting ciphertext can be stored at an untrusted location. Only when the systems enters a state where PCR content matches the specified value at the time of sealing, will the TPM decrypt the ciphertext.

**NVRAM.** Sensitive data can also be stored in TPM NVRAM based on PCR contents. Unfortunately TPM NVRAM has significant drawbacks. Most TPM implementations only provide 1,280 bytes of non-volatile memory and support only 100,000 write operations. Accessing TPM NVRAM every second would wear it out in less than 28 hours.

**Monotonic Counters.** Finally, TPM chips are also shipped with at least 4 monotonic counters; these are counters that can be incremented but never decremented. Unfortunately, the TPMv1.2 specification [132] only requires these counters to be incrementable at least once every 5 seconds. TPM vendors may provide increments at higher speeds but counters must not wear out within 7 years of operation.

### 1.3 Why Software Security Is Still a Mess

The security measures presented in Section 1.2 all seem promising. But users are still presented with daily software updates to patch vulnerable systems and have the impression that "everything can be attacked successfully." Why is the state of software security in practice so bad?

One could argue that software security is still a very young field, especially when compared to medicine or physics, and that software security will increase automatically over time when programmers are becoming better educated. While this may be the case for some type of vulnerabilities, it is unlikely that it will stop all attacks. Some vulnerabilities are just too subtle and too easily overlooked, especially when under time pressure.

Development of security measures, combined with better education, may provide better chances of success. In order to get widely adopted, security measures should meet some key properties:

• Easily Applicable: Software security measures need to be easy to apply by users and developers. Security measures that hinder users in their daily

12 \_\_\_\_\_\_INTRODUCTION

operations, will simply be disabled. Similarly, developers won't apply a security measure if it is too cumbersome. Software verification is a prime example of such a security measure; formally proving that software meets some security property is non-trivial and too time costly.

- Limited Overhead: Security measures that significantly impact the performance, memory usage or energy requirements, may not be suitable for widespread deployment. For instance, security measures exists that remove all buffer overflow vulnerabilities of an application by adding bounds checks. However, due to their huge performance overhead (PAriCheck [147] and Baggy Bounce [5] pose a 49% and 60% performance overhead respectively on the SPEC2000int benchmark), they are not widely deployed.

- Evolutionary: Writing software is a labor-intensive undertaking. Only in extraordinary cases will existing software be discarded and re-implemented to provide stronger security guarantees. Successful security measures such as StackGuard, ProPolice and ASLR can be applied to fortify most legacy software or simply be disabled for non-compatible applications.

- Effectiveness: The cost users and software vendors are willing to pay for increased security, naturally also depends on the effectiveness of the applied security measures. Unfortunately, most security measures rely on a huge Trusted Computing Base (TCB) the hardware and software that needs to be trusted upon especially when applied on commodity computing devices equipped with a huge monolithical kernel such as MS Windows or Linux. The security guarantees that such security measures can provide is thus also limited.

- Gain a Critical Mass: Software vendors are usually hesitant to apply newly developed security measures. Their impact on legacy software may not yet be clear and long-term support may be uncertain. Especially switching to another, more secure language is a risky undertaking; without widespread adoption, the language compiler and runtime environment may not be maintained in the future and skilled developers may be hard to find. The decision is also hard to revert in the future.

To minimize overhead, security measures are often specifically tailored to a very specific type of vulnerability (e.g., stack-based buffer overflows). Other types need to be addressed by applying additional countermeasures. The hope is that by stacking security measures, the bar is raised so high for attackers that successful exploits are infeasible. Unfortunately the sheer size of the codebase that needs to be protected makes this approach unlikely to succeed. The number of vulnerabilities that are exploited on a daily basis, are a direct result.

# 1.4 A New Deal:<sup>3</sup> Protected Module Architectures

Software vendors and system administrators could continue to add newly developed security measures to computing devices, raising the bar for attackers ever higher. While this would make attacks more challenging to execute, it is unlikely that this approach will ever be able to provide provably strong security guarantees. Protected-Module Architectures (PMAs) provide a viable alternative.

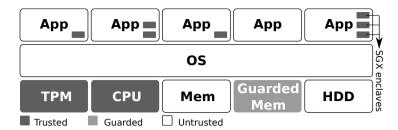

**Concept.** In 2008 McCune et al. proposed [78] a radical new research direction based on two observations. First, modern monolithical operating systems provide process isolation primitives, but the kernel is too large to be implemented free from vulnerabilities. Moreover, its continuous extension to support new file systems, process scheduling algorithms and new peripherals generates a snowball effect of an ever growing TCB. Both properties make formal verification not only infeasible, it would pose a huge barrier for third-party vendors to develop new kernel services as they too would need to be formally verified. In order to provide strong security guarantees to applications running on commodity computing devices, a novel isolation approach is required that avoids the pitfalls of common monolithical kernels.<sup>4</sup>

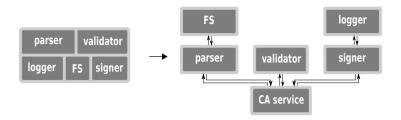

Second, not all components of an application are security sensitive and a vulnerability in one compartment should not affect security of another. For instance, a vulnerability in a component that parses incoming messages or that collects and sends memory dumps when the application crashes, should not affect the secrecy of the cryptographic key used by a component providing an encryption/decryption service. Isolation of sensitive parts of an application can lead to limited-sized components that can provide strong security guarantees as they are mostly self-contained; they only need to place limited trust in services provided by other parts of the application or the operating system. They are still dependent on the kernel to eventually receive allocated CPU time or get access to files, but failure to provide these services does not necessarily break required security properties. For instance, files could be integrity and version protected

<sup>&</sup>lt;sup>3</sup>The term "New Deal" refers to a series of measures taken by US Congress and President Franklin D. Roosevelt in response to the Great Depression of the 1930s [14]. They focused on Relief, Recovery, and Reform. Given the poor state of security of high-end computing devices and even more so of low-end, embedded devices, society is also in need of a "new deal" regarding system security.

<sup>&</sup>lt;sup>4</sup>Microkernels largely avoid these pitfalls already by minimizing the amount of services running at kernel-level. The seL4 microkernel even has been formally verified completely [64]. However, virtually all commodity applications run on top of monolithical kernels and attempts to rebuild them into microkernels have largely failed. In Appendix B we discuss the similarities and differences between Protected-Module Architectures and microkernels in more detail.

14 \_\_\_\_\_\_INTRODUCTION

before they are passed to the operating system for storage. Kernel-level malware may then corrupt stored files, delete them or replay old versions, but sensitive information cannot leak. Similarly, an attacker who gained kernel-level access, may simply stop security sensitive components from being scheduled or prevent the system from ever resuming normal operation after it rebooted.

Based on these observations, McCune et al. proposed a novel protection mechanism. It enables module vendors to provide strong security guarantees while relying only on a limited and stable set of primitives – additional primitives will not need to be added in the future. In contrast to many existing security measures, the protection mechanism does not assume that the system started in a pristine state. An attacker may already have gained access to the highest privilege levels. Only the provided primitives must not be subvertible. Security architectures that follow a similar reasoning have since become known as "Protected-Module Architectures" (PMAs).

Which security primitives are presented to modules depends on the implementation of the PMA, but all ensure two vital properties. Most importantly, protected modules are in complete control of their own security. They are completely isolated from the rest of the system, including from other modules. Malware executing at any privilege level cannot directly access modules' memory content.

Given that an attacker may have infiltrated to the highest privilege levels of the system, modules may have been compromised before they could be protected. In such cases PMAs must ensure that an attacker does not gain any additional power. Their security primitives guarantee that (1) the compromised module cannot access previously stored secrets and (2) the module will fail to attest its correct execution to a (remote) verifier.

Flicker. In the same work [78] McCune et al. also presented Flicker, a prototype of such a protected-module architecture. Flicker relied heavily on the security features provided by the TPM chip and the late launch feature of the then recent AMD processors.<sup>5</sup> A late launch was designed to securely start a hypervisor or a security kernel. When issued, a late launch provides a Secure Load Block (SLB) as parameter. This code and data chunk will receive control after the late launch. To prevent software attacks against the SLB, a late launch sequence disables interrupts, prevents direct memory access (DMA) to the SLB and disables debug access. Virtual memory is disabled as well. To tie TPM features to the provided SLB, the TPM's dynamic PCR registers are reset and PCR 17 is extended with the measurement of the SLB.

<sup>&</sup>lt;sup>5</sup>Intel processors provide with Trusted eXecution Technology (TXT) similar capabilities.

Flicker uses a late launch sequence to completely isolate sensitive parts of an application, called Pieces of Application Logic (PALs) by its authors, from the rest of the system. As a result, PALs are short-lived. Every time a PAL is called, it needs to marshall all required inputs and initiate a late launch to start the PAL's execution. Afterwards normal, untrusted execution is resumed and the PAL's output can be unmarshalled. When required, PALs can seal sensitive data for the next invocation of the same or another PAL.

Flicker's merit is that it is able to provide provable security properties by applying existing security-hardware primitives in a completely new way. Unfortunately, since these primitives were never designed for such use cases, they incur some significant disadvantages. First, development of PALs is a challenging undertaking, especially when state needs to be maintained between invocations or shared between multiple PALs. Special care may also have to be taken in such cases to ensure that an attacker cannot replay messages. The fact that PALs cannot access the legacy application's memory region, complicates their development as well. While some inputs may be marshalled/unmarshalled easily, this is definitely not always the case, for example, when a PAL needs to access a graph stored in unprotected memory.

Second, Flicker incurs a significant performance overhead. Issuing a late launch sequence for every PAL invocation and accessing the TPM to retrieve previously stored data, makes Flicker unsuitable to protect sensitive parts of performance-critical applications. However, it must be noted that this overhead only occurs when crossing PAL/legacy-code boundaries. Execution of legacy applications is not affected.

Third, Flicker takes advantage of complex hardware. Their power and energy requirements makes its approach infeasible for low-end applications such as sensor networks.

Research Questions. Despite Flicker's drawbacks, it showed to be a very promising research direction. It finally demonstrated how strong security guarantees could be offered to applications running on huge monolithical operating systems while only relying on an extremely limited software TCB of 250 lines of code. This lead to a number of research questions. Some of them have been (partially) answered during this doctoral work, others are still open for further research.

• What is the minimal set of security primitives required? We have proposed a novel program-counter-based access control mechanism [120] that provides strong isolation and enables lightweight inter-module communication (see also Chapter 2). Later we added a new primitive:

16 \_\_\_\_\_\_INTRODUCTION

state-continuous execution [116, 117] that guarantees that even in the event of unexpected crashes or power failure, an attacker cannot roll back a module's state (see Chapter 4). We expect that this set of primitives may be reduced further. State-continuity support for example may only require access to an attestable, monotonic counter.

- Can PMAs suitable for low-end devices be developed? Noorman et al. [87] showed that the proposed program-counter-based access control mechanism can be implemented efficiently in hardware and used in low-end applications such as sensor networks.

- Which security guarantees can PMAs offer? How can these be verified? Agten et al. [4] and Patrignani et al. [96,98] showed how protected modules can be compiled to protected-module architectures without introducing potential software vulnerabilities. As a result protected modules can only be attacked at assembly-level when a related attack exists at source-code level. Later Agten et al. [3] also presented work on how protected modules can be verified at source-code level.

- How can PMAs communicate securely with peripheral devices, including screen and keyboard? This is still an open research question. See Section 5.2.1 for more details.

- Can availability properties be guaranteed to PMA architectures? This is also still an open research question. Section 5.2.1 also provides more details on this topic.

# 1.5 Building Secure Subsystems: Contributions to the Research Area

McCune et al.'s approach finally provides verifiable security guarantees to isolated PALs executing op top of an untrusted legacy operating system. This dissertation focused on the problem of developing secure subsystems using the same core principle. Such subsystems are much more complex. Consider as an example a secure payment framework. Application vendors must be able to connect to a single payment module that in turn connects to the payment system of the user's bank or selected payment method. Multiple stakeholders are involved in such a system that do not necessarily trust one another. An application vendor using the payment subsystem requires strong security guarantees that the user transferred the correct amount. Financial institutions may want to provide their own payment module without placing

trust in modules of other vendors. Building such subsystems is very challenging as modules cannot be merged.

We present here an overview of our contributions in this research area. We refer the reader to one of the thesis chapters when work has been incorporated in full, or to the published papers.

Self-Protecting Modules: A Noval Isolation Approach. At the beginning of 2010 we came up with a novel isolation mechanism [120]. Unlike Flicker, it does not rely on short-lived modules. Instead, protected modules are treated as "black boxes" by untrusted components; modules execute in the same address space as the rest of the untrusted application, but cannot be accessed from outside the module. They can only be called through an explicit interface and maintain their state between invocations. Obviously, the services themselves do have full access to their own memory locations. This includes the exclusive right to disable their own protection, after the required security measures have been taken to prevent sensitive information from leaking to unprotected memory. Hence the name "Self-Protecting Modules" (SPMs).

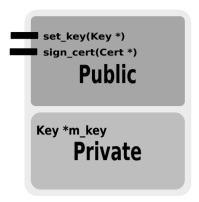

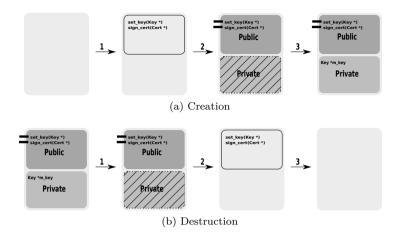

To guarantee these isolation properties, a program-counter-based access control mechanism was developed. Depending on the value of the program counter (i.e., the location of the currently executing instruction) different access rights are enforced. Obviously, when the program counter points inside an SPM, instructions have more privileges to the SPM's memory region than when we are executing untrusted code outside the module.

Next to the separation between unprotected memory and the SPM, the SPM itself is also divided into two<sup>6</sup> sections. Code implementing the module's services, is placed in the Public section. This section is read-accessible from unprotected memory, but can only be entered via specific entry points. The other section – the Secret section – contains security-sensitive information (e.g., cryptographic keys and the call stack). It is only accessible when executing within the SPM's boundaries.

**Secure Inter-SPM Communication.** Next to enabling strong isolation of protected modules, the program-counter-based access control mechanism has a second strong property: It enables the easy creation of secure channels between

<sup>&</sup>lt;sup>6</sup>The original paper [120] presented a solution using three sections: SEntry, SPublic and SSecret. Follow-up work simplified this setup and replaced the SEntry section with entry points to the SPM. To avoid confusion, we present here the simplified setup which will also be used throughout this text.

18 \_\_\_\_\_\_INTRODUCTION

modules. Even when an attacker gains kernel-level access to the system, integrity and confidentiality of messages exchanged is guaranteed.

SPMs can be authenticated in two steps. First, the world-readable Public section of the SPM is compared to a stored hash value. As the Public section cannot be modified after the module's protection is enabled and it is the only executable section, it prevents SPMs from masquerading their behavior. The access right restrictions guarantee to the caller which code will be executed. In the second step, the layout of the SPM is checked. Containing the correct executable code is not sufficient. Modules with an incorrect layout (e.g., a too short Secret section) may use unprotected memory to store sensitive information. When both checks succeed, the SPM is authenticated and can be called securely by jumping to one of its entry points. Since messages cannot be intercepted and are always delivered, this provides another important building block for secure subsystems.

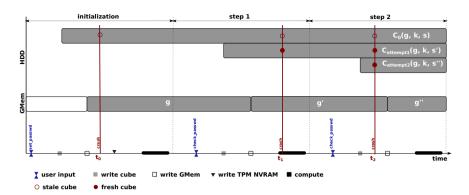

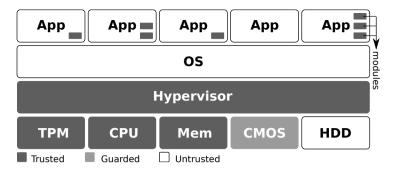

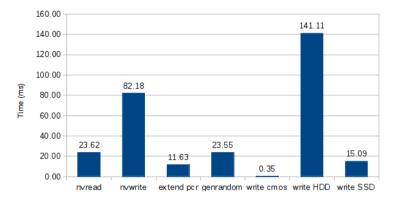

Early work [87,119,120] exposed a public interface to untrusted code. While SPMs are in full control over the sensitive information they store internally, exposing insecure interfaces may still present a major security risk. An SPM implementing a signing service, for example, may guarantee that its private key will never leak to the outside world. When this SPM can be called from unprotected code however, an attacker can still request arbitrary data to be signed.