## ARENBERG DOCTORAL SCHOOL Faculty of Engineering Science

# Differential Scan-Based Side-Channel Attacks and Countermeasures

Secure Design-for-Testability (DfT) for Cryptographic Circuits

### **Amitabh Das**

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor in Engineering

# Differential Scan-Based Side-Channel Attacks and Countermeasures

Secure Design-for-Testability (DfT) for Cryptographic Circuits

#### **Amitabh DAS**

Supervisory Committee:

Prof. dr. ir. Pierre Verbaeten, chair

Prof. dr. ir. Ingrid Verbauwhede, supervisor

Prof. dr. ir. Wim Dehaene

Prof. dr. ir. Bart Preneel

Prof. dr. ir. Nele Mentens

Prof. dr. ir. Bruno Rouzeyre

(LIRMM, University of Montpellier (UM2),

Montpellier, France)

Ir. Erik Jan Marinissen, PDEng

(Principal Scientist, IMEC, Leuven, Belgium)

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor

in Engineering

© KU Leuven – Faculty of Engineering Science Kasteelpark Arenberg 10, box 2452, B-3001 Heverlee (Belgium)

Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt worden door middel van druk, fotocopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever.

All rights reserved. No part of the publication may be reproduced in any form by print, photoprint, microfilm or any other means without written permission from the publisher.

D/2013/7515/121 ISBN 978-94-6018-736-0

### **Preface**

This PhD thesis is about secure testing of cryptographic hardware. Security and testability are two conflicting goals that are difficult to achieve simultaneously. The purpose of this dissertation and my PhD research has been mainly to address this conflict, while at the same time creating feasible low-cost solutions that can be implemented in real applications.

I would like to express my sincere gratitude to Prof. Ingrid Verbauwhede for giving me the opportunity to pursue research at the COSIC group of KU Leuven. Her guidance and encouragement in these four years have been instrumental in architecting my PhD. I would also like to thank my assessors, Prof. Wim Dehaene and Prof. Bart Preneel for giving their insights and asking stimulating questions during the course of my PhD research that has helped in further improving this work. I would also like to acknowledge my other jury members, Erik Jan Marinissen at IMEC, Prof. Nele Mentens, and Prof. Bruno Rouzeyre from LIRMM, Montpellier, France, for their improvement suggestions and support. My collaboration with Prof. Rouzeyre's research group at LIRMM and joint work with my co-author, Jean Da Rolt, helped a lot in developing my PhD research. I also acknowledge my other co-authors, especially Baris Ege, Santosh Ghosh and Stefaan Seys, for their efforts in our joint publications.

I am thankful to Pela, our COSIC group secretary, for helping in the administrative process at KU Leuven, and in my personal problems during my PhD years. I am also grateful for the support of my colleagues at COSIC who have been kind to guide and help me in my research. This PhD would not have been possible without the continuous encouragement of my parents, my elder brother, and my wife, who have played a major role in building my career. I am really indebted to them for inspiring and motivating me all along my PhD.

Amitabh Das Leuven-Heverlee, Belgium, September 2013

i

### **Abstract**

Cryptographic circuits are vulnerable to various side-channel attacks that target their hardware implementations to extract secret information stored inside them. One such side-channel is the scan chain based Design-for-Test (DfT) infrastructure employed for thorough and faster testing of VLSI circuits. Removing the connectivity of scan chains after manufacturing test prevents such attacks, but also makes in-field test and updates of the circuits impossible. In some applications, such as set-top box decoders, the firmware updates happen through the JTAG port internally connected to the scan chains. Hence, scan chains must be left intact and at the same time protected from these attacks. Moreover, the cost in terms of area and test time overhead must be kept to a minimum to make it feasible to incorporate the security mechanism on a reasonably priced commercial product. This work first investigates the scan attack vulnerability of symmetric-key and public-key hardware implementations, and then presents suitable countermeasures to address the aforementioned trade-off between testability, security and test cost.

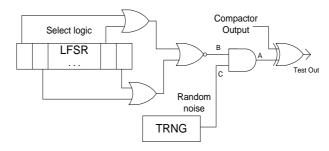

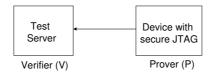

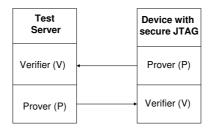

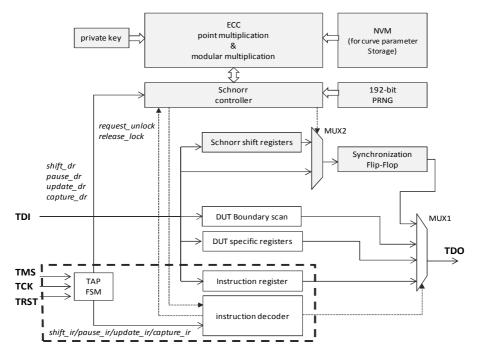

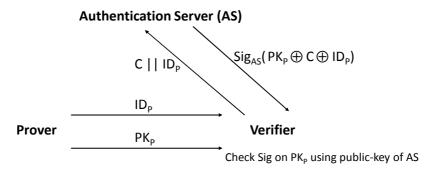

The thesis first presents scan attacks on hardware implementations of the symmetric-key block cipher AES and the public-key ciphers RSA and ECC in the presence of advanced DfT structures such as test compression and X-handling schemes. In addition, state-of-the-art power analysis side-channel and fault attack countermeasures are analyzed to evaluate whether they are suitable in warding off scan attacks. The thesis also investigates the practical security provided by various scan attack countermeasures (such as partial scan and scan chain scrambling) that are proposed in the literature. At the algorithmic level, blinding and randomization based schemes that protect against Differential Power Analysis (DPA) attacks are shown to be secure against scan attacks, whereas countermeasures against Simple Power Analysis (SPA) and Fault Attacks are found to be ineffective against scan attacks. At the Register Transfer level (RTL), Multiple Input Signature Register (MISR)-based time compaction schemes are found be inherently secure against scan attacks, provided only the final MISR signature is observable and not the intermediate states. New countermeasures are also proposed at the system level in the form of a secure JTAG architecture based on an ECC-based Schnorr Protocol and at the gate level in the form of a noise injector integrated with the

iv \_\_\_\_\_\_ Abstract

test compression schemes.

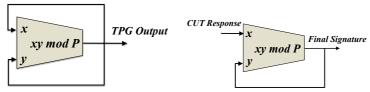

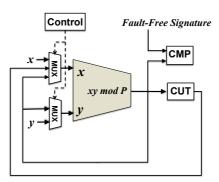

Another major contribution of the thesis is secure Cryptographic SoC Testing. As part of our research work, scan attack resistant Secure Test Wrappers (STWs) have been designed that integrate a challenge-response based secure entity authentication protocol with the IEEE 1500 standard Test Wrapper. Two variants of STWs are proposed; one based on a lightweight block cipher KATAN and the other using Physically Unclonable Functions (PUFs). Another work performed in this direction is integrating efficient multiplier-based pseudo-random Logic Built-In Self-Test (LBIST) solutions with STWs. This helps in providing a flexible self-testing option for the cryptographic SoC and maintaining a high level of testability and security, while simultaneously reducing the test overhead.

## Samenvatting

Cryptografische schakelingen zijn vatbaar voor verscheidene nevenkanaalsaanvallen met als doel de extractie van geheime sleutels die opgeslagen zijn in de hardware Eén van deze nevenkanalen is de "Design-for-Test (DfT)" infrastructuur die gebaseerd is op scan chains en gebruikt wordt voor uitgebreide en snelle functionele testen van VLSI schakelingen. Het verwijderen of uitschakelen van de scan chain interface na de testen tijdens productie maakt dit nevenkanaal onbruikbaar voor aanvallers, maar verhindert ook het verder testen en updaten van de schakeling in een latere fase. In sommige toepassingen, zoals bijvoorbeeld set-top boxen, gebeurt het updaten van de firmware via de JTAG poort die intern is doorverbonden met de scan chains. In deze gevallen is het dus niet mogelijk de scan chains uit te schakelen en zal op een andere manier bescherming moeten gezocht worden tegen aanvallen. Daarenboven zal de kost in termen van oppervlakte en extra doorlooptijd van de testen minimaal moeten gehouden worden om deze beveiligingsmechanismen in te kunnen bouwen in een commercieel product. Dit werkstuk start vanuit een onderzoek naar de gevoeligheid zowel symmetrischesleutel- als publieke-sleutel-implementaties in hardware t.o.v. scan-aanvallen. Daarna worden geschikte tegenmaatregelen voorgesteld om de bovenvermelde afweging tussen testbaarheid, beveiliging en kost aan te pakken.

Eerst wordt in deze thesis een beschrijving gegeven van scan-aanvallen op hardwareimplementaties van het symmetrische-sleutel-algoritme AES en de publieke-sleutelalgoritmes RSA en ECC. Er wordt verondersteld dat er geavanceerde DfT structuren

zoals test-compressie en X-handling in gebruik zijn. Daarnaast worden ook actuele

tegenmaatregelen tegen nevenkanaalsaanvallen gebaseerd op vermogensanalyse en

fout-aanvallen (fault attacks) geanalyseerd. Er wordt nagegaan of deze geschikt

zijn om scan-aanvallen af te weren. Deze thesis evalueert ook de effectiviteit

van verscheidene in de literatuur beschreven scan-aanval-tegenmaatregelen, zoals

partiële scans en scan chain scrambling. Op het niveau van het algoritme, wordt

aangetoond dat blinderen en schema's gebaseerd op willekeur ("randomization

schemes") die bescherming bieden tegen differentiële vermogensanalyse ook veilig

zijn tegen scan-aanvallen. Dit in tegenstelling tot tegenmaatregelen tegen

eenvoudige vermogensanalyse en fout-aanvallen (fault attacks) waarvan aangetoond

vi \_\_\_\_\_\_ Samenvatting

wordt dat ze geen bescherming bieden tegen scan-aanvallen. Op het RTL niveau wordt er aangetoond dat Multiple Input Signature Register (MISR) gebaseerde schema's inherent veilig zijn tegen scan-aanvallen, op voorwaarde dat enkel de laatste (en niet de tussentijdse) MISR handtekening observeerbaar is door de aanvaller. Ook worden er twee nieuwe tegenmaatregelen voorgesteld. Enerzijds op het systeemniveau: een veilige JTAG architectuur gebaseerd op het Schnorr protocol (gebruikmakend van ECC). Anderzijds op het poort-niveau ("gate level"): een ruis-injector die geïntegreerd werd met de test-compressie schema's.

Een volgende grote bijdrage van deze thesis zijn veilige cryptografische systeem-op-chip (SoC) testen. Als onderdeel van ons onderzoek werden scan-aanval-resistente Veilige Test Wrappers (VTW) ontworpen. Deze combineren een veilig authentiseringsmechanisme met de IEEE 1500 standaard Test Wrapper. Er worden twee varianten van de VTW voorgesteld: een eerste gebaseerd op het lichtgewicht blokcijfer KATAN en een tweede gebruikmakend van fysisch onkloonbare functies of PUF's (Physically Unclonable Functions). Hieraan gerelateerd werd ook gewerkt aan het integreren van efficiënte vermenigvuldiger-gebaseerde pseudo-willekeurige Logic Built-In Self-Test (LBIST) oplossingen met VTWs. Hiermee worden flexibele zelf-testen mogelijk voor SoCs met gewaarborgde beveiliging en beperkte kost op het vlak van tijd en oppervlakte.

## **Contents**

| Pi | erace  | 2       |                                                           | ı   |

|----|--------|---------|-----------------------------------------------------------|-----|

| ΑI | ostrac | ct      |                                                           | iii |

| Sa | ımen   | vatting |                                                           | v   |

| Cd | onten  | ts      |                                                           | vii |

| Li | st of  | Figures | 5                                                         | χv  |

| Li | st of  | Tables  |                                                           | xix |

| Li | st of  | Abbrev  | riations                                                  | xxi |

| 1  | Intr   | oductio | on and Background                                         | 1   |

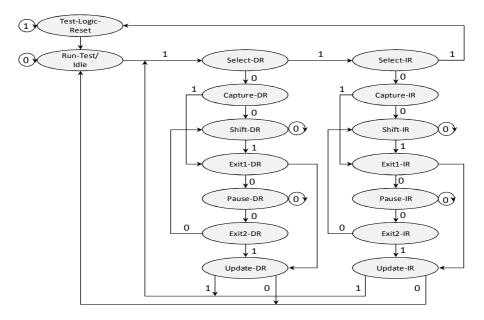

|    | 1.1    | Introd  | luction to Testing and Structural Testing                 | 3   |

|    |        | 1.1.1   | Structural vs. Functional Testing                         | 3   |

|    |        | 1.1.2   | Fault Models                                              | 4   |

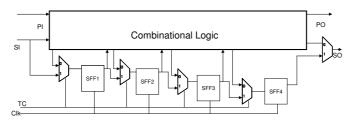

|    |        | 1.1.3   | Scan-Based Structural Design-for-Test (DfT) $\dots \dots$ | 4   |

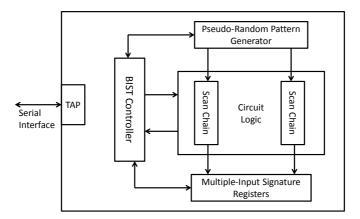

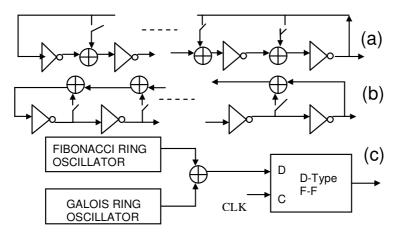

|    |        | 1.1.4   | Logic Built-In Self-Test (LBIST)                          | 5   |

|    |        | 1.1.5   | Time Compaction                                           | 6   |

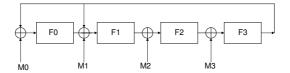

|    |        | 1.1.6   | Multiple Input Signature Register (MISR)                  | 7   |

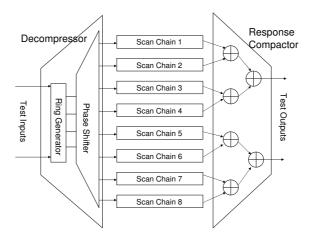

|    | 1.2    | Test (  | Compression                                               | 7   |

viii \_\_\_\_\_\_ CONTENTS

|   |     | 1.2.1   | Space C    | ompaction                                                              | 8  |

|---|-----|---------|------------|------------------------------------------------------------------------|----|

|   |     | 1.2.2   | X-State    | Handling                                                               | 8  |

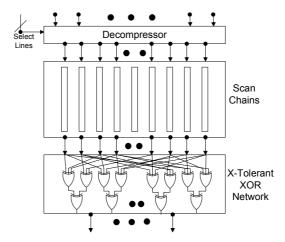

|   |     |         | 1.2.2.1    | X-Tolerant Schemes                                                     | 9  |

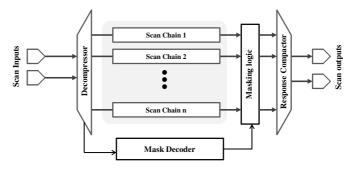

|   |     |         | 1.2.2.2    | X-masking Schemes                                                      | 10 |

|   | 1.3 | Introd  | luction to | Scan Attacks                                                           | 11 |

|   |     | 1.3.1   | Attack I   | Principle                                                              | 12 |

|   |     | 1.3.2   | Attack 7   | Target                                                                 | 12 |

|   |     | 1.3.3   | Attacker   | Scenario and Assumptions                                               | 12 |

|   |     | 1.3.4   | Classica   | l Differential Scan Attacks                                            | 13 |

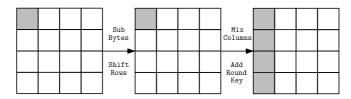

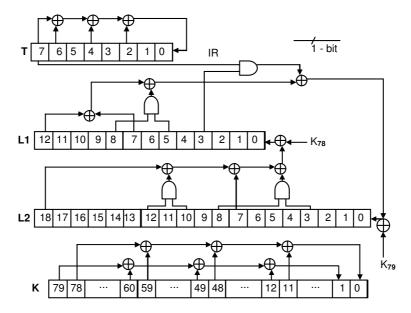

|   |     | 1.3.5   | Advance    | ed Encryption Standard (AES)                                           | 14 |

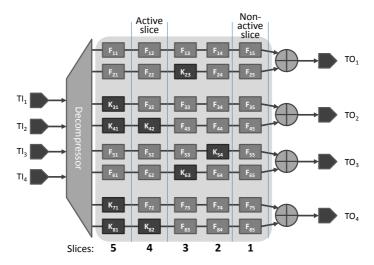

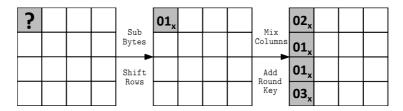

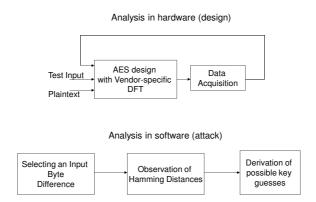

|   |     | 1.3.6   | Modified   | l Differential Scan Attacks                                            | 14 |

|   |     | 1.3.7   | Recent 1   | Differential Scan Attack                                               | 17 |

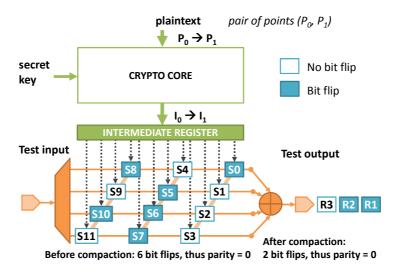

|   |     | 1.3.8   | Test Co    | mpression and security                                                 | 19 |

|   | 1.4 | Scan a  | attack cou | intermeasures                                                          | 19 |

|   | 1.5 | Summ    | ary of Co  | ontributions                                                           | 20 |

| _ | D:w |         | ı C A.     |                                                                        | 00 |

| 2 |     |         |            | tacks on Advanced DfT Schemes                                          | 23 |

|   | 2.1 |         |            |                                                                        | 24 |

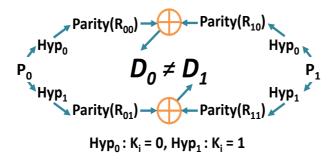

|   | 2.2 | Differe | ential Sca | n Attacks on Symmetric-Key Implementations                             | 24 |

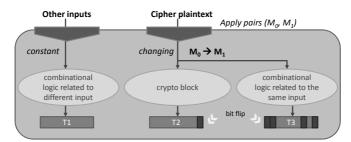

|   |     | 2.2.1   | Attack S   | Strategy                                                               | 24 |

|   |     | 2.2.2   | Distribu   | tions Considered                                                       | 26 |

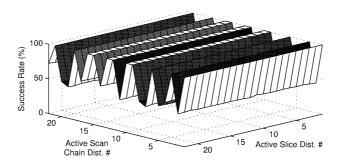

|   |     | 2.2.3   |            | tack on AES Hardware in the Presence of XOR ion with X-Tolerance       | 28 |

|   |     | 2.2.4   |            | tack on AES Hardware in the Presence of XOR tion with Static X-Masking | 31 |

|   |     |         | 2.2.4.1    | Description of the Attack                                              | 31 |

|   |     |         | 2.2.4.2    | DSA on XOR Compaction with Static X-Masking                            | 32 |

|   |     |         | 2.2.4.3    | DSA on XOR Compaction, Static X-Masking and OPMISR                     | 35 |

CONTENTS \_\_\_\_\_\_ix

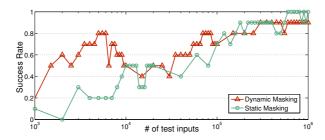

|     | 2.2.5   |             | tack on AES Hardware in the Presence of XOR tion with Dynamic X-Masking | 36  |

|-----|---------|-------------|-------------------------------------------------------------------------|-----|

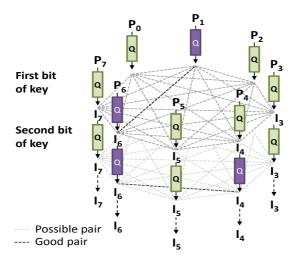

| 2.3 | Differe | ential Scar | n Attacks on Public Key Implementations                                 | 38  |

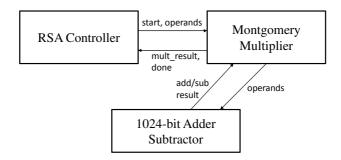

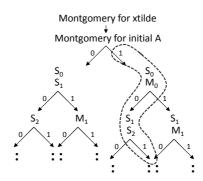

|     | 2.3.1   | Different   | sial Scan Attacks on RSA                                                | 39  |

|     |         | 2.3.1.1     | RSA                                                                     | 39  |

|     |         | 2.3.1.2     | Target RSA Hardware Implementation                                      | 41  |

|     |         | 2.3.1.3     | Differential scan Attack Mode                                           | 41  |

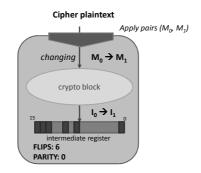

|     |         | 2.3.1.4     | Description of the Scan Attack on RSA $\ \ldots \ \ldots$               | 43  |

|     |         | 2.3.1.5     | Practical Aspects of the Attack                                         | 44  |

|     |         | 2.          | 3.1.5.1 Leakage Analysis                                                |     |

|     |         |             |                                                                         | 44  |

|     |         | 2.          | 3.1.5.2 Timing Aspects                                                  | 46  |

|     |         | 2.3.1.6     |                                                                         | 48  |

|     |         | 2.3.1.7     |                                                                         | 49  |

|     |         | 2.3.1.8     |                                                                         | 50  |

|     | 2.3.2   |             |                                                                         | 51  |

|     | 2.0.2   | 2.3.2.1     |                                                                         | 51  |

|     |         | 2.3.2.1     |                                                                         | 52  |

|     |         | 2.3.2.3     |                                                                         | 52  |

|     |         |             | •                                                                       |     |

|     |         | 2.3.2.4     |                                                                         | 53  |

|     |         | 2.3.2.5     |                                                                         | 53  |

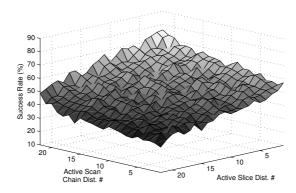

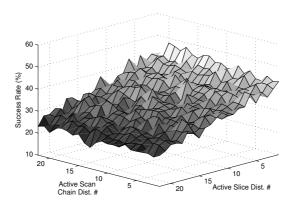

|     |         | 2.3.2.6     | v                                                                       | 56  |

|     |         | 2.3.2.7     | Inherent Countermeasure                                                 | 58  |

|     |         | 2.3.2.8     | Timing Estimate                                                         | 58  |

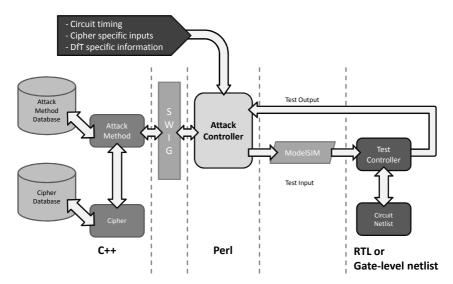

|     |         | 2.3.2.9     | Scan Attack Experimental Setup                                          | 59  |

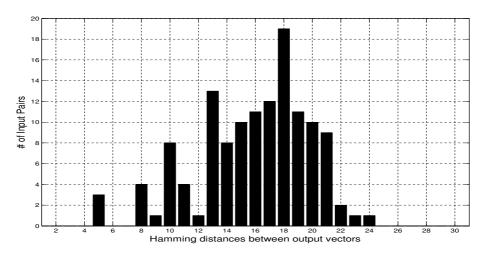

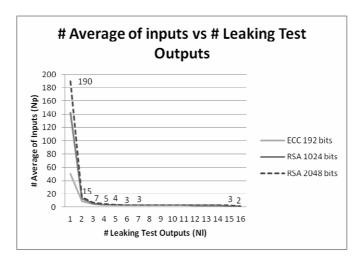

|     |         | 2.3.2.10    | Experimental Results and Discussion                                     | 59  |

|     |         | 2.          | 3.2.10.1 Scan attack timing and number of points                        | F 0 |

|     |         |             |                                                                         | 59  |

× \_\_\_\_\_ CONTENTS

|    |         |         | 2.3.2.10.2 Scan Attack on ECC in Presence of<br>Advanced DfT Methods |    |

|----|---------|---------|----------------------------------------------------------------------|----|

|    |         |         |                                                                      | 60 |

|    |         |         | 2.3.2.11 Previous Work                                               | 60 |

|    | 2.4     | Concl   | usion                                                                | 61 |

| 3  | Sca     | n Attac | ck Countermeasures                                                   | 63 |

| Pa | rt I: ( | Counter | measures from other side-channel attacks                             |    |

|    | 3.1     | Introd  | luction                                                              | 64 |

|    | 3.2     | Side (  | Channel Attacks and countermeasures                                  | 65 |

|    | 3.3     | Mathe   | ematical Modeling and Attack Scenarios                               | 66 |

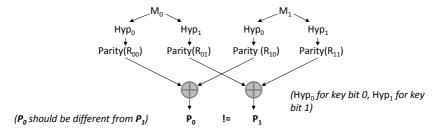

|    |         | 3.3.1   | Mathematical Analysis of DSA on PKC                                  | 66 |

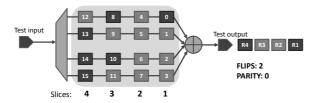

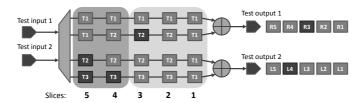

|    |         | 3.3.2   | DfT Configuration and Leaking Slices                                 | 66 |

|    |         | 3.3.3   | Handling the Mask Decoder                                            | 68 |

|    | 3.4     | Scan .  | Attacks with SPA Countermeasures in Place                            | 69 |

|    | 3.5     | Scan .  | Attacks with DPA Countermeasures in Place                            | 71 |

|    | 3.6     | Scan .  | Attacks with Fault Attack Countermeasures in Place                   | 72 |

|    |         | 3.6.1   | Safe-Error Analysis                                                  | 73 |

|    |         | 3.6.2   | Small Subgroup Attack and Curve Integrity Check                      | 74 |

|    | 3.7     | Summ    | nary of Vulnerabilities and Countermeasures                          | 74 |

| Pa | rt II:  | Counte  | ermeasures Specific for Scan Attacks                                 |    |

|    | 3.8     | Explic  | cit Scan Attack Countermeasures                                      | 75 |

|    |         | 3.8.1   | Insertion of inverters in the scan structure                         | 75 |

|    |         | 3.8.2   | State Dependent Scan Flip-Flops                                      | 76 |

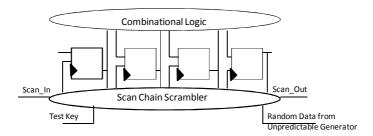

|    |         | 3.8.3   | Scan Chain Scrambling                                                | 76 |

|    |         | 3.8.4   | Removing All Traces of Secret Information in Test Mode $$ .          | 77 |

|    |         | 3.8.5   | Modified Partial Scan                                                | 77 |

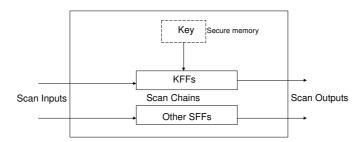

|    |         | 3.8.6   | Lock and Key Technique                                               | 78 |

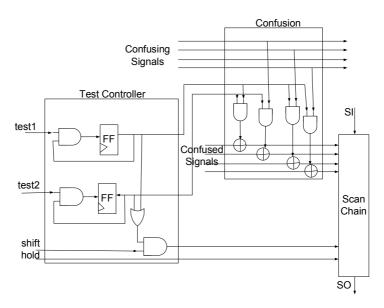

|    |         | 3.8.7   | Design for Secure Test                                               | 80 |

CONTENTS \_\_\_\_\_\_xi

|   |      | 3.8.8                                      | Masking Schemes                                                                            | 80                                     |

|---|------|--------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------|

|   |      | 3.8.9                                      | On-Chip Comparison                                                                         | 81                                     |

|   |      | 3.8.10                                     | Self-Test of Cryptographic Hardware                                                        | 81                                     |

|   | 3.9  | Differe                                    | ntial Scan Attack on Scan Attack Countermeasures                                           | 82                                     |

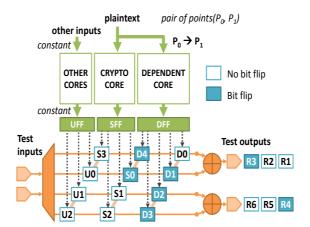

|   |      | 3.9.1                                      | Combined Scan attack on AES with Test Compression and Scan Attack Countermeasures in Place | 82                                     |

|   |      | 3.9.2                                      | Scan Attack on RSA in the Presence of Proposed Countermeasures                             | 84                                     |

|   |      | 3.9.3                                      | Scan Attack on ECC in the Presence of Proposed Countermeasures                             | 85                                     |

|   | 3.10 | Noise ?                                    | Injector Countermeasure                                                                    | 85                                     |

|   |      | 3.10.1                                     | Design of the Noise Injector                                                               | 86                                     |

|   |      | 3.10.2                                     | Security Analysis of the Noise Injector                                                    | 87                                     |

|   |      | 3.10.3                                     | Impact on Test Coverage and Overheads                                                      | 87                                     |

|   | 3.11 | Conclu                                     | sion                                                                                       | 89                                     |

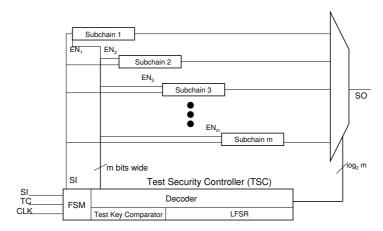

| 4 | Secu | ire Tes                                    | t Infrastructure                                                                           | 91                                     |

|   |      |                                            |                                                                                            | 91                                     |

|   | 4.1  | Introd                                     | uction                                                                                     | 92                                     |

|   | 4.1  |                                            |                                                                                            | _                                      |

|   |      |                                            | uction                                                                                     | 92                                     |

|   |      | Secure                                     | uction                                                                                     | 92<br>92                               |

|   |      | Secure 4.2.1                               | JTAG                                                                                       | 92<br>92<br>92                         |

|   |      | Secure 4.2.1 4.2.2                         | JTAG                                                                                       | 92<br>92<br>92<br>95                   |

|   |      | Secure<br>4.2.1<br>4.2.2<br>4.2.3          | JTAG                                                                                       | 92<br>92<br>92<br>95<br>97             |

|   |      | Secure<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4 | JTAG                                                                                       | 92<br>92<br>92<br>95<br>97             |

|   |      | Secure 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5       | JTAG                                                                                       | 92<br>92<br>92<br>95<br>97<br>99       |

|   |      | Secure 4.2.1 4.2.2 4.2.3 4.2.4 4.2.5 4.2.6 | JTAG                                                                                       | 92<br>92<br>92<br>95<br>97<br>99<br>99 |

xii \_\_\_\_\_\_CONTENTS

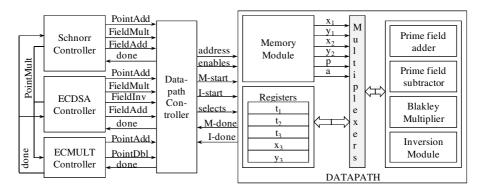

|     | 4.2.10 |                    | e used for ECC Point Addition and Doubling in ve Coordinates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 104 |

|-----|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

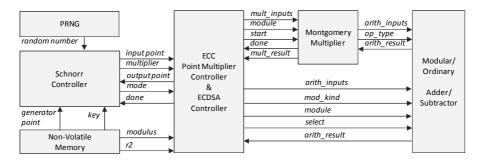

|     | 4.2.11 | Hardwar<br>modules | re Implementation of space-time optimized ECC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 104 |

|     |        | 4.2.11.1           | Design I: ECC over Projective Coordinates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 104 |

|     |        | 4.2.11.2           | Design II: ECC over Affine Coordinates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106 |

|     | 4.2.12 | Area and           | d Timing Costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 108 |

|     |        | 4.2.12.1           | Area Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 108 |

|     |        | 4.2.12.2           | Timing Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 109 |

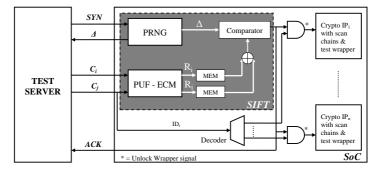

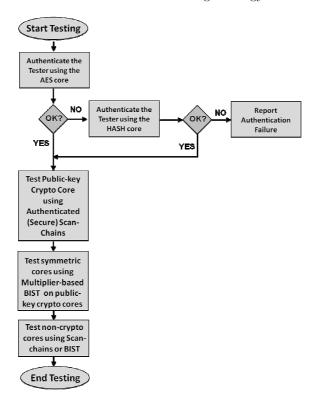

| 4.3 | Secure | Test Wra           | apper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 111 |

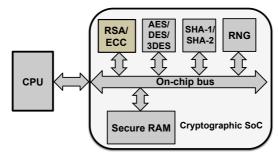

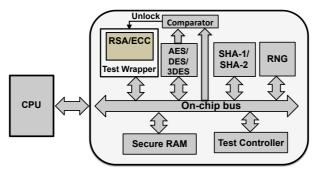

|     | 4.3.1  | Cryptog            | raphic SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111 |

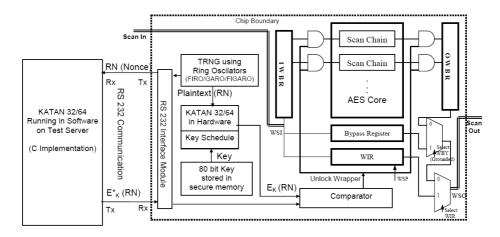

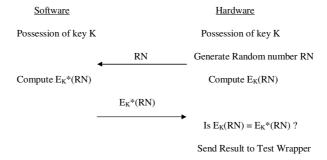

|     | 4.3.2  | Secure T           | Testing and SoC Integration Testing Environment $% \left( 1\right) =\left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left($ | 112 |

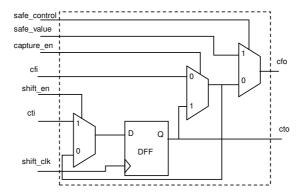

|     | 4.3.3  | Standard           | d IEEE 1500 Test Wrapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 113 |