ARENBERG DOCTORAL SCHOOL Faculty of Engineering Science

# Cross-Layer Optimization for Power-Efficient and Robust Digital Circuits and Systems

Yanxiang Huang

Supervisors: Prof. dr. ir. Wim Dehaene Prof. dr. ir. Liesbet Van der Perre Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Electrical Engineering

### Cross-Layer Optimization for Power-Efficient and Robust Digital Circuits and Systems

### Yanxiang HUANG

Examination committee: Prof. dr. ir.Yves Willems, chair Prof. dr. ir. Wim Dehaene, supervisor Prof. dr. ir. Liesbet Van der Perre, supervisor Prof. dr. ir. Francky Catthoor Prof. dr. ir. Sofie Pollin Prof. dr. ir. Rudy Lauwereins Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Electrical Engineering

Prof. dr. ir. Andreas P. Burg (École Polytechnique Fédérale de Lausanne) Prof. dr. ir. Liang Liu (Lund University)

In collaboration with **imec** vzw Kapeldreef 75 B-3001 Leuven (Belgium)

September 12, 2017

© 2017 KU Leuven – Faculty of Engineering Science Uitgegeven in eigen beheer, Yanxiang Huang, Kasteelpark Arenberg 10, B-3001 Leuven (Belgium)

Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt worden door middel van druk, fotokopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever.

All rights reserved. No part of the publication may be reproduced in any form by print, photoprint, microfilm, electronic or any other means without written permission from the publisher.

## Acknowledgements

Undertaking this Ph.D. has been a truly life-changing experience for me. It would not have been possible without the support and guidance that I received from many people. It is a pleasure for me to take this opportunity to express my gratitude.

First of all, I would like to express my deep and sincere appreciation to my supervisors, Prof. Wim Dehaene and Prof. Liesbet Van der Perre. I have been incredibly lucky to have both as my advisors. Prof. Liesbet Van der Perre offered me the opportunity, backed in 2013 autumn, to pursue this research subject that I passionate. She always keeps faith in my work and provides full support in every aspect of my research, spanning from the knowledge on wireless communication systems, to scientific writing and even career advice. Prof. Wim Dehaene joined as my promoter in 2014 winter. He brings not only world-class understanding of circuits and systems, inspiring consultations on professional and personal developments. Furthermore, I would like to thank my committee member Prof. Francky Catthoor, for providing critical comments on my work, and for teaching me the enthusiastic attitude towards research. My cordial gratefulness also goes to all the jury members: Prof. Sofie Pollin, Prof. Rudy Lauwereins, Prof. Andreas P. Burg, and Prof. Liang Liu. It is their feedback that significantly improves this work.

My sincere thank goes to Andre Bourdoux, for his scientific supervision from the imec perceptive. I would like to thank Chunshu Li, towards whom I can share all the ideas freely. His advice helps shape a lot of the flashing thoughts towards research ideas. I would also express my appreciation to Meng Li. She has always been very supportive since the first day I joined imec.

Besides, I would like to express my gratitude my superb colleagues from the perceptive system group in imec, Maxim Rykunov, Khaled Khalaf, Claude Desset, Veerle Derudder, Qixian Shi, Hans Cappelle, Hans Suys, Simone Corbetta, Eddy De Greef, Miguel Glassee, and Karthick Parashar. Thank you for your warm help when I came to you with mathematics formulation, Matlab code, system description, circuit simulation or even Latex code. Moreover, I would like to thank the group management and administration, Wim Van Thillo, Andy Dewilde, Charlotte Soens, Annemie Stas, and Bjorn Debaillie, for their supportive assistance with the practical issues during the past years, especially scheduling tape-outs, conferences attendance, and measurement equipment.

Furthermore, I would like to thank various colleagues from imec, Peter Debacker, Min Li, Julien Verschueren, Sebastien Morrison, Paul Zuber, Petr Dobrovolny, Phillip Christie, Steven Redant, for the enjoyable cross-discipline collaborations. I am also very grateful for the colleagues from the KU Leuven, Chunming Liu, and Andras Boho for the inspiring discussions.

I am deeply grateful to my Ph.D. friends, Halil Kukner, Matthias Hartmann, Prashant Agrawal, Ubaid Ahmad, Steve Blandino, Alessandro Chiumento, Raf Appeltans, Oscar Elisio Mattia, Johan Nguyen, for the special 'Ph.D.' moments. My warm gratitude also goes to Zhijie Xu, Habib Khalid, Yuzhu Gai, Antonio Callejon, Sara Gunnarsson, and Miceale Bortas, for the splendid cooperation during their master thesis.

Moreover, I would like to share my gratitude towards the friends from imec and KU Leuven, Michael Chen, Xiaoqiang Zhang, Zhiwei Zong, Yao Liu, Cheng-Hsueh Tsai, Leqi Zhang, Linkun Wu, Mingxu Liu, Weiming Qiu, Tiwei Wei, Menglei Xu, Chang Chen, Ziyang Liu, Dongjie Shao, Gaozhan Cai, Xin Lin, Jiachen Wang, Xueji Zhang, many others and their family members, for invaluable help and consultant in all aspects.

Finally, I especially owe my loving thanks to my family. The trust and encouragement from my parents helped me to overcome every difficulty and will motivate me achieving any other success in the future. I devote my deepest gratitude to my wife, Dan Ning. We met, got acquaintance, and finally got married during my Ph.D. study in Leuven. This thesis would not have been possible without her warming hug, understanding, encouragement, and most importantly, love.

> Yanxiang Huang September 2017 Leuven, Belgium

## Abstract

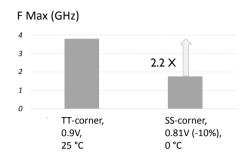

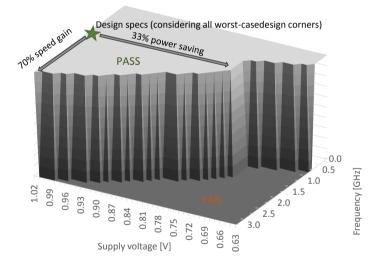

With the increasing digital services demand, performance and power-efficiency become vital requirements for digital circuits and systems. However, the enabling CMOS technology scaling has been facing significant challenges of device uncertainties, such as process, voltage, and temperature variations. To ensure system reliability, worst-case corner assumptions are usually made in each design level. However, the over-pessimistic worst-case margin leads to unnecessary power waste and performance loss as high as 2.2x. Since optimizations are traditionally confined to each specific level, those safe margins can hardly be properly exploited.

To tackle the challenge, it is therefore advised in this Ph.D. thesis to perform a cross-layer optimization for digital signal processing circuits and systems, to achieve a global balance of power consumption and output quality.

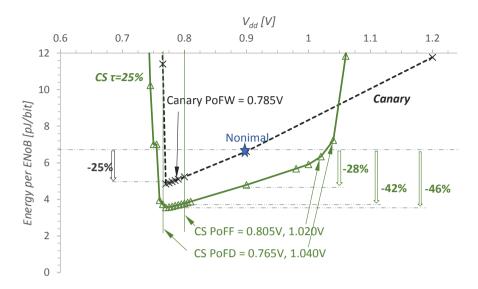

The first key contribution of this work is an algorithm to identify important flipflops that contribute significantly to circuit outputs, by analytically modeling reliability threats at logic gate-level. Consequently, circuit designers are guided on which flip-flop to harden against random errors (on ASIC, e.g. FFT, LDPC decoder). With this help, this thesis eliminated the unnecessary hardening overheads (achieving the same SNR with only half of hardening overheads) for a traditional FFT design. This work also contributes by optimizing the microarchitecture for the embedded OpenRISC processor, exploiting application-level word-length opportunities. It improved the power efficiency for universal signal processing applications. For instance, It saved power by 9.5% for the whole execution unit on the Coremark benchmark. Moreover, this work mitigated circuit-level errors in micro-architectural and algorithm levels for recursive applications. The techniques were applied on a CORDIC hardware accelerator in digital front-end, which saves power consumption by up to 46The last key contribution of this thesis is the algorithm and application-level optimization to mitigate lower-level errors on Massive MIMO wireless communication systems. It demonstrated that for typical Massive MIMO setup, a few (3%) antenna

outage will only degrade the target system SNR by 0.5dB. This promotes operating the circuit in a more aggressive region, which might lead to circuit errors, to improve power efficiency.

To conclude, the traditional over-pessimistic worst-case approach leads to huge power waste. In contrast, the adaptive voltage scaling approach saves power (25% for the CORDIC application) by providing a just-needed supply voltage. The power saving is maximized (46% for CORDIC) when a more aggressive voltage over-scaling scheme is applied. These sparsely occurred circuit errors produced by aggressive voltage over-scaling are mitigated by higher level error resilient designs. For functions like FFT and CORDIC, smart error mitigation schemes were proposed to enhance reliability (soft-errors and timing-errors, respectively). Applications like Massive MIMO systems are robust against lower level errors, thanks to the intrinsically redundant antennas. This property makes it applicable to embrace digital hardware that trades quality for power savings.

## Nederlandstalige Synopsis

Met de toenemende vraag naar digitale diensten worden prestaties en vermogenefficiëntie energie-efficiëntie essentiële vereisten voor digitale circuits en systemen. De schaling van CMOS technologie die dit mogelijk maakt, wordt echter geconfronteerd met belangrijke uitdagingen door onzekerheden in geminiaturiseerde componenten, zoals proces-, spanning- en temperatuurvariaties. Om de betrouwbaarheid van systemen te waarborgen, worden meestal in alle ontwerpniveaus conservatieve marges voorzien. Deze aannames zijn echter te pessimistisch, en de genomen marges zorgen voor energieverspilling en prestatieverlies dat kan oplopen tot een factor 2.2 van wat haalbaar is door de technologie. Aangezien de optimalisaties traditioneel beperkt zijn tot elk specifiek niveau, kunnen deze veilige marges niet goed worden benut.

Om deze uitdaging aan te pakken, wordt het daarom geadviseerd in dit Ph.D. proefschrift om een cross-layer optimalisatie uit te voeren voor digitale signaalverwerkingscircuits en systemen, om een globaal evenwicht te bereiken tussen stroomverbruik en kwaliteit aan de uitgangen van de schakelingen.

De eerste sleutelbijdrage van dit werk is een algoritme om belangrijke flip-flops te identificeren die aanzienlijk bijdragen aan de uitgangen van het circuit, door analytische modellering vanbetrouwbaarheidsdrempels op logisch poortniveau. Bijgevolg worden circuitontwerpers begeleid om enkel een hogere marge te nemen op flip-flops die gevoeliger zijn voor willekeurige fouten (bijvoorbeeld FFT, LDPC decoder circuits in een applicatie specifieke schakeling). Met deze hulp elimineerde dit proefschrift de onnodige marges op de helft van de flipflopseen traditioneel FFT-ontwerp, en kon een identieke kwaliteit bekomen worden als het conservatief ontwerp. Dit werk draagt ook bij aan het optimaliseren van de microarchitectuur van een microprocessor voor het verbeteren van de energie-efficiëntie voor universele signaalverwerking toepassingen . Dit verbeterde de energieefficiëntie van de verwerkingseenheid van een OpenRisc processor met 9.5% voor de volledige Coremark benchmark . Bovendien verminderde dit werk fouten op circuitniveau in micro-architecturale en algoritme-niveaus voor recursieve

toepassingen. De technieken werden toegepast op een CORDIC hardware accelerator in digitale front-end, waardoor een besparing van energieverbruik met 46% wordt bekomen. De laatste belangrijke bijdrage van dit proefschrift is het optimaliseren van de algoritme en applicatie om de fouten van de Massive MIMO draadloze communicatiesystemen te beperken. Het blijkt dat voor een typische Massieve MIMO-installatie antenne-uitval van 3% de signaal ruis verhoudingslechts met 0.5 dB zal degraderen. Dit laat toe de electronische circuits te laten werken in een foutgevoeliger gebied, om de energie-efficiëntie van het totaal systeem gevoelig te verbeteren.

Tenslotte stelden we vast dat de traditionele keuze voor pessimistische marges inderdaad tot gevoelige vermogentoename leiden. In tegenstelling hiermee bespaart de adaptieve spanningsschaalbenadering energie (25% voor de CORDIC-toepassing) door de benodigde voedingsspanning te beperken. De energiebesparing wordt gemaximaliseerd (46% voor CORDIC) wanneer een meer agressieve spanningsoverschaling wordt toegepast. Deze zelden voorkomende schakelfouten, die worden veroorzaakt door agressieve verlagen van de spanning, worden vermeden door een robuuster ontwerp op hogere niveaus van de meest gevoelige schakelingen. Voor functies zoals FFT en CORDIC werden slimme foutverminderingsschema's voorgesteld om de betrouwbaarheid te verbeteren (respectievelijk softfouten en timingfouten). Toepassingen zoals Massive MIMO-systemen zijn robuust tegen hoger fouten, dankzij de intrinsieke redundante antennes. Deze eigenschap laat to om kwaliteit af te wegen ten opzichte van energiebesparing voor digitale hardware.

## Abbreviations

This list of acronyms only specifies the most important ones. The abbreviations lists below represent both the singular and the plural forms.

**ANT** Algorithmic Noise Tolerance.

ASIC Application Specific Integrated Circuit.

**ASIP** Application-Specific Instruction set Processor.

AVFS Adaptive Voltage Frequency Scaling.

**AWGN** Additive White Gaussian Noise.

**BER** Bit Error Rate.

**BS** Base Station.

CMOS Complementary Metal Oxide Semiconductor.

CORDIC COordinate Rotation DIgital Computer.

**CPI** Cycles Per Instruction.

${\bf CPU}\,$  Central Processing Unit.

**CS** Computation-Skip.

DAC Digital-to-Analog Converter.

**DFE** Digital Front-End.

DL Down Link.

**DSP** Digital Signal Processing/Processor.

ECC Error Correction Code.

EDA Electronic Design Automation.

**ENoB** Effective Number of Bits.

${\bf EVM}\,$  Error Vector Magnitude.

**FF** Flip-Flop.

**FFT** Fast Fourier Transform.

**FIR** Finite Impulse Response.

FPGA Field-Programmable Gate Array.

IC Integrated Circuit/Chip.

**IoT** Internet of Things.

**IR-drop** dynamic voltage drop.

LDPC Low-Density Parity-Check code.

LSB Least Significant Bit.

LTE Long Term Evolution.

**LUT** Look-Up Table.

MAC Multiply Accumulate.

MCU Micro-Controller Unit.

MIMO Multiple Input Multiple Output.

**MMSE** Minimum Mean Square Error.

**MSB** Most Significant Bit.

**MSFF** Master-Salve Flip-Flop.

**OCV** On-Chip Variation.

#### **OFDM** Orthogonal Frequency Division Multiplexing.

**PA** Power Amplifier.

**PoFD** Point of First noticeable Degradation.

**PoFF** Point of First Failure.

**PoFW** Point of First Warning.

**PVT** Process Voltage Temperature.

**QAM** Quadrature Amplitude Modulation.

${\bf QPSK}\,$  Quadrature Phase Shift Keying.

**RAM** Random Access Memory.

**RISC** Reduced Instruction Set Computer.

**RTL** Register Transfer Level.

**SDDR** Signal to Digital Distortion Ratio.

${\bf SDR}\,$  Software Defined Radio.

SEU Single Event Upset.

**SIMD** Single Instruction, Multiple Data.

**SNR** Signal to Noise Ratio.

**SRAM** Static Random-Access Memory.

**STA** Static Timing Analysis.

**TDD** Time division duplex.

UL Up Link.

**VLSI** Very Large Scale Integration.

**VOS** Voltage-OverScaling.

**ZF** Zero-Forcing.

## Contents

| Acl                       | know                | wledgements                                                                                                          | i  |  |  |

|---------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------|----|--|--|

| Ab                        | stra                | ct ii                                                                                                                | ii |  |  |

| Nederlandstalige Synopsis |                     |                                                                                                                      |    |  |  |

| Contents xi               |                     |                                                                                                                      |    |  |  |

| List                      | List of Figures xix |                                                                                                                      |    |  |  |

| List of Tables xxii       |                     |                                                                                                                      |    |  |  |

| 1                         | Intr                | roduction                                                                                                            | 1  |  |  |

|                           | 1.1                 | Context: motivation for power consumption and reliability trade-<br>offs                                             | 1  |  |  |

|                           |                     | 1.1.1 Demand: performance and power efficiency improvements                                                          | 2  |  |  |

|                           |                     | 1.1.2 Reality: device and application uncertainties endanger successful designs                                      | 4  |  |  |

|                           | 1.2                 | Calling for cross-layer optimizations                                                                                | 6  |  |  |

|                           |                     | 1.2.1 Traditional pyramid-shaped design                                                                              | 6  |  |  |

|                           |                     | 1.2.2 Cross-layer optimization $\ldots \ldots \ldots$ | 8  |  |  |

|                           | 1.3                 | Thesis scope                                                                                                         | 0  |  |  |

|                                                                          | 1.4        | Main                                                       | contributions                                                                                                                                                                                                                                                               | 11                         |

|--------------------------------------------------------------------------|------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                                                                          | 1.5        | Thesis                                                     | s structure                                                                                                                                                                                                                                                                 | 12                         |

| •                                                                        | _          |                                                            |                                                                                                                                                                                                                                                                             |                            |

| 2                                                                        | Вас        | -                                                          | d: pessimistic safety margins should be exploited                                                                                                                                                                                                                           | 15                         |

|                                                                          | 2.1        | Uncer                                                      | tainties in circuit paramaters                                                                                                                                                                                                                                              | 15                         |

|                                                                          |            | 2.1.1                                                      | Process variations and aging effects                                                                                                                                                                                                                                        | 16                         |

|                                                                          |            | 2.1.2                                                      | Environmental and runtime uncertainties                                                                                                                                                                                                                                     | 19                         |

|                                                                          | 2.2        | Adjus                                                      | t supply voltage to trade quality for power savings $\ldots$ .                                                                                                                                                                                                              | 22                         |

|                                                                          |            | 2.2.1                                                      | Limitations to the worst-case corner approach                                                                                                                                                                                                                               | 23                         |

|                                                                          |            | 2.2.2                                                      | Adaptive supply voltage schemes                                                                                                                                                                                                                                             | 24                         |

|                                                                          | 2.3        | Cross-                                                     | layer error-resilient voltage over-scaling schemes                                                                                                                                                                                                                          | 27                         |

|                                                                          |            | 2.3.1                                                      | In-situ error detection and corrections                                                                                                                                                                                                                                     | 28                         |

|                                                                          |            | 2.3.2                                                      | Arithmetic noise tolerance                                                                                                                                                                                                                                                  | 29                         |

|                                                                          | 2.4        | Concl                                                      | usion                                                                                                                                                                                                                                                                       | 30                         |

| 3 Gate-level error impacts modeling analysis for random er<br>mitigation |            |                                                            | error impacts modeling analysis for random error                                                                                                                                                                                                                            | 31                         |

| 3.1 Demands for a reliability model                                      |            |                                                            |                                                                                                                                                                                                                                                                             | 32                         |

|                                                                          | 3.2        |                                                            |                                                                                                                                                                                                                                                                             |                            |

|                                                                          |            | Model                                                      | ling and enhancement techniques for reliability                                                                                                                                                                                                                             | 33                         |

|                                                                          |            | Model<br>3.2.1                                             | v                                                                                                                                                                                                                                                                           | 33<br>33                   |

|                                                                          |            |                                                            | ling and enhancement techniques for reliability                                                                                                                                                                                                                             |                            |

|                                                                          | 3.3        | 3.2.1<br>3.2.2                                             | ling and enhancement techniques for reliability Error modeling                                                                                                                                                                                                              | 33                         |

|                                                                          | 3.3<br>3.4 | 3.2.1<br>3.2.2<br>Contra<br>SERL                           | ling and enhancement techniques for reliability                                                                                                                                                                                                                             | 33<br>34                   |

|                                                                          |            | 3.2.1<br>3.2.2<br>Contra<br>SERL                           | ling and enhancement techniques for reliability          Error modeling          Reliability enhancement techniques          ibutions of this chapter          AL – a SignificancE RankIng ALgorithm for error effects                                                      | 33<br>34<br>35             |

|                                                                          |            | 3.2.1<br>3.2.2<br>Contr<br>SERL<br>model                   | ling and enhancement techniques for reliability          Error modeling          Reliability enhancement techniques          ibutions of this chapter          AL – a SignificancE RankIng ALgorithm for error effects         ing                                          | 33<br>34<br>35<br>36       |

|                                                                          |            | 3.2.1<br>3.2.2<br>Contr<br>SERL<br>model<br>3.4.1<br>3.4.2 | ling and enhancement techniques for reliability         Error modeling         Reliability enhancement techniques         ibutions of this chapter         AL – a SignificancE RankIng ALgorithm for error effects         ing         Determine the distribution factor DF | 33<br>34<br>35<br>36<br>39 |

CONTENTS \_\_\_\_\_\_ xv

|   |      | 3.5.2               | Validation on an LDPC decoder                                  | 51 |

|---|------|---------------------|----------------------------------------------------------------|----|

|   | 3.6  | Applie              | cation to harden an FFT design                                 | 52 |

|   | 3.7  | Conclu              | usion                                                          | 53 |

| 4 |      | roarchi<br>ortuniti | tecture-level power optimization exploiting application ies    | 55 |

|   | 4.1  | Proces              | ssor power waste in using unsuitable execution units $\ldots$  | 56 |

|   | 4.2  | Contri              | ibution of this chapter                                        | 56 |

|   | 4.3  | Target              | ted embedded processing platform                               | 57 |

|   |      | 4.3.1               | OpenRISC microarchitecture                                     | 57 |

|   |      | 4.3.2               | Power of the multiplication unit                               | 58 |

|   | 4.4  | Fine-g              | grained hardware-switch scheme for multiplier $(MUL)$          | 59 |

|   | 4.5  | Algori              | thm profile                                                    | 61 |

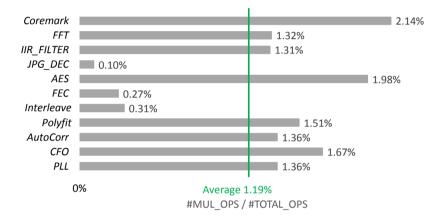

|   |      | 4.5.1               | Utilization frequency of MUL                                   | 62 |

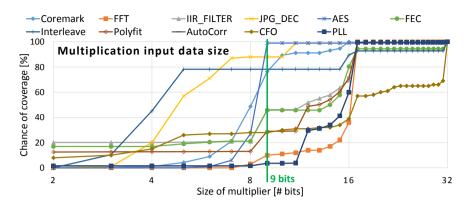

|   |      | 4.5.2               | Word-length distribution for $MUL$                             | 62 |

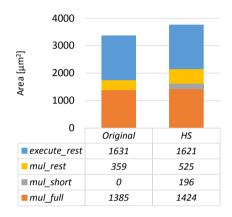

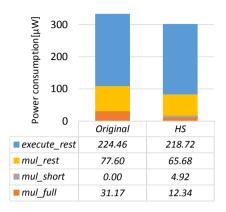

|   | 4.6  |                     | saving validation of the proposed fine-grained hardware scheme | 63 |

|   |      | 4.6.1               | Area comparison                                                | 64 |

|   |      | 4.6.2               | Power savings                                                  | 64 |

|   | 4.7  | Conclu              | usion                                                          | 65 |

| 5 | Algo | orithm-             | level error-resilient design mitigating circuit-level errors   | 67 |

|   | 5.1  | Motiv               | atuion to algorithm-level error resilience                     | 68 |

|   |      | 5.1.1               | Review of error-resilient techniques                           | 68 |

|   | 5.2  | Contra              | ibutions of this chapter                                       | 69 |

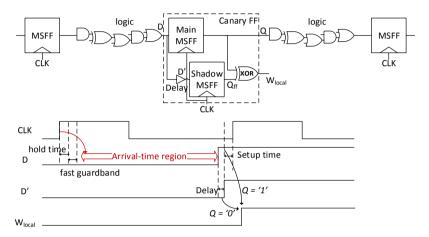

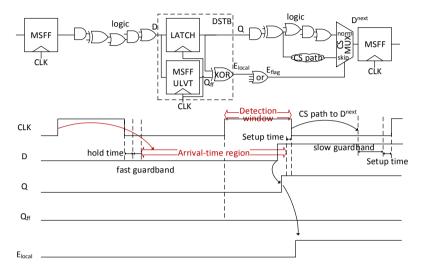

|   | 5.3  | Error               | resilient circuits implementations                             | 71 |

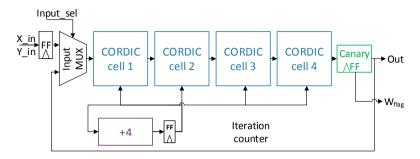

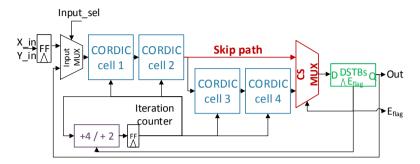

|   |      | 5.3.1               | Circuits with Canary FF                                        | 71 |

|   |      | 5.3.2               | Circuits with <i>computation-skip</i> scheme                   | 72 |

|   |     | 5.3.3    | Computation-skip scheme settings                                         | 74  |

|---|-----|----------|--------------------------------------------------------------------------|-----|

|   | 5.4 | Case s   | study on a CORDIC hardware accelerator                                   | 77  |

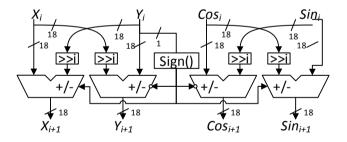

|   |     | 5.4.1    | CORDIC algorithm                                                         | 77  |

|   |     | 5.4.2    | State-of-the-art Core1 with Canary FF $\ldots$                           | 79  |

|   |     | 5.4.3    | Proposed Core2 with computation-skip scheme $\ldots$ .                   | 80  |

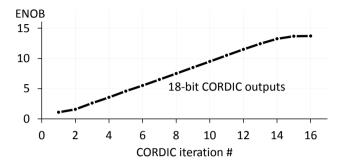

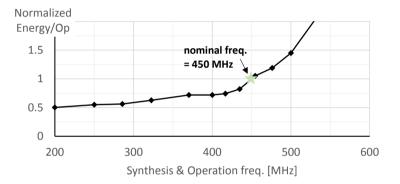

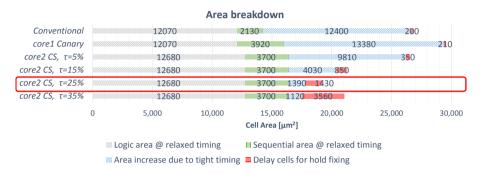

|   |     | 5.4.4    | Pre-silicon analysis                                                     | 83  |

|   |     | 5.4.5    | Post-silicon Measurement                                                 | 84  |

|   | 5.5 | Concl    | usion                                                                    | 88  |

| 6 | Арр | licatior | n-level error-resilience on massive MIMO base stations                   | 91  |

|   | 6.1 | Oppor    | rtunities and challenges of massive MIMO                                 | 92  |

|   |     | 6.1.1    | Massive MIMO, the highly-demanded future technology                      | 92  |

|   |     | 6.1.2    | Power consumption, a design challenge in massive MIMO digital processing | 93  |

|   | 6.2 | Contr    | ibution of this chapter                                                  | 94  |

|   | 6.3 | Masiv    | e MIMO system introduction                                               | 94  |

|   | 6.4 | Digita   | l hardware error impacts on signal quality $\ldots \ldots \ldots$        | 97  |

|   |     | 6.4.1    | VOS (Voltage-OverScaling) impacts                                        | 98  |

|   |     | 6.4.2    | Antenna outage impacts                                                   | 99  |

|   | 6.5 | Rando    | om antenna error impacts assessment                                      | 99  |

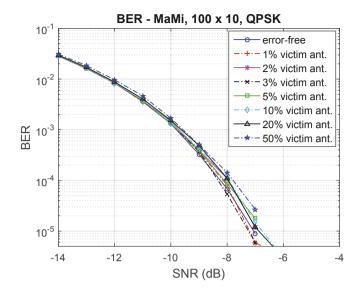

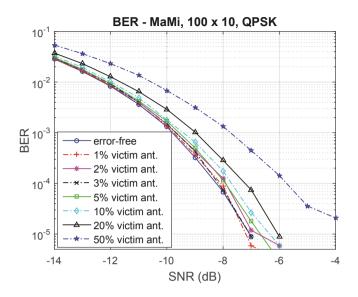

|   |     | 6.5.1    | Error effects on uncoded QPSK 100x10 massive MIMO $$                     | 100 |

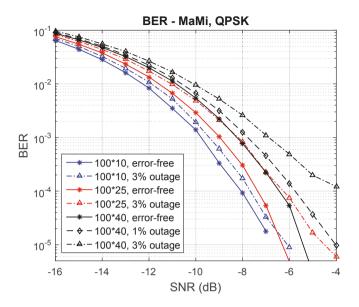

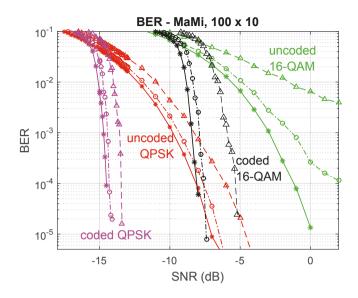

|   |     | 6.5.2    | Antenna outage effects for other massive MIMO setups                     | 103 |

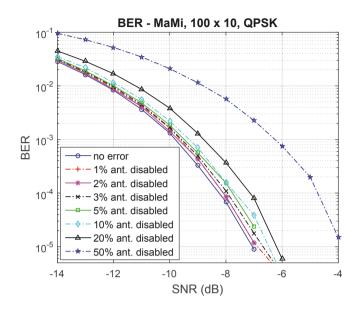

|   | 6.6 | Contr    | olled antenna outage                                                     | 106 |

|   | 6.7 | Concl    | usion                                                                    | 110 |

| 7 | Con | clusion  | s and future work                                                        | 111 |

|   | 7.1 | Concl    | usions                                                                   | 111 |

|   | 7.2 | Key n    | nessages                                                                 | 114 |

|                      | 7.3  | Future work                                            | 116 |  |

|----------------------|------|--------------------------------------------------------|-----|--|

| A                    | A di | gital front-end processor for 60 GHz polar transmitter | 119 |  |

|                      | A.1  | Introduction                                           | 119 |  |

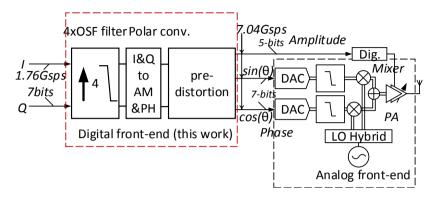

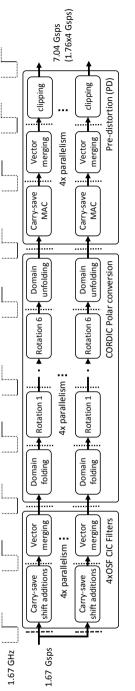

|                      | A.2  | System architecture                                    | 120 |  |

|                      |      | A.2.1 Polar conversion                                 | 121 |  |

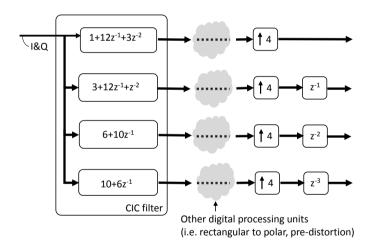

|                      |      | A.2.2 Phase shaping filter                             | 122 |  |

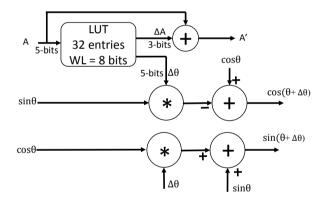

|                      |      | A.2.3 Pre-distortion                                   | 123 |  |

|                      | A.3  | Implementation details                                 | 124 |  |

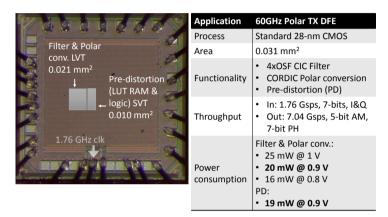

|                      | A.4  | Measurement results                                    | 127 |  |

|                      | A.5  | Conclusions                                            | 130 |  |

| Curriculum Vitea     |      |                                                        |     |  |

| List of publications |      |                                                        |     |  |

## **List of Figures**

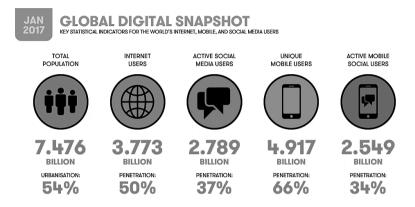

| 1.1 | The world is immersed in digital services.                                                                                                                                                                     | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

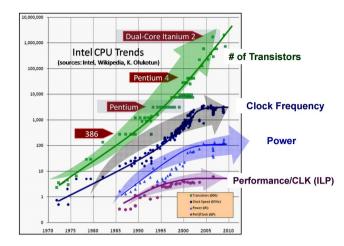

| 1.2 | The free lunch of CMOS scaling is over.                                                                                                                                                                        | 4  |

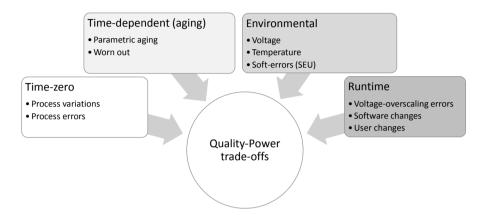

| 1.3 | Digital designs must cope with permanent (time-zero and time-dependent) and temporary (environmental and runtime) uncertainties (variations), to reach a balance between power consumption and output quality. | 5  |

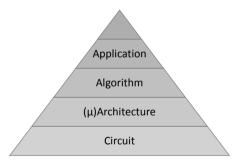

| 1.4 | The traditional pyramid-shaped design flow leads to over-designs at all levels.                                                                                                                                | 6  |

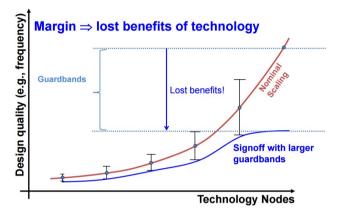

| 1.5 | Over-designed guardbands diminish the benefits of CMOS scaling.                                                                                                                                                | 7  |

| 1.6 | Promoted tower-shaped cross-layer design approach reduces<br>unnecessary power and area waste                                                                                                                  | 9  |

| 1.7 | Structure of the thesis and overview of the chapters. $\ldots$ .                                                                                                                                               | 13 |

| 2.1 | Spatial process variations consist of global and local components.                                                                                                                                             | 17 |

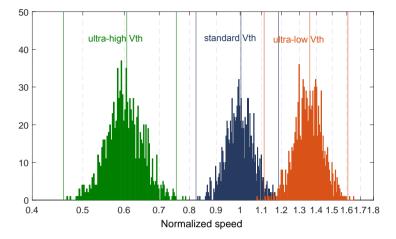

| 2.2 | The speed (inverse delay) of 28nm fan-out of 4 (FO4) ring oscillators (RO) follows a Gaussian distribution because of process variability.                                                                     | 18 |

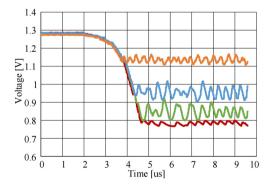

| 2.3 | The supply voltage of an IC is fluctuating                                                                                                                                                                     | 19 |

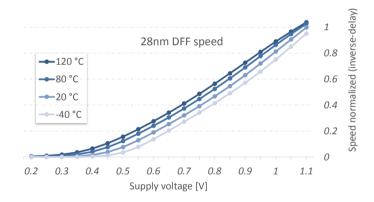

| 2.4 | The speed of a 28nm circuit changes along with temperature and supply voltage.                                                                                                                                 | 20 |

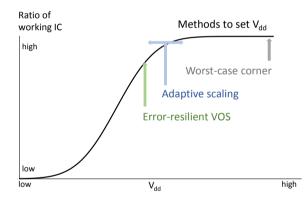

| 2.5 | Worst-case corner, adaptive scaling, and error resilient voltage over-scaling approaches all cope with speed variability.                                                                                      | 22 |

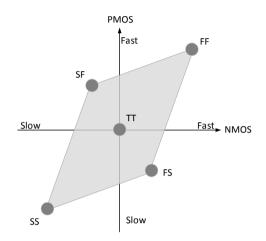

| 2.6  | Spatial process variability are described by slow and fast corner-<br>case files.                                                                  | 23 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.7  | The speed of a 28nm circuit exhibits a 2.2x difference between the typical-case and worst-case corners.                                            | 24 |

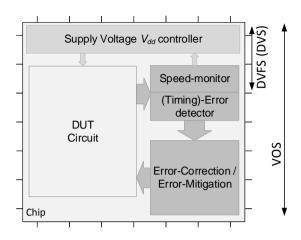

| 2.8  | The dynamical scaling method handles speed variability. More-<br>over, the error-resilient $V_{dd}$ scheme also handles circuit timing-<br>errors. | 25 |

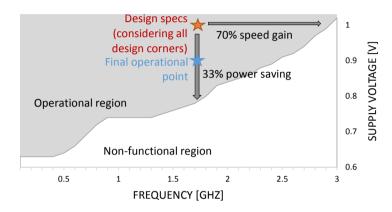

| 2.9  | The operation region of a digital front-end IC can be much wider<br>than conservatively assumed.                                                   | 26 |

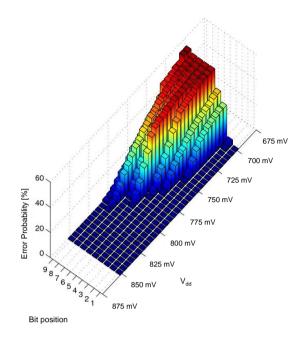

| 2.10 | With VOS, errors firstly occur at MSB for carry-ripple adders.                                                                                     | 28 |

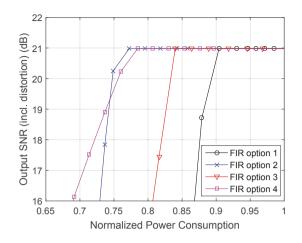

| 2.11 | VOS with error resilient techniques save power on FIR filter, at the cost of signal quality degradations [Liu, 2010].                              | 30 |

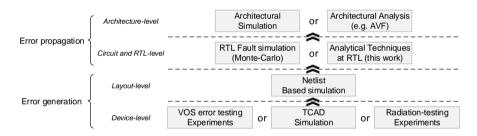

| 3.1  | Modeling process and structure for error impacts                                                                                                   | 33 |

| 3.2  | A significance graph inverses the signal direction of the corresponding netlist.                                                                   | 37 |

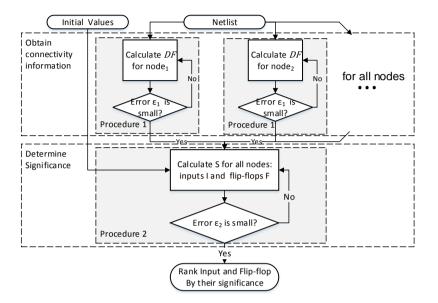

| 3.3  | The SERIAL model consist of two procedures.                                                                                                        | 39 |

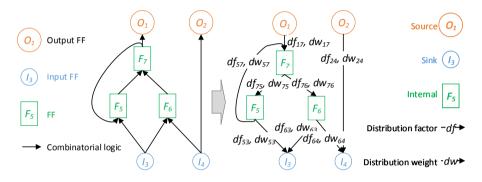

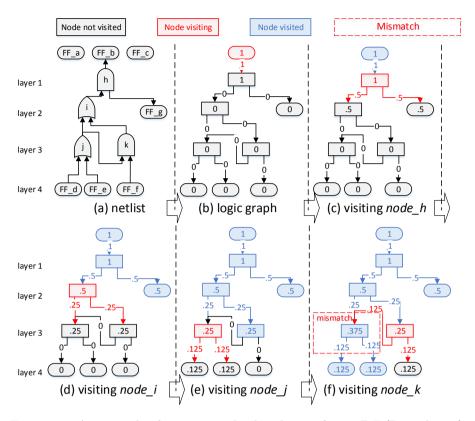

| 3.4  | An example of computing the distribution factor $DF$<br>(Procedure 1).                                                                             | 43 |

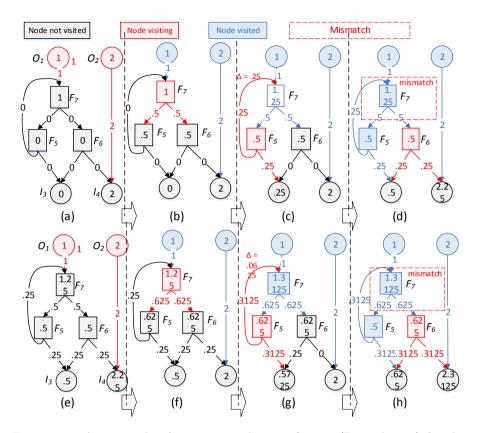

| 3.5  | An example of computing the significance (Procedure 2)                                                                                             | 47 |

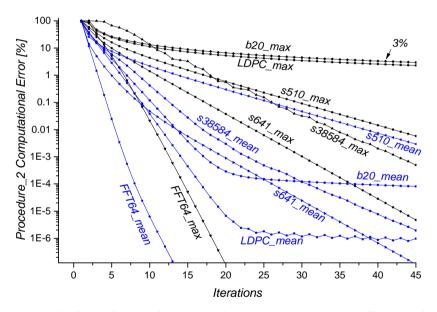

| 3.6  | In Procedure 2, the mismatch error $\epsilon_2$ converges rapidly towards 0.                                                                       | 50 |

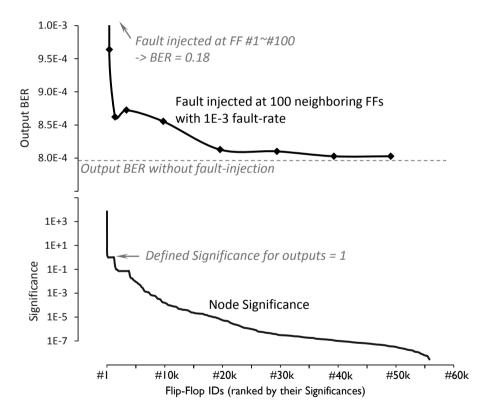

| 3.7  | In an LDPC decoder circuit, errors on FF with high significance values leads to worse BER.                                                         | 51 |

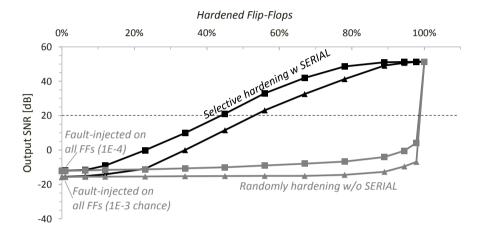

| 3.8  | Compared with hardening randomly, selective hardening with SERIAL increases the SNR, at the same hardening ratio                                   | 53 |

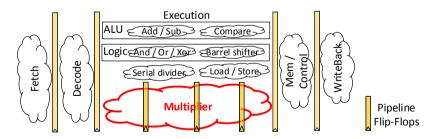

| 4.1  | A customized OpenRISC microarchitecture: the mor1kx Cap-<br>puccino flavor.                                                                        | 57 |

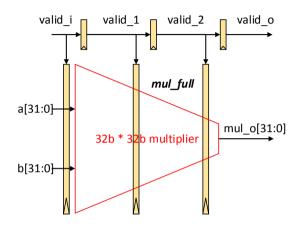

| 4.2  | The original multiplier in the Cappuccino implementation is 32 bits wide.                                                                          | 58 |

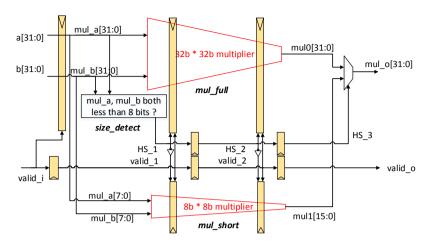

| 4.3  | MUL with the proposed hardware-switching (HS) scheme selects between a 32-bit and an 8-bit multiplier, based on the data range.                    | 60 |

| 4.4  | $H\!S$ saves power when the multiplication inputs are small                                                                                        | 61 |

LIST OF FIGURES \_\_\_\_\_\_ xxi

| 4.5  | Utilization frequency of the multiplier unit.                                                                                                                                                                   | 62  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.6  | The chance that both multiplicands are short increases when the criteria for 'short' gets loose.                                                                                                                | 63  |

| 4.7  | The proposed $HS$ scheme results to more area                                                                                                                                                                   | 64  |

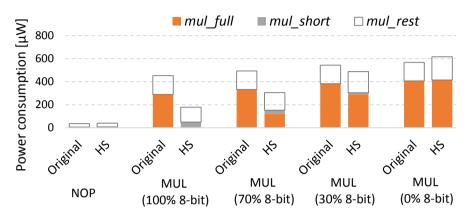

| 4.8  | The power consumption of the $HS$ reduces substantially                                                                                                                                                         | 65  |

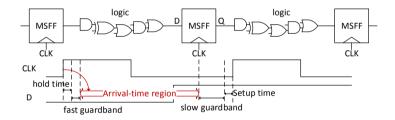

| 5.1  | The conventional pipeline scheme requires worst-case design margins.                                                                                                                                            | 71  |

| 5.2  | Circuits with in-situ <i>canary</i> FF that shave worst-case design margins                                                                                                                                     | 72  |

| 5.3  | Circuits with <i>computation-skip</i> scheme, which utilizes <i>DTSBs</i> for error-detection, eliminate worst-case design margins                                                                              | 73  |

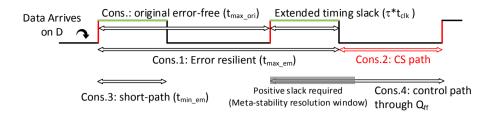

| 5.4  | Timing constraints for circuits with the ${\it computation-skip}$ scheme.                                                                                                                                       | 75  |

| 5.6  | The CORDIC output ENOB evolves with numbers of iterations $\boldsymbol{n}.$                                                                                                                                     | 79  |

| 5.9  | Example timing diagrams of the proposed <i>computation-skip</i> CORDIC                                                                                                                                          | 82  |

| 5.10 | 450 MHz is selected for the operating condition                                                                                                                                                                 | 83  |

| 5.11 | Cell area breakdown of the conventional and the proposed hardware CORDIC accelerators designed at 450 MHz                                                                                                       | 84  |

| 5.12 | Die photo and chip information.                                                                                                                                                                                 | 85  |

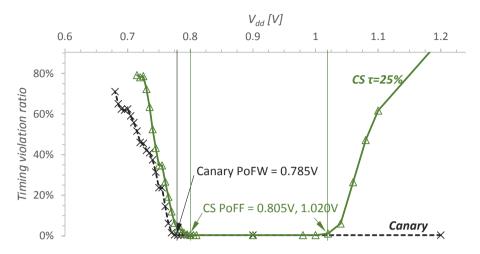

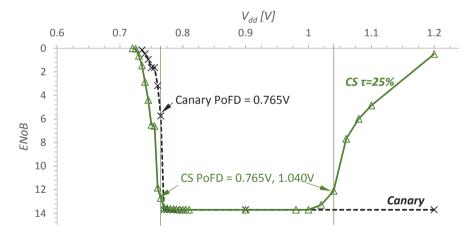

| 5.13 | Measured timing violation ratio.                                                                                                                                                                                | 86  |

| 5.14 | Measured CORDIC ENOB                                                                                                                                                                                            | 86  |

| 5.15 | Comparison of the <i>core1 canary</i> (implementing the baseline state-<br>of-the-art technique) and <i>core2</i> CS (implementing the proposed<br>scheme) CORDIC accelerators during voltage scaling. $\ldots$ | 88  |

| 6.1  | Massive MIMO exploits large antenna arrays to spatially multiplex many terminals.                                                                                                                               | 92  |

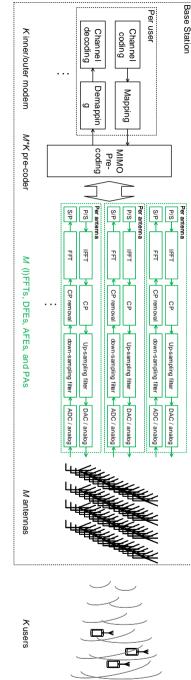

| 6.2  | A massive MIMO base station (BS) equips with $M$ antennas and serves $K$ users                                                                                                                                  | 96  |

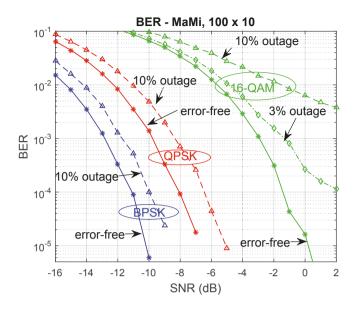

| 6.3  | Slight VOS digital distortion errors, i.e. SDDR = 10 dB, only degrades the system BER marginally.                                                                                                               | 101 |

| 6.4  | If the massive MIMO system is suffering from extensive VOS digital errors on some antennas, i.e. $SDDR = 0 dB$ , the output is still manageable.          | 102 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.5  | The system can tolerates some antenna outage (DFE output stuck at a fixed value), i.e. $SDDR = -\infty. \ldots \ldots$                                    | 103 |

| 6.6  | Simple modulation schemes are more resilient to antenna outage.                                                                                           | 104 |

| 6.7  | Lower loads leave more spaces for error absorption                                                                                                        | 105 |

| 6.8  | Coding and uncoded degradations are similar                                                                                                               | 106 |

| 6.9  | Massive MIMO system performance when victim antennas are discarded and the channel estimation and DL is carried out by the remaining error-free antennas. | 108 |

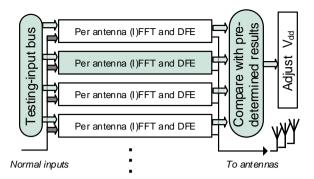

| 6.10 | An error resilient adaptive scaling technique to manage hardware errors.                                                                                  | 109 |

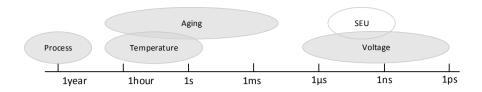

| 6.11 | The frequency of changing of the process, aging, temperature, and voltage noise that affect the timing errors of circuits                                 | 110 |

| A.1  | Block diagram of the digital intensive 60 GHz polar transmitter.                                                                                          | 121 |

| A.2  | Poly-phase implementation of the phase shaping filter                                                                                                     | 122 |

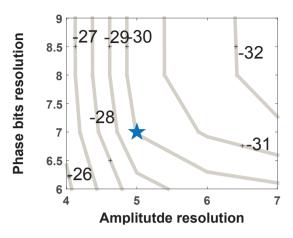

| A.3  | EVM vs. PH/AM resolution.                                                                                                                                 | 123 |

| A.4  | Pre-distortion circuits for PA non-linearities.                                                                                                           | 123 |

| A.5  | Pipeline scheme of the proposed DFE processor                                                                                                             | 125 |

| A.6  | Die photo and chip information of the proposed digital polar<br>DFE processor                                                                             | 127 |

| A.7  | Cell area breakdown of the proposed DFE processor                                                                                                         | 127 |

| A.8  | Typical chip speed vs. $V_{dd}$ @25°C                                                                                                                     | 128 |

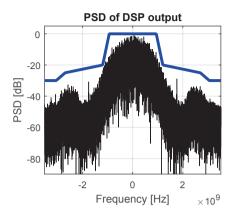

| A.9  | Measurement DFE outputs PSD                                                                                                                               | 129 |

| A.10 | Measurement DFE output 16-QAM constellation, with a corresponding EVM of -30.5 dB.                                                                        | 129 |

## List of Tables

| 3.1 | Truth table of a 3-input AND gate                                           | 41  |

|-----|-----------------------------------------------------------------------------|-----|

| 3.2 | SERIAL model solver runtime analysis for benchmark circuits.                | 49  |

| 4.1 | Multiplier area and power consumption during each instruction.              | 59  |

| 5.1 | In-situ timing-error detection and correction/mitigation schemes.           | 70  |

| 5.2 | Timing constraints for the <i>computation-skip</i> error mitigation scheme. | 76  |

| 6.1 | Complexity of digital components for a 100x10 massive MIMO system.          | 95  |

| A.1 | Performance comparisons of digital polar front-end systems                  | 130 |

### Chapter 1

### Introduction

The groundbreaking digital revolution has refined the work and life styles of every individual. However, the gap between great application requirements and the enabling CMOS technology limitations is prominent. Therefore, design techniques to balance the quality and the power consumption of integrated circuits are demanded in the nano-CMOS era. This work promotes cross-layer optimizations for power and quality trade-off. It accepts errors that traditional designers advocated avoiding at all cost. The CMOS devices are working at their extremes with fewer safety margins. This enables extra power saving without noticeable quality degradations. This chapter introduces this work.

The chapter is structured as follows: Section 1.1 describes the motivation of this thesis. It reviews the contradiction between the need and the reality of current digital circuits and systems. A cross-layer optimization approach is therefore promoted (Section 1.2). Section 1.3 summarizes the scope of this thesis. Section 1.4 lists the main contributions of this work. Finally, Section 1.5 presents the structure of this thesis.

### 1.1 Context: motivation for power consumption and reliability trade-offs

The ubiquitous digital infrastructure and services have totally changed our way of life, leisure and our means of communication and information. The new generation is enjoying the conveniences offered by the computers, phones, gadgets, and varieties of smart IoT devices that exceed the visions of last generation's craziest sci-fi movies. The immersion of digital world is playing a key role in human lives (Fig. 1.1). According to [EMarketer, 2017], adults are spending more than 12 hours accessing digital data in 2017.

Figure 1.1: The world is immersed in digital services ([Kemp, 2017]).

The digital reality cannot be realized without the development of the enabling technologies. For the past few decades, we have seen marvelous breakthroughs in the domains such as personal computers, the internet, and mobile communications. Those breakthroughs, not only redefine the frontier of technologies but also expedite the mass adoption of them. For instance, almost three-quarters of the world's population now use a mobile phone, with the total number of unique global mobile users rapidly approaching 5 billion [Kemp, 2017]. The advance of technology is now spreading to the applications as artificial intelligence, smart vehicle, and IoT devices.

### 1.1.1 Demand: performance and power efficiency improvements

Consumers are demanding higher data volume, in a faster rate. For instance, the world monthly mobile data traffic goes steeply from 3.7 EB (Exabytes) in 2015, to 9.9 EB in 2017, and will increase to 30.6 EB by 2020 [Index, 2016]. The exponential growth of wireless data services driven by the mobile internet and smart devices has triggered the investigation of the 5G cellular network. The mobile phone of the future has to provide seamless connectivity anywhere and anytime. Around 2020, the new 5G mobile networks are expected to be deployed [Andrews, 2014]. These networks will support multimedia applications with a wide variety of requirements, including higher peak and user data rates (more

than 100 megabits per second for metropolitan areas [Osseiran, 2014]), reduced latency (less than 1 ms [Best, 2014]), enhanced indoor coverage, improved energy efficiency and so on.

Powering up those digital services requires a big amount of energy. Worldwide, data centers use about 400 terawatt-hours of electricity each year [Andrae, 2015]. That's a little more electricity than all of the United Kingdom uses. Already, they have mushroomed from virtually nothing 10 years ago to accounting for about 2 per cent of total greenhouse gas emissions [Bawden, 2016]. That gives it the same carbon footprint as the airline industry. If left unchecked, they could use almost 8,000 terawatt-hours by 2030. That's about the amount of electricity all of Europe and Africa and much of Asia use today. Another optimistic estimation predicts that the global IT services will consume 15% electricity production world-wise by 2025 [METI, 2008]. Considering the continuing demands for increased digital services, the energy efficiency for digital computation must be improved accordingly.

In the past few decades, the demands of increasing performance and power efficiency were realized with the CMOS technology progress. The complexity of integrated circuits has approximately doubled every 18 months; the cost per function has decreased several thousand-fold. The exponential growth has fit to the well-known Moore's Law (prediction) [Moore, 1998]. In the computer sector, the CPU had kept pace with the Dennard's scaling [Dennard, 1974], which suggests that the performance per watt also grows exponentially (Fig. 1.2). However, CPU performance, which is largely coupled with the clock speed, has stalled at around 2005, since the 65nm CMOS process. This suggests the end of the free lunch brought by the CMOS scaling [Sutter, 2005].

Figure 1.2: The free lunch of CMOS scaling is over [Sutter, 2005].

The power consumption (too high), heat (too much of it and too hard to dissipate), and current leakage problems are among the biggest challenges for the continuing of free-lunch scaling. Multicore parallelisms are employed to keep improving the performance, which eventually leads to new power challenges (dark silicon) that may end the multicore era [Esmaeilzadeh, 2011]. Nowadays, power consumption has become an, arguably the most, important metric for digital computing devices.

Apart from saving energy, another motivation to minimize power consumption is to fit digital chips into ubiquitous IoT devices, much of which are powered by batteries or energy harvesters [Bravos, 2005; Gyselinckx, 2005; Rawat, 2014]. Looking to the future, Cisco IBSG predicts there will be 25 billion devices connected to the Internet by 2015 and 50 billion by 2020 [Evans, 2011].

In summary, the increased IT service calls for, in addition to advanced CMOS technologies, successful enhancement in design of digital circuits and systems, to fulfill the performance and power efficiency requirements.

### 1.1.2 Reality: device and application uncertainties endanger successful designs

The variability has become a major roadblock to CMOS scaling (Fig. 1.3). Below the sub-65nm regime, transistors no longer act deterministically as a consequence of fluctuations in device parameters. This phenomenon is caused by the process challenges (lithography, etching, chemical mechanical polishing, etc.) [Ghosh, 2010]. These process challenges not only alters chip parameters (speed, area, power, etc.), they also result in functionality failures, e.g. stuck-in fault. The time-zero manufacturing process is not the only source of device uncertainties, chips also face aging problems during lifetimes. Worse still, the aging phenomena are uncertain in themselves. They heavily depend on the environment or workloads [Mintarno, 2013].

Figure 1.3: Digital designs must cope with permanent (time-zero and time-dependent) and temporary (environmental and runtime) uncertainties (variations), to reach a balance between power consumption and output quality.

Apart from these (semi-) permanent effects, environment [Unsal, 2006] (voltage, temperature, cosmic particle strikes, etc.) and runtime (timing errors, software, and user) variations also add uncertainties to chip designs. For instance, high energy particle strikes can lead to random bit flippings on storage elements. VOS (Voltage Over-Scaling) circuits [Hegde, 2004; Jeon, 2012] tries to save power by operates at a riskily-low supply voltage <sup>1</sup>, which produces uncertain errors. In summary, these uncertainties share a similarity that they only affect the IC temporaries.

The time-zero and time-dependent challenges are often regarded as a yield problem, which is mainly tackled by the IC foundries [Tsai, 2004]. In contrast, the fast changing runtime uncertainties are so dynamical that they cannot be simplified solved by traditional post-silicon testing [Nithin, 2010]. Therefore,

<sup>&</sup>lt;sup>1</sup>It is different from the sub-threshold computing technique [Dreslinski, 2010] where the  $V_{dd}$  and the clock frequency are very low. In contrast, the VOS reduces  $V_{dd}$ , but not the clock frequency. The operating voltage of VOS is much higher than the sub-threshold region.

runtime uncertainties management is a domain that is still wide open and much profitable for digital circuits and systems designers. The fact that these uncertainties only leads to temporary effects makes trading quality for power savings possible.

The source and effects of them are further explained in Section 2.1. To conclude, careful consideration of all those uncertainties is essential for successful digital circuit and system design.

### 1.2 Calling for cross-layer optimizations

### 1.2.1 Traditional pyramid-shaped design

Traditionally, the digital design flow follows a top-down procedure (Fig. 1.4). That is, the top-level design specs, e.g. quality, speed, power consumption, are assigned by system architects. The algorithm and circuit-level designers are forced to come up with solutions to fulfill these requirements. This rigid task dividing simplifies the design process, as fewer confusions during design are expected.

Figure 1.4: The traditional pyramid-shaped design flow leads to over-design at all levels (derived from [Hennessy, 2011]).

Following this design flow, the variations are traditionally tackled in particular levels. For instance, the process, voltage, and temperature (PVT) variations are packed up together and guaranteed with worst-corner safety margins at the circuit level (Section 2.2.1). Temporal degradation issues are hidden in the time-zero variations margins, albeit early works on designing with accurate time-dependent models [Liu, 2017] start to gain popularity.

A variety of safety margins are inserted in all levels of the design for manufacturing cost, reliable computing, acceptable device lifetime, device performance, etc [Austin, 2008]. If keeps inserting margins and being pessimistic, the gain obtained by the CMOS scaling will reduce and might eventually diminish (Fig. 1.5).

Figure 1.5: Over-designed guardbands diminish the benefits of CMOS scaling [Kahng, 2011].

The drawback is that, following the traditional pyramid-shaped design flow, smart engineering on quality and power consumption is usually limited to specific design levels, leading to only local optimal solutions. The application-level and the algorithm-level designs call for error-free results from lower levels, which makes lower level designs (e.g., at the architecture and circuit-level) unnecessarily complex sometimes. For example, chips should work at any temperature within the specification range, and thus transistors delays are pre-characterized on all temperatures. Circuits designers always try to avoid uncertainties and constrain chips to work equally on that (wide) delay range, which is not easy. Not many "if-then-else" cross-layer co-optimization are possible conventionally. The waste of resources of this worst-case guard-band is reviewed in Section 2.2.1.

Considering that the lower levels are utilizing too much resources to provide the higher level application service, the design flow is named as a pyramid-shaped method. In summary, the lack of information across design levels leads to wasted resources (in terms of power consumption and area cost). It is therefore calling for a new design and optimization paradigm.

### 1.2.2 Cross-layer optimization

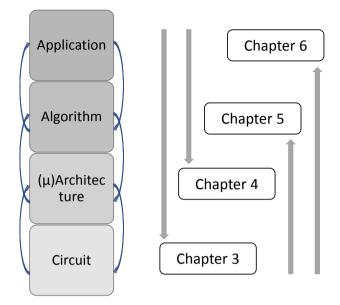

To exploit the resource waste in the pyramid-shaped design, this thesis promotes a cross-layer optimization design approach <sup>2</sup>. With this optimization paradigm, information are sharing across design layers for power savings or quality improvements. As will be demonstrated in the rest of this thesis, by extending optimization across different design levels, the over-design can be much reduced. This provides an advantage in conserving area and power consumption at the silicon foundation and increasing performance and quality at the applicationlevel. This paradigm is named as a tower-shaped design flow (Fig. 1.6), reflecting the aim that each design layer is utilizing just-needed resources, which avoids over-designs.

$<sup>^{2}</sup>$ Corss-layers in this work means to optimize across different design levels, which is different from the notion of "layer" from the Open Systems Interconnection (OSI) model.

Figure 1.6: Promoted tower-shaped cross-layer design approach reduces unnecessary power and area waste. This is achieved by exchanging information across design levels. Comparing with the pyramid-shaped cartoon (Fig. 1.4), the new paradigm requires less space at the low level, yet provides more rooms at the top of the tower (hence a tower rather than a pyramid). Chapter 3 and 4 transfers information from higher levels to circuit and micro-architecture levels. Chapter 5 and 6 mitigates lower level errors at algorithm and application levels.

In contrast of the tower-shaped design, errors are often permitted in the context of cross-layer optimizations. [Djahromi, 2007] showed that by allowing data bearing memories to have a controlled number of errors, significant gains in power consumption are possible. In fact, for a 3GPP modem, power savings of up to 17.5% are achievable assuming a 32nm technology. The Razor [Ernst, 2003] and ANT [Hegde, 1999a] techniques are excellent cross-layer optimization examples. They are discussed in details in Section 2.3.

[Carter, 2010; Mitra, 2010; GimmlerDumont, 2013] overviewed of the design techniques for cross-layer resilience. They highlights that distributing resilience and reliability across the system stack can improve performance and reduce power and area costs by taking advantage of the strengths of each layer and exploiting the characteristics of individual applications.

Admittedly, the design effort of this new paradigm is larger because a crosslayer information should be shared and evaluated. Though, its benefits are worth the effort. This thesis demonstrates that the cross-layer approach brings considerable benefits for digital circuits and systems, with limited design effort increase. For example, lower-level designs assume (predicate) some properties of the higher-level, which reduce the power cost once predicated successfully; lower-level designs generate some errors under the worst situations, which will be handled by the higher-level designs.

## 1.3 Thesis scope

This thesis aims to reduce safety margins and saving power. Runtime adjusting approaches are employed to exploit those margins. More specifically, this work mainly handles the environmental and runtime uncertainties. The reason is that, these uncertainties are so dynamical that they cannot be simplified solved by traditional post-silicon testing [Tsai, 2004; Nithin, 2010]. It not only responses to the environmental changes as the DVFS techniques (Section 2.2.2), but also allows occasional errors to propagate through different levels (e.g. Section 5). Techniques in this work, however, also exploit margins for slowly changing process variations (time-zero and time-dependent), assuming that they are already packed in the safety margin. The permanent breakdowns are not covered in the thesis. This is because time-zero breakdowns are classified as yield problems and are mostly taken care of by semiconductor foundries; workload-dependent aging effects are considered by EDA tools recently [Karapetyan, 2015].

The targeted applications of this thesis are soft-quality requirement digital signal processing devices. These cross-layer optimizations are particularly beneficial in the context of soft-quality requirement systems. In these systems, errors are acceptable as long as the system output still meets the requirements. For instance, the transient error in a wireless communication application can easily be tolerated by the symbol detector, considering that the error vector magnitude is allowed [Karakonstantis, 2012b]. This distinguishes from the general-purpose computer case [Carter, 2010] where usually no errors are permitted. Another example is video processing applications, where skipping few erroneous pixels can be tolerated [Driscoll, 2003]. This leaves plenty of spaces for quality-power trade-offs.

Therefore, in this work, the uncertainties incurred errors are allowed to propagate to the algorithmic and application-level. The end result is a good balance between the quality and power consumption. In specific, Chapter 3 firstly models the algorithm-level impact of random errors, in the circuit-level, without digging into the algorithm. It then provides valuable guidelines to selectively harden designs against random errors at the circuit-level. Chapter 4 predicates programs' behavior, and modifies the microarchitectural structure, which leads to power savings for typical usages. Chapter 5 mitigates circuit-level errors at the microarchitecture and eventually the algorithm-level, leading to a graceful quality degradation. Chapter 6 demonstrates that lower-level generated errors can be handled at the application-level. This provides opportunities to embrace hardware uncertainties for power saving. It takes the Massive MIMO wireless communication application as a case-study and demonstrates its resilience to lower-level errors. The chapter, therefore, encourages to use low-power yet erroneous components in the Massive MIMO.

## 1.4 Main contributions

This work has contributed to better power solutions of digital designs in scaled CMOS, through a cross-layer optimization. These approaches were demonstrated in the content of wireless communication applications. The main research contributions of this thesis are summarized below. A more elaborate version of the main messages is provided in Chapter 7.

- Introduction of an analytical circuit-level random error effects model (Chapter 3). This thesis proposed a graph travel approach that solves the model. It is shown how a graph based scheme can identify the sensitivity of indivisual Flip-Flops. This helps to selectively protect only those. It also demonstrated the scalability and effectiveness of the model on ISCAS and ITC benchmark circuits. Finally, this work validated the benefits of the model on an FFT processor design that reduces soft-error hardening overhead. This work was unveiled in [Huang, 2016b].

- Proposed a novel fine-grain hardware-switch scheme to save power in embedded processors (Chapter 4). The thesis applied the proposed scheme to the multiplier unit of an OpenRISC processor. This technique competes with the idea of VLIW based SIMD instructions that requires large compiler modification. It demonstrated power savings on 11 typical signal processing applications, e.g. FFT, IIR, AES, JPEG. This work was published in [Huang, 2016c].

- Application of Razor circuit-level error detection techniques with error mitigation achieved through an algorithmic approach. Proposed a novel computation-skip scheme to mitigate errors for recursive applications (Chapter 5). It saves power saving by reducing the supply voltage,

exploiting not only the error-free but also error resilient safety marigns. This is achieved by skipping part of the computation and sacrificing some accuracy. The thesis implemented the scheme on a CORDIC hardware accelerator in 28nm CMOS technology with standard digital design flow. The work was published in [Huang, 2014], and elaborated in [Huang, 2016d].

• Investigation of application-level error absorption and handling for Massive MIMO wireless communication applications (Chapter 6). It demonstrated the error resiliency of Massive MIMO systems under hardware errors and even antenna outage. It also proposed a damage control strategy for Massive MIMO applications. The work is published in [Huang, 2017].

## List of publications

The list of publications can be found in the attached Curriculum Vitae section.

## 1.5 Thesis structure

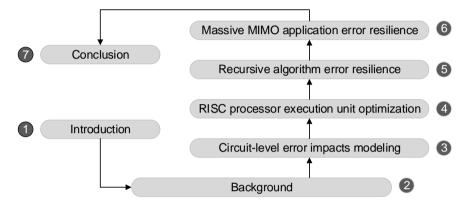

In this thesis, cross-layer optimization are performed for digital circuits and systems for power consumption and reliability trade-off (Fig. 1.7).

Chapter 2 reviews techniques for power and quality tradeoffs. It starts with device-level phenomena of variations. The chapter then reviews the worst-case design and the adaptive scaling method that tunes supply voltage to save power. Finally, the benefit of the cross-layer VOS (Voltage Over-Scaling) approach is justified.

As shown in Fig. 1.6, Chapter 3 develops a gate-level random error model, SERIAL. It models the importance of flip-flops regarding their impact on algorithm outputs. The efficiency and effectiveness of the model are shown in typical circuits, including ISCAS and ITC benchmarks, and an LDPC decoder. Finally, the model is applied to design a reliable FFT processor.

In Chapter 4, a microarchitecture-level fine-grain hardware-switch scheme for embedded processors power savings is proposed. In specific, the chapter modifies the multiplier unit of the OpenRISC platform. It demonstrates power savings on typical signal processing applications.

Chapter 5 proposes a method for cross-layer error interplay between the circuitlevel and the algorithm-level. It presents a computation-skip scheme to mitigate errors in recursive applications. The error mitigation scheme, together with the state-of-the-art timing error detection benchmark, are applied to a hardware CORDIC accelerator. The CORDIC accelerator is processed and verified in a standard 28nm CMOS process with only standard-cells.

Chapter 6 presents the application-level error absorption and handling. It focuses on a Massive MIMO communication case-study. This chapter assesses hardware random errors (VOS) and antenna outage impacts. Finally, damage control strategies are proposed.

Figure 1.7: Structure of the thesis and overview of the chapters.

## Chapter 2

## Background: pessimistic safety margins should be exploited

This chapter reviews techniques for power and quality trade-offs. It firstly introduces PVT (process, voltage, and temperature) variations and reliability threats. It then reviews the worst-case design and the adaptive scaling method that tunes supply voltage to save power. Finally, the benefit of the cross-level VOS (Voltage Over-Scaling) approach is discussed.

The rest of this chapter is structured as follows: Section 2.1 explains the variations from process, environment and runtime changes. Section 2.2 analyses two conventional methods, i.e. the worst-case approach, and dynamical voltage scaling, which handle variability. The limitation of the worst-case approach is pointed out. The benefits and disadvantages of adaptive scaling are also reviewed. Section 2.3 discusses adventurous VOS methods that reach a balance between power consumption and output quality. Finally Section 2.4 concludes this chapter.

## 2.1 Uncertainties in circuit paramaters

IC design has always been subject to variations which make it impossible at design time to determine exactly how a circuit will perform. Worse still, these

uncertainties have become increasingly significant as a result of the scaling of technology. To cope with those variations, the concept of design margin has been introduced in the design process.

This section reviews the cause, and more importantly the effects, of the longterm and short-term variations, from a digital circuits and systems designer's perspective. This thesis does not try to model for these variations directly. Instead, it saves power by reducing over-pessimistic safety margins.

### 2.1.1 Process variations and aging effects

Process variations and aging effects are long-term or permanent uncertainties for IC. They result to parametric variability (in area, speed, power consumption) and functional breakdowns. The parametric variability effects are reviewed in this subsection, because they usually lead to pessimistic parametric safety margins. Functional breakdowns, e.g., stuck-in errors, electrical stress, burn-in, [Veendrick, 2008], are not covered in this work. The reason is that those extra threats have very specific characteristics that require individual studies. Another reason is that, most of them have already been addressed properly in the subjects of design-for-testability [Fujiwara, 1985] and design-for-manufacturability [Strojwas, 1989; Chiang, 2007; Orshansky, 2007].

#### Time-zero process variations

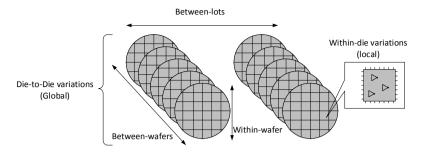

Spatial process variations are deviations of IC parameters compared to their targeted values at the design time. They are created by the limited controllability of a manufacturing process [Nourani, 2006]. The origins of these variations are categorized into inter-die (global) and intra-die (local) components [Ghosh, 2010]. As plotted in Fig. 2.1, the global components consist of between-lots, between-wafers, and within-wafer variations. The local components are the within-die variations.

Figure 2.1: Spatial process variations consist of global and local components.

Global variability refers to the parameter changes for identical devices/interconnects separated by a longer distance, or fabricated at a different time, that result from factors such as processing temperature, equipment/tool properties, etc. between different runs, lots, wafers and dies [Saha, 2010]. Therefore, they impact equally on all transistors and interconnects on a die [Bowman, 2009a].

On the other hand, local variability causes parameter mismatch between identically designed devices/interconnects across a short distance within a die [Saha, 2010; Ohnari, 2013]. Typical causes are fluctuations in length, width, oxide thickness, flat band control, and the number of dopants [Herr, 1986].

Conventionally, the main focus was on global variations. This is convenient for designers, as all transistors on the same IC can be modeled with an equal offset. However, local variations have recently entered into the interest zone, and have been pronounced more as a consequence of the aggressive technology scaling, increased chip area, clock frequency, and leakage power distributions [Boning, 1996; Tschanz, 2002; Bowman, 2002]. Moreover, it was observed that local variations can have a much higher impact compared to global variations, e.g. lithography and etch technology can achieve 5% mismatch of wafer-scale metal width uniformity, whereas within-die variations were reported on the order of 15% [Dai, 2001].

The most prominent sources of the variabilities in nano-CMOS transistors are analyzed in [Wang, 2011; Asenov, 2007], which are Front-end-of-the-line (FEOL) random process variability sources, namely Random Discrete Doping (RDD), Line Edge Roughness (LER); PolySilicon (Poly-Si) Granularity (PSG), Metal Gate Granularity (MGG), and Oxide Thickness Variation (OTV).