# Polyhedral AST generation is more than scanning polyhedra

GROSSER TOBIAS, INRIA and ÉCOLE NORMALE SUPÉRIEURE <sup>1</sup>

VERDOOLAEGE SVEN, INRIA, ÉCOLE NORMALE SUPÉRIEURE and KU Leuven<sup>2</sup>

COHEN ALBERT, INRIA and ÉCOLE NORMALE SUPÉRIEURE

Abstract mathematical representations such as integer polyhedra have shown to be useful to precisely analyze computational kernels and to express complex loop transformations. Such transformations rely on Abstract Syntax Tree (AST) generators to convert the mathematical representation back to an imperative program. Such generic AST generators avoid the need to resort to transformation-specific code generators, which may be very costly or technically difficult to develop as transformations become more complex. Existing AST generators have proven their effectiveness, but they hit limitations in more complex scenarios. Specifically, (1) they do not support or may fail to generate control flow for complex transformations using piecewise schedules or mappings involving modulo arithmetic; (2) they offer limited support for the specialization of the generated code exposing compact, straightline, vectorizable kernels with high arithmetic intensity necessary to exploit the peak performance of modern hardware; (3) they offer no support for memory layout transformations; (4) they provide insufficient control over the AST generation strategy, preventing their application to complex domain-specific optimizations.

We present a new AST generation approach that extends classical polyhedral scanning to the full generality of Presburger arithmetic, including existentially quantified variables and piecewise schedules, and introduce new optimizations for the detection of components and shifted strides. Not limiting ourselves to control flow generation, we expose functionality to generate AST expressions from arbitrary piecewise quasi-affine expressions which enables the use of our AST generator for data-layout transformations. We complement this with support for specialization by polyhedral unrolling, user-directed versioning, and specialization of AST expressions according to the location they are generated at, and complete this work with fine-grained user control over the AST generation strategies used. Using this generalized idea of AST generation, we present how to implement complex domain-specific transformations without the need to write specialized code generators, but instead relying on a generic AST generator parametrized to a specific problem domain.

Categories and Subject Descriptors: D.3.4 [**Programming Languages**]: Processor – Compilers, Optimizations

General Terms: Algorithms, Performance

Additional Key Words and Phrases: Polyhedral compilation, code generation, unrolling, index set splitting, Presburger relations

# **ACM Reference Format:**

ACM Trans. Program. Lang. Syst. V, N, Article A ( 2015), 50 pages.  $\tt DOI:http://dx.doi.org/10.1145/2743016$

#### 1. INTRODUCTION

The development of high-level optimizations for domain-specific or general purpose compilers can often be conceptually divided into two parts: the design of a high-level

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org.

© 2015 ACM 0164-0925/2015/-ARTA \$15.00

DOI: http://dx.doi.org/10.1145/2743016

<sup>&</sup>lt;sup>1</sup>Part of this work was performed while working for ETH Zurich.

<sup>&</sup>lt;sup>2</sup>Part of this work was performed while working for LIACS, Leiden.

A:2 Grosser et al.

optimization strategy and the generation of program code according to this optimization strategy. In many cases, the interesting scientific contribution is the new optimization strategy. However, in practice, significant efforts are put into the generation of efficient program code.

For loop programs with affine (and even non-affine [Venkat et al. 2014]) control flow, it is common to automatically generate optimized program code from an abstract description that models each statement instance (i.e., each dynamic execution of a statement inside a loop nest) and each array element individually through the use of a compact representation such as polyhedra [Loechner and Wilde 1997] or Presburger relations [Pugh and Wonnacott 1994]. Optimizations, for example those of Pugh and Rosser [1997; Wonnacott [2002; Bondhugula et al. [2008; Kong et al. [2013; Zuo et al. [2013] and Bandishti et al. [2012], are described by modifying an abstract schedule that defines the execution order of the individual statement instances in a program. According to this schedule, imperative program code is (re)generated using a technique called polyhedral scanning [Ancourt and Irigoin 1991], code generation [Kelly et al. 1995; Bastoul 2004], or, more accurately, Abstract Syntax Tree (AST) generation. Decoupling the optimization and program generation steps not only reduces the time needed to implement a certain optimization strategy, it also speeds up the evaluation of new optimization strategies [Pouchet et al. 2007; Pouchet et al. 2008]. Furthermore, being able to describe transformations on a highly abstract level enables the development of complex transformations [Grosser et al. 2014] relying on the AST generator to generate efficient imperative code.

Even though AST generators have many benefits, existing approaches focus on control flow generation [Bastoul 2004; Kelly et al. 1995; Chen 2012], provide only rudimentary support for the specialization of the generated expressions, and limited control over code size vs. control overhead. These limitations often prevent their wider usage. Missing support for generating user-provided AST expressions, e.g., to describe memory locations, prevents their application to data-layout transformations [Wonnacott 2002; Yuki et al. 2012; Henretty et al. 2013] or, to the mapping of data to software managed caches [Holewinski et al. 2012]. Also, existing AST generators may produce multiple code versions according to specific parameter values, to reduce control overhead, but existing approaches do not natively support the generation of specialized code. This would be particularly helpful for the separation of full and partial tiles [Ancourt and Irigoin 1991; Goumas et al. 2003; Kim et al. 2007] or for the generation of specialized code to handle possibly different conditions at iteration space boundaries. Instead, versioning has to be enforced by generating several distinct copies of each statement in the input description [Chen et al. 2008]. Similarly, performing unrolling during AST generation is only possible by duplicating statements in the input description [Chen et al. 2008; Bondhugula et al. 2008; Shirako et al. 2014]. Besides being conceptually unsatisfying, duplicating statements causes serious problems. Firstly, by purposefully hiding the fact that statements are identical, the AST generator is forced to generate duplicate code for them in all cases, missing redundancies in complex expressions and missing opportunities to factor colder parts of the code. Secondly, duplicating statements increases the complexity of the polyhedral operations involved in the generation of imperative control flow, supporting optimizations such as full/partial tile separation, and supporting expression specialization or simplification for modulo arithmetic. If we now wish to minimize code size for colder parts of the iteration space (e.g., the partial tiles), we run into the next limitation. Even though AST generators provide basic control over the desirable aggressiveness in separating statements or control flow specialization (conditional hoisting), the level of control is way too coarsegrained in existing methods and tools. Also, no guarantees are given about the maximal number of loop nests and the maximal number of statements generated, which is problematic for scenarios where code size is a major concern, such as AST generation for many-core targets with software-managed caches, embedded processors, and high-level synthesis [Zuo et al. 2013]. Overall, existing approaches and tools are in many ways not yet mature for complex AST generation problems.

This work presents an integrated AST generation approach that, in addition to classical control flow generation, allows the generation of AST expressions from arbitrary user-provided piecewise affine expressions.<sup>3</sup> We define a fine-grained "option" mechanism that enables the user to request maximal specialization where needed while retaining control over code size. To enable aggressive specialization, we allow the user to instruct the AST generator how to version the code, we provide an integrated polyhedral unrolling facility, and we make sure that AST expressions are specialized according to the context they are generated in. Doing so is essential to correctly model the floor-division and modulo arithmetic arising from abstract transformations of the program, and to cast these expressions to efficient remainder and integer divisions, or to lower-complexity operations, as provided by existing instruction set architectures and programming languages. Finally, we present a miscellaneous set of optimizations that improve the quality of the generated code, in comparison to existing polyhedral scanning tools, but also optimizations made necessary to cover the wider application scenarios of our AST generator.

Our contributions are as follows:

- AST generation with complete support for *Presburger relations* including support for *piecewise schedules*, and their use in expressing *index set splitting as a schedule*only transformation.

- An aggressive simplification of *AST expressions* generated from *piecewise quasi-affine expressions* within the context of their position in the AST, including the *detection of modulo and division operations*. The generation of simplified AST expressions is not only used to construct loop bounds and if conditionals from within the AST generator, but is also exposed to the user, who can use this functionality to generate custom index expressions and run-time checks.

- Fine-grained options to control AST generation including an atomic option that can be used to control code size and to ensure that no program statements are duplicated.

- Specialization through polyhedral unrolling and user directed versioning, in particular the user can specify a subset of the schedule space (e.g., full tiles) that should be isolated from the rest of the schedule space (i.e., partial tiles).

- Algorithms for improved stride detection and the detection of reorderable components.

- AST generation for structured schedules expressed as *schedule trees*.

- Evaluation in an advanced domain-specific optimizer and comparison to state-ofthe-art code generation techniques.

The remaining content of this paper is organized as follows. Section 2 gives a high-level overview of our new AST generation approach and presents new, illustrative use cases. We then present theoretical background in Section 3, the data structures involved in Section 4, our core AST generation approach in Section 5, and its extension to schedule trees in Section 6. We finish with a set of experiments in Section 7, the discussion of related work in Section 8, and the conclusion in Section 9.

<sup>&</sup>lt;sup>3</sup>The entire approach is available at http://repo.or.cz/w/isl.git in the development version isl-0.14-368-g23e8573, which will be included in the next releases of isl.

A:4 Grosser et al.

#### 2. A NEW APPROACH TO AST GENERATION

To give an idea of the new AST generation concepts proposed in this work, we present them in the context of a complex AST generation scenario. One such ideal scenario is our recent work on hexagonal/parallelogram tiling [Grosser et al. 2014], a domain specific optimization for generating efficient CUDA code for iterative stencil computations. It is implemented on top of PPCG [Verdoolaege et al. 2013], a generic C to CUDA/OpenCL translator, which uses Presburger relations to describe both the computation itself and the program transformation to apply. Taking advantage of such an abstract mathematical description, a new tiling scheme has been developed that involves complex geometric shapes to address the most important performance issues of compiling iterative stencils for GPUs, including the usage of shared memory, the optimization of data-transfers, the increase of arithmetic intensity, the exploitation of multiple levels of parallelism, and the avoidance of thread divergence. In the following paragraphs, we show how we obtained highly efficient code using our new generic AST generation approach without the need to develop a domain- or optimization-specific generator.

When translating C code to CUDA, we start from code consisting of compute statements and loops. To simplify the exposition, let us first assume in this section that the program consists of a single perfectly nested set of loops, with one outer sequential loop, a set of inner parallel loops, and a single compute statement. To generate CUDA code for this computation it is necessary to obtain a set of kernels that can be launched sequentially and that each expose two levels of parallelism: coarse grained parallelism, which will be mapped to so-called CUDA thread blocks, and fine grained parallelism, which will be mapped to so-called CUDA threads. To obtain these two levels of parallelism we divide the set of individual computations (statement instances) enumerated by these loops into subsets (tiles). We do this by computing a polyhedral schedule that enumerates the set of statement instances with two groups of loops. A set of outer loops that enumerate the tiles (tile loops) and a set of inner loops (point loops) that enumerate the statement instances that belong to a certain tile. The first AST generation problem we encounter is that the hybrid-hexagonal schedule defining the tile shapes decomposes the computation into phases and applies to each phase a different schedule. This results in a piecewise schedule from which an AST needs to be generated.

As a next step, we map the tile and point loops to a fixed number of thread blocks and threads. We start by looking for a set of parallel point loops and a set of parallel tile loops. We then strip-mine each loop by the number of thread blocks and threads. For instance, to map a point loop with n iterations to a set of 1024 kernel threads, we stripmine the loop by a factor of 1024 such that each 1024<sup>th</sup> iteration is executed by the same thread. The next step is to produce a piece of CPU code that schedules instances of an accelerated kernel, and the kernel code itself that defines the computation of a specific thread in a specific thread block. No actual loops are generated that enumerate the set of thread blocks and threads, but instead the CUDA run-time and hardware spawns a set of blocks and threads and provides the block and thread ID as a parameter to each thread executing the kernel code. To model this, we first generate the outer loop, then we use a *nested context* to introduce the block and thread identifiers and, finally, we generate kernel code that can reference values in the outer CPU code, taking into account the AST generation context of the outer C code as well as the constraints on the kernel and thread identifiers. Exploiting this information is very important to generate high-quality code.

When generating kernel code we also need to rewrite all array subscripts in our compute statement. Traditionally this is done textually by replacing all references to

Fig. 1: Copy code from hybrid hexagonal/parallelogram tiling (a single loop)

old induction variables with expressions that compute the values of the old induction variables from new induction variables. When translating an access A[i+1] where i now is expressed as c0 + 1, a classical rewrite would yield A[(c0 + 1) + 1]. With our new approach we represent the expression i+1 itself as a piecewise quasi-affine expression, perform the translation on the piecewise quasi-affine expression, simplify the resulting expression and use our AST generator to generate an AST expression from this piecewise quasi-affine expression. As a result we obtain the code A[c0 + 2]. In this example the only benefit is increased readability, as any compiler would constant-fold the two additions. However, in general, this concept is a lot more powerful. It allows the specialization of expressions according to the context in which they are generated. If, for instance, an access A[i == 0 ? N - 1 : i - 1] is scheduled in a tile where we know i is never 0, we can simplify the access to A[i - 1]. This simplification removes the overhead of boundary condition handling from the core computation, a transformation for which a normal compiler misses context information and which traditionally requires specialized statements for boundary and core computations. With our AST generation approach, statements are automatically specialized as soon as boundary computations and core computations are generated as specialized AST subtrees. This is very natural for an AST generator that allows user-directed versioning.

After having generated basic CUDA code including the rewritten data accesses, we can start to optimize the code. An essential optimization is to switch from the use of slow "global memory" to the use of fast, manually managed "shared memory". To do so we need to change the code of each tile such that, before the actual computation takes place, the relevant data from global memory is copied into shared memory, and at the end, the modified data is copied back from shared to global memory. To perform the computation in shared memory, we need to adjust all memory accesses such that they point to the new shared memory arrays and the corresponding locations. How exactly the mapping is computed is outside the scope of this paper, but how we generate the relevant code is interesting. We derive from our mapping a set of piecewise quasi-affine expressions that define the new data locations and generate AST expressions for them, relying on the AST generator to ensure that efficient code is generated. This approach enables us to use possibly complex mappings, without writing specialized code generation routines. To create the code that moves the data, we create new statements that copy data from a given global memory location to a given shared memory location and vice versa. In case there is more data to copy than there are threads we use a modulo mapping to assign data locations to threads. Figure 1 shows the code generated to copy data back to global memory. There are various interesting observations possible. First, we see that our modulo expressions have been mapped to the C remainder operator %, which will be translated to fast bitwise operations in case the divisor is a powerof-two constant and the compiler can derive that the dividend is always non-negative. Using the C remainder operator is only possible because we have context information

A:6 Grosser et al.

```

A[0][6 * b0 + 1][128 * g7 + (t1 + 125) % 128) - 1] = ...;

A[0][6 * b0 + 2][128 * g7 + (t1 + 127) % 128) - 3] = ...;

if (t1 <= 2 && t1 >= 1)

A[0][6 * b0 + 2][128 * g7 + t1 + 128] = ...;

A[0][6 * b0 + 3][128 * g7 + (t1 + 127) % 128) - 3] = ...;

if (t1 <= 2 && t1 >= 1)

A[0][6 * b0 + 3][128 * g7 + t1 + 128] = ...;

A[0][6 * b0 + 4][128 * g7 + (t1 + 125) % 128) - 1] = ...;

A[1][6 * b0 + 1][128 * g7 + (t1 + 126) % 128) - 2] = ...;

A[1][6 * b0 + 2][128 * g7 + (t1 + 126) % 128) - 2] = ...;

if (t1 <= 3 && t1 >= 2)

A[1][6 * b0 + 2][128 * g7 + t1 + 128] = ...;

A[1][6 * b0 + 3][128 * g7 + (t1 + 126) % 128) - 2] = ...;

if (t1 <= 3 && t1 >= 2)

A[1][6 * b0 + 3][128 * g7 + t1 + 128] = ...;

A[1][6 * b0 + 4][128 * g7 + (t1 + 126) % 128) - 2] = ...;

```

Fig. 2: Copy code from hybrid hexagonal/parallelogram tiling (unrolled)

about the value of t1. Otherwise we would need to fall back to expensive floord or intMod expressions, dealing with arbitrary (possibly negative) integers, as the state-of-the-art AST generators CLooG and CodeGen+ do. Secondly, we see that we generate a reasonably dense loop nest that enumerates the statements. Because of the presence of existentially quantified variables in the input description, this is by itself non-trivial (see Section 7.3).

Nevertheless, we observe that the generated code is not very efficient. Every loop iteration performs very little computation and evaluates a complex condition. One might hope the condition could be simplified further, but unfortunately the data modified when moving a 5-point stencil forming a cross over a hexagonal tile shape is by itself already non-convex. Applying another level of modulo scheduling makes the necessary compute pattern even more complex, such that obtaining a simpler loop structure is difficult. However, by using *polyhedral unrolling* on the inner three loops and by specializing the statements according to the iteration they are unrolled for, we can remove almost all control overhead. The result is shown in Figure 2. The code is very smooth and each array subscript is specialized to the specific location. We can also see that for the conditionally executed statements the subscripts are optimized according to the conditions such that the remainder operations disappear entirely. Unrolling this code is not trivial, as it needs to be performed in the presence of multiple loop boundaries as well as strides and we need to support the generation of guarded instructions when unrolling. The guarded instructions at the innermost level are very cheap on a GPU, as they can be implemented as predicated instructions. In this small example this is not very visible, but for realistic tile sizes a larger number of statements share the same conditions. We perform similar unrolling for the compute code in our kernel to ensure sufficient instruction level parallelism is available.

The code in Figure 2 is now close to optimal. However, so far we have only looked at a simplified example, a single tile that does not touch any iteration space boundaries. If the iteration space boundaries are taken into account, the generated code becomes a lot more complex. To ensure we can still use the "close to optimal" code most of the time, we use *user directed versioning* to isolate the core computation (the full tiles) from the set of tiles that need to take into account the boundary conditions (partial tiles). Doing so gives us maximal specialization and best performance. However, we now specialize and unroll not only the core computation, but also the code that was introduced to handle the boundary cases, which increases the size of the generated

code as well as the time necessary to generate it. When targeting a GPU this may be acceptable, but for FPGAs [Zuo et al. 2013] the cost may be prohibitive. This problem can be easily addressed by using *fine-grained options* to limit the amount of unrolling and specialization in the boundary tiles.

In summary, extending AST generation beyond the creation of control flow makes it possible to use automatic AST generation in complex scenarios. Even though existing AST generators combined with workarounds such as duplicating statements before running the AST generator can be used to solve some of the previously mentioned AST generation issues, such workarounds only exist for some features, they apply only in simple special cases and often inhibit other necessary transformations. By instead carefully integrating several important new extensions into a single AST generation approach, we significantly extend the concept of automatic AST generation such that it is usable in complex AST generation scenarios. We ensure that the different features do not block each other, but when combined provide novel opportunities and solutions to complex AST generation problems. As a result we hope to not only significantly simplify AST generation, but to enable its use in new optimization scenarios.

### 3. POLYHEDRAL MODEL

The polyhedral model [Feautrier and Lengauer 2011] is a powerful abstraction for analyzing and transforming (parts of) programs that are "sufficiently regular". The key feature of this model is that it is instance based. That is, each statement instance (i.e., each dynamic execution of a statement inside a loop nest) and each array element is treated individually through the use of a compact representation such as polyhedra [Loechner and Wilde 1997] or Presburger relations [Pugh and Wonnacott 1994]. A program is typically represented using *iteration domains*, containing the statement instances, *access relations*, mapping statement instances to the accessed array element(s), *dependences*, relating statement instances that depend on each other, and a *schedule*, assigning an execution order to the statement instances.

In terms of AST generation, the most relevant elements are the iteration domain and the schedule, where the iteration domain describes the statement instances that need to be executed and the schedule describes the order in which they should be executed. For the iteration domain, we use the representation proposed by Verdoolaege [2011], where each statement instance is represented by a name (identifying the statement) and a tuple of integers (identifying the instance). For each statement, the instances in the iteration domain are described using a *Presburger formula*. We call such a set a *named Presburger set*. Other representations of iteration domains can easily be converted to such a named Presburger set.

Before defining Presburger formulas, let us first consider *affine* expressions, which are terms composed of variables, integer constants, symbolic constants, addition (+) and subtraction (-). Multiplication by an integer constant is available as syntactic sugar for repeated addition or subtraction. Symbolic constants have a fixed but unknown value and typically represent problem sizes. A *quasi-affine* expression additionally allows integer division by an integer constant ( $\lfloor \cdot / d \rfloor$ ). A Presburger formula is then constructed from quasi-affine expressions, comparison ( $\leq$ ) and the first order logic operators: conjunction ( $\wedge$ ), disjunction ( $\vee$ ), negation ( $\neg$ ), existential quantification ( $\exists$ ), and universal quantification ( $\forall$ ). A *piecewise quasi-affine* expression is a list of pairs of named Presburger sets and quasi-affine expressions. The sets are pairwise disjoint and the value of the piecewise quasi-affine expression at a given point is equal to the value of the quasi-affine expression associated to the set that contains the point.

Binary relations on pairs of named integer tuples can be defined in a similar way and are called *named Presburger relations*. Although we will use a more structured representation for schedules in Section 6, it is instructive to consider the basic case of rep-

A:8 Grosser et al.

```

for (int i = 0; i < n; ++i) {

S1: s[i] = 0;

for (int j = 0; j < i; ++j)

S2:       s[i] = s[i] + a[j][i] * b[j];

S3: b[i] = b[i] - s[i];

}</pre>

```

Fig. 3: Example Program

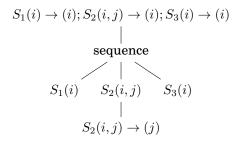

resenting schedules as named Presburger relations proposed by Verdoolaege [2011]. These named Presburger relations associate an integer tuple to each statement instance and the execution order expressed by the schedule is given by the lexicographic order of these integer tuples. Consider for example the program in Figure 3. The iteration domain is

$$\{ S1(i) : 0 \le i < n; S2(i,j) : 0 \le j < i < n; S3(i) : 0 \le i < n \}.$$

One way of expressing the original execution order is the schedule

$$\{S1(i) \to (i,0,0); S2(i,j) \to (i,1,j); S3(i) \to (i,2,0)\}.$$

(2)

That is, the statement instances are first ordered according to the first (or only) element in their instance identifier tuple. Then, for those statement instances that have the same value, the instance of S1 is executed before the instances of S2, which in turn are executed before the instance of S3. Finally, the instances of S2 are executed according to the second element in its instance identifier tuple. For the other two statements all instances are already scheduled apart, so the final schedule coordinate does not need to make a distinction between instances. It may therefore be set to an arbitrary value (here 0).

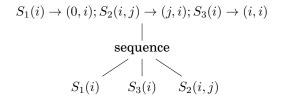

An alternative execution order may be obtained through the schedule

$$\{S1(i) \to (0, i, 0, 0); S2(i, j) \to (1, i, 1, j); S3(i) \to (1, i + 1, 0, 0)\},\$$

where all instances of S1 are executed before any instance of S2 or S3. Among the instances of S2 or S3, those where the first dimension of S2 is one more than the single dimension of S3 are executed together, with the S3 instance being executed before the S2 instances.

The purpose of the AST generator is to construct an AST that visits the elements of the iteration domain in the lexicographic order of the integer tuples assigned to the iteration domain elements by the schedule. The construction uses several operations on named Presburger sets and relations available in isl [Verdoolaege 2010], including domain and range of a relation, intersection, union, set difference, projection, shared constraints ("simple hull"), simplification of a set (relation) with respect to known constraints ("gist"), integer affine hull and coalescing (replacing pairs of disjuncts by single disjuncts without introducing spurious elements) [Verdoolaege 2015]. All these operations commonly change the elements contained in the sets (relations) they operate on with the exception of coalescing, which only affects the *representation* of a set (relation). Note that the AST generator presented in this paper does *not* use the convex hull operation, as this may introduce constraints with large coefficients.

### 4. DATA STRUCTURES

The core AST generation algorithm translates schedule constraints into lower and upper bounds of the for loops of the generated AST. In order to be able to construct the for loops, the algorithm may need to break down the schedule domain into several pieces, resulting in a tree of for loops generated from outermost to innermost. There

may, however, also be other constraints that cannot be directly encoded in the lower and upper bounds of for loops and that need to be generated as if conditions instead. In general, we want these conditions to be inserted as high up as possible. On the other hand, we do not want to insert too many redundant conditions, while some conditions may only be redundant with respect to the code that is generated underneath those conditions. Moreover, some constraints, especially disjunctive constraints, may only get discovered at later stages and need to be hoisted up. The AST therefore cannot be constructed in a single pure pre-order depth-first traversal of the schedule. Instead, we perform a single depth-first traversal with some pre-order operations, mainly decomposing the schedule, and some post-order operations, actually constructing the AST. The details of the algorithm will be described in Section 5. In this section, we introduce vocabulary and data structures for passing information up and down the depth-first traversal. These are necessary to describe the current part of the decomposed schedule, the information that is passed down, the actual AST that is being constructed, and the information that is passed up.

# 4.1. Executed Relation

In the base case of the AST generation algorithm, the schedule is given by a named Presburger relation mapping statement instances to their relative multi-dimensional execution times. The loops in the generated AST are derived from these multi-dimensional execution times. During the AST generation, it is therefore more natural to consider the inverse of this schedule relation, which we call the *executed relation* and which maps execution time vectors to the statement instances that should be executed at those times. For example, given the schedule relation in (3), the (initial) executed relation (without domain constraints) is

$$\{(0, s_1, 0, 0) \to S1(s_1); (1, s_1, 1, s_2) \to S2(s_1, s_2); (1, s_1, 0, 0) \to S3(s_1 - 1)\}.$$

(4)

The levels of the depth-first pass over the schedule correspond to the input dimensions of this executed relation. At each level, the domain of the executed relation is broken up into pieces along that dimension and each piece of the executed relation is considered in turn.

#### 4.2. Stock

The AST node corresponding to a dimension in the domain of the executed relation is constructed upon leaving that level during a depth-first traversal. However, the main information about the AST node is already available when that level is first entered. Some of this information needs to be stored and forwarded through the traversal. We introduce the *stock* to collect this information that can be used to simplify the descendant AST nodes. The stock mainly keeps track of two pieces of information, the conditions on symbolic constants and outer loop iterators that are known to hold at the current position, and a mapping from loop iterators to schedule dimensions. At each level of the depth-first traversal, a new stock is created that is initialized from the stock passed down from the higher level.

The conditions come in two groups, the *generated* conditions and the *pending* conditions. The generated conditions are those for which the algorithm has already decided that they *will* be enforced by the outer nodes in the AST. These are typically the loop bounds on the outer loop nodes. The pending conditions are those that *may* end up being enforced by the outer nodes. They may also get dropped if they turn out to be implied by the inner AST nodes. Note that this distinction is only relevant at the point where the actual AST nodes are being constructed. At other points in the AST generation algorithm, we can simply consider the combination of the two groups of constraints.

A:10 Grosser et al.

The mapping from loop iterators to schedule dimensions is needed because unlike other AST generators, ours exploits the fact that a schedule only specifies a *relative* execution order. The loop iterators in the final AST may then not correspond exactly to the schedule dimensions in the input schedule due to, e.g., scaling or strip-mining by the AST generator, while these schedule dimensions may still be referenced from other parts of the schedule through options (see Section 5.6) or advanced schedule tree nodes (see Section 6).

# 4.3. Abstract Syntax Tree

The generated AST contains only syntactical information and has been designed to be easily translatable to both C and compiler IR. Each node of the AST is of one of four types, an *if-node*, a *for-node*, a *block-node* or a *user-node*. An if-node has an AST expression as condition, a then-node and optionally an else-node. A for-node has initialization, condition, and increment expressions, and a *body-node*. A block-node represents a compound statement and maintains a list of nodes. Finally, the statement expressed by a user-node is represented as an AST expression.

An AST expression is itself a tree with operators in the internal nodes and integer constants or identifiers as the leaves. The set of operators contains the standard operators found in C-like programming languages, but also higher level operators such as min and max. Boolean logical operators and the conditional operator (cond? a: b) are available in two forms, one using short-circuit evaluation and one using eager evaluation. We found in our work on low-level compilers [Grosser et al. 2012] that eagerly evaluating operands, instead of using C's short-circuit evaluation, is often beneficial as it reduces control overhead and simplifies the hoisting of loop invariant subexpressions.

The integer division operator also comes in different forms, one of them corresponding to the mathematical operation  $\lfloor a/b \rfloor$ . Unfortunately, this operation cannot be translated directly into a / b in C because the /-operator in C rounds toward zero ([ISO 1999, 6.5.5]) rather than toward negative infinity. A correct translation to C involves a condition on the sign of a, which can bring significant extra costs on some architectures such as GPU devices. We therefore also have a form of the integer division where the result is known to be an integer (such that rounding becomes irrelevant) and one where the dividend is known to be non-negative. The user can specify a preference for these latter forms in which case the AST expression generator will look for opportunities to use them (see Section 5.10). Similarly, the remainder operator comes in two special forms, one where the dividend is known to be non-negative and one where the result of the operations is only compared against zero. In these special cases, the remainder operator can be translated into the %-operator in C.

### 4.4. Annotated AST

The AST nodes are created after having visited all the children in the depth-first traversal of the schedule. The AST generator may however decide to not encode some of the conditions that need to be satisfied by the symbolic constants in the generated AST nodes such that these conditions may be hoisted up to higher levels. An *annotated AST* keeps track of both the (purely syntactical) AST itself and such extra pieces of polyhedral information. Besides the conditions described above that still need to be enforced by the AST at higher levels, the annotated AST also keeps track of the conditions that *have* been enforced already. This latter set of conditions can then be used to simplify or even eliminate some of the pending conditions in the stock at higher levels.

#### 5. AST GENERATION

This section describes the core AST generation algorithm. In Section 6.3, we will see that this algorithm is applied for each band node in the schedule tree. Our core algorithm is derived from the "Quilleré et al." algorithm [Bastoul 2004; Quilleré et al. 2000], with several significant changes such as isolation, unrolling, if-hoisting, the detection of components, shifted strides, and the optimized generation of AST expressions.

#### 5.1. Overview

*Example* 5.1. Before we delve into the details of the AST generation algorithm, let us first apply it to the simple example of Section 3, where our algorithm essentially coincides with the standard "Quilleré et al." algorithm. In particular, let us consider the schedule of (2). The initial executed relation, including the domain constraints of (1), is

$$\{(i,0,0) \to \mathrm{S1}(i) : 0 \le i < n; (i,1,j) \to \mathrm{S2}(i,j) : 0 \le j < i < n; (i,2,0) \to \mathrm{S3}(i) : 0 \le i < n\}.$$

(5)

The outermost loop of the generated AST is derived from the first dimension in the domain of this relation. A projection onto this first dimension yields

$$\{(i): 0 \le i < n\}.$$

(6)

In this simple case, we find a set described by a single disjunct and the lower and upper bound of the generated outermost for loop can be trivially read off from the constraints. If the projection were described by multiple disjuncts, then we would have to combine them or break them up into disjoint pieces first. Moving on to the second dimension, we would, in principle, find the following projection onto the outer two dimensions

$$\{(i,t): 0 \le i < n \land 0 \le t \le 2\}.$$

(7)

and generate a loop iterating over the values 0 to 2. However, we can see that no instance of S1 is ordered after any instance of S2 or S3 at this level and similarly for S2 with respect to S3. We therefore have a trivial case of our component detection and continue generating an AST for S1, S2 and S3 separately in that order. Note that other AST generators handle this special case through different mechanisms. In each of the components, the second dimension has a fixed value, so no loop needs to be generated. The same is true for the third dimension in the components containing S1 and S3, respectively. The component containing S2 does result in an extra loop, which is handled in the same way as the outer loop.

Algorithm 3 forms the core of the AST generation and creates a (possibly degenerate) for AST node for a given schedule dimension after generating AST nodes for the next schedule dimensions through a call to Algorithm 1. The process of creating such a for-node is detailed in Section 5.3. The input is a single-disjunct set corresponding to the current dimension in the schedule domain. The actual schedule domain at this dimension may however consist of several disjuncts. Algorithm 2 takes care of breaking up (or overapproximating) the schedule domain into disjoint single-disjunct pieces and calling Algorithm 3 on each of them. The different ways of breaking up the schedule domain are explained in Section 5.4 and Section 5.5. In Example 5.1, the relevant schedule domains all consist of a single disjunct such that no additional processing is required.

Finally, Algorithm 1 is the main driver that is called (recursively) for each dimension in the schedule space (i.e., the domain of the executed relation). It calls Algorithm 2 after detecting some special cases. In particular, as long as the inner level has not been

A:12 Grosser et al.

#### **ALGORITHM 1:** Generate Next Schedule Dimension ("next")

```

Input: — stock

executed relation

if at inner level then

return terminate(stock, executed)

end

list := ()

foreach sorted component do

/* detect shifted strides and record mapping in f, see Section 5.8

*/

(stock, executed, f) := detect shifts(stock, executed)

/* project domain of executed on outer level dimension, see Section 5.2

*/

domain := project(executed, level)

if has isolation domain then

(before, domain, after, other) = split on isolation(domain)

list' := base(stock, executed, before, false)

list' += base(stock, executed, domain, true)

list' += base(stock, executed, after, false)

list' += base(stock, executed, other, false)

list' := base(stock, executed, domain, false)

end

/* undo schedule modification in case of shifted strides, see Section 5.8

list += transform(list', f)

end

return list

```

reached, the algorithm first looks for components as described in Section 5.7. In Example 5.1, three components are detected at the second schedule dimension. In each component, the algorithm checks for shifted strides as explained in Section 5.8, possibly modifying the executed relation if any shifted strides were detected. The domain of the executed relation is then projected onto the outer level dimensions as explained in Section 5.2. In Example 5.1, this projection yields the set  $\{(i): 0 \le i < n\}$  (6) at the outer schedule dimension. Finally, if the user specified a piece of the schedule space that needs to be isolated (see Section 5.6), then the algorithm splits the schedule domain into four parts, the part that comes before the isolated part, the isolated part itself, the part that comes after and the part that is incomparable to the isolated part.

When the inner level has been reached, the schedule makes no further distinction between the statement instances in the range of the current executed relation. We therefore generate an AST for each statement separately. Usually, the executed relation will only associate a single statement instance to a given schedule point and we simply create and return a user node. Otherwise, the AST still needs to iterate over the different instances and it can do so in any order. We therefore extend the domain of the executed relation with a copy of the range and continue processing the new dimensions in the domain of the executed relation until the inner level is reached again, in which case the executed relation is guaranteed to have only a single statement instance associated to a given schedule point.

#### 5.2. Local Schedule Domain Constraints

The lower and upper bounds of a for loop generated at a given level are derived from the constraints in the domain of the executed relation that involve the current schedule dimension. These constraints may also involve other schedule dimensions, both those corresponding to outer for loops and those corresponding to inner for loops. Since the

### **ALGORITHM 2:** Generate Component ("base")

```

Input: — stock

executed relation

— domain: part of schedule domain at current level for which AST should be generated

— isolated: boolean indicating whether domain refers to isolated part

type := generation type(level, isolated)

if type = unroll then

(bound, n) := find lower bound(domain)

list := ()

for 0 \le i \le n do

/* select domain elements at offset i from the lower bound

*/

domain' := slice(domain, bound, i)

domain' := shared constraints(domain')

list += (create(stock, executed, domain'))

end

return list

end

if type = separate then

domain list := separate(domain, executed)

else if type = atomic then

domain list := (shared constraints(domain))

else

domain list := make disjoint(domain)

end

list := 0

foreach domain in sorted domain list do

list += (create(stock, executed, domain))

return list

```

# **ALGORITHM 3:** Create for-node ("create")

lower and upper bounds of a for loop can only refer to iterators of outer loops and (obviously) not to those of inner loops, we first need to project the domain of the executed relation onto its first level dimensions. This operation may introduce additional existentially quantified variables, which cannot be encoded directly in AST expressions. We therefore need to remove them in some way.

One way of removing the existentially quantified variables is to perform quantifier elimination. This process preserves the meaning of the set and therefore ensures that only those values of the current schedule dimension that have any associated state-

A:14 Grosser et al.

ment instances will be executed. On the other hand, quantifier elimination may break up the schedule domain into several pieces. In particular, isl performs quantifier elimination by applying parametric integer programming [Feautrier 1988] to compute explicit, quasi-affine representations of the quantified variables. In general, this may split the domain into several parts, each with its own quasi-affine expressions. Other quantifier elimination algorithms lead to similar decompositions of the schedule domain

Another way of removing the existentially quantified variables is to perform Fourier-Motzkin elimination on them. This may result in an overapproximation of the schedule domain, but it is guaranteed not to break up the schedule domain into several disjuncts. In our AST generator, we take this second option in order to avoid the code size expansion resulting from the first option. That is, we apply Fourier-Motzkin elimination to remove all existentially quantified variables for which we do not have an explicit representation yet. Note that we will only consider the constraints of the possible overapproximation as having been generated at this level, such that any constraint on the actual schedule domain that is not satisfied by this overapproximation will end up getting enforced at a deeper level.

*Example* 5.2. As an example of a case where these two approaches produce different results, consider the following projection of some schedule domain onto the outermost schedule dimension,

$$\{(t): (\exists \alpha: \alpha \ge -1 + t \land 2\alpha \ge 1 + t \land \alpha \le t \land 4\alpha \le N + 2t)\},\tag{8}$$

where N is a symbolic constant. Applying quantifier elimination to the set description in (8) results in

$$\{(t): (t \ge 3 \land 2t \le 4 + N) \lor (t \le 2 \land t \ge 1 \land 2t \le N)\}.$$

(9)

Note that this is the same set, but that it is described in a different way, without existentially quantified variables. Also note that the description now consists of two disjuncts. Applying Fourier-Motzkin elimination on the  $\alpha$  variable in (8) on the other hand results in

$$\{(t): 2t \le 4 + N \land N \ge 2 \land t \ge 1\}.$$

(10)

This set contains an extra element that is not an element of the set in (8). In particular, it contains the extra element

$$\{(2): 2 \le N \le 3\} \tag{11}$$

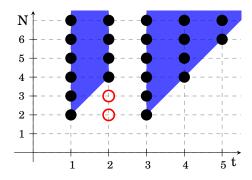

Figure 4 shows the elements of the set in (8) in black for  $0 \le N \le 7$ . These are the same as those in the set description in (9) that results from quantifier elimination. The additional element (if any) introduced by Fourier-Motzkin (10) is shown in red.

Using the set in (9) would produce the code

```

for (int c0 = 1; c0 <= min(2, floord(N, 2)); c0 += 1)

// body

for (int c0 = 3; c0 <= floord(N, 2) + 2; c0 += 1)

// body</pre>

```

whereas using the set in (10) produces the code

```

for (int c0 = 1; c0 <= floord(N, 2) + 2; c0 += 1)

// body

```

As explained above, isl's quantifier elimination may replace a quantified variable by a quasi-affine expression. During the simplification of set descriptions, isl may perform a similar substitution. We therefore need to take into account that the projection

Fig. 4: Quantifier elimination (blue area) and Fourier-Motzkin (black dots + red circles) applied to (8) (black dots).

of the schedule domain, even after eliminating the existentially quantified variables using Fourier-Motzkin elimination, may involve such quasi-affine expressions. If any of these quasi-affine expressions depend on the current level, then they are also eliminated using Fourier-Motzkin elimination since a lower bound of a loop cannot depend on the value of the loop iterator. Similarly, a constraint involving such an expression cannot be used to construct an upper bound since it may fail to hold for some values of the iterator while being satisfied by higher values of the iterator. Note that this process also removes any stride information, but this information will be recovered from the executed relation as explained in Section 5.3.1.

Example 5.3. Consider an iteration domain

$$\left\{ S(i) : 3 \left\lfloor \frac{i+1}{3} \right\rfloor \le i \land i \ge 0 \land i \le 3 \right\}$$

(12)

with schedule

$$\{S(i) \to (i)\}. \tag{13}$$

The schedule domain and its projection onto the outermost (and only) level is

$$\{(i): 3\left\lfloor\frac{i+1}{3}\right\rfloor \le i \land i \ge 0 \land i \le 3\}. \tag{14}$$

The constraint  $3\lfloor (i+1)/3\rfloor \leq i$  involves a quasi-affine expression in terms of the current level and therefore cannot be used in the construction of the for loop bounds. Instead, the expression is eliminated, resulting in the schedule domain

$$\{(i): i \ge 0 \land i \le 3\}.$$

(15)

The eliminated constraint is then taken into account at the innermost level, resulting in the following code.

Note that when reaching the innermost level, we can no longer perform any approximations and we have to perform quantifier elimination on any remaining existentially quantified variables. This may then result in a disjunctive condition around the generated statement. Also note that the quantifier elimination procedure of the Omega library is different from the one used by is1, but it may also result in splitting the

A:16 Grosser et al.

domain. A detailed comparison of the two is beyond the scope of the present article. It is not clear at which point and how far CodeGen+ applies quantifier elimination, but it appears to be tailored to constraints that only involve a single existentially quantified variable.

#### 5.3. For Node Construction

5.3.1. Stride Detection. Besides the stock and the executed relation, Algorithm 3 for creating a for-node takes as extra input a convex set called "bounds" from which the bounds of the for-node will be extracted. The first step is the detection of strides, but this information is not available in bounds since it does not involve any quasi-affine expressions that depend on the current level. Instead, we use the intersection of the bounds set with the domain of the executed relation. The strides are extracted from the integer affine hull [Verdoolaege 2010] of the resulting set. This operation extracts the equality constraints satisfied by the elements of the set and preserves (most of) the stride information. Let

$$h(\mathbf{p}) + u\left(vi + sf(\boldsymbol{\alpha})\right) = 0 \tag{16}$$

be one of these equality constraints, with i the current schedule dimension,  $\mathbf p$  the symbolic constants and outer dimensions and  $\alpha$  the existentially quantified variables. Furthermore, v and s have no common factor and f and h are affine expressions such that the coefficients of f have no common factor. If v is nonzero and s is greater than one, then this equality represents a non-trivial stride constraint. Using Bézout's identity av + bs = 1, we can rewrite (16) to

$$ui = -ah(\mathbf{p}) + us\left(bi - af(\boldsymbol{\alpha})\right) \tag{17}$$

so that  $-ah(\mathbf{p})$  is a multiple of u and i is equal to  $o(\mathbf{p}) = -ah(\mathbf{p})/u$  modulo s. The offset  $o(\mathbf{p})$  and the stride s are stored in the stock. If there is more than one equality with a non-trivial stride, then the offsets and strides can be combined and the overall stride will be the least common multiple of the strides. In particular, if we have two offset/stride pairs

$$i = o_1(\mathbf{p}) + s_1 f_1(\boldsymbol{\alpha}) \tag{18}$$

$$i = o_2(\mathbf{p}) + s_2 f_2(\alpha) \tag{19}$$

then let g be the greatest common divisor of  $s_1$  and  $s_2$  and let c and d be such that  $c s_1 + d s_2 = g$  (Bézout's identity once more). Multiplying the equation in (18) by  $t_1 = d s_2/g$  and the equation in (19) by  $t_2 = c s_1/g$ , we obtain

$$i = (d s_2 + c s_1)/g i = t_1 o_1(\mathbf{p}) + t_2 o_2(\mathbf{p}) + (s_1 s_2)/g (b f_1(\alpha) + a f_2(\alpha)).$$

(20)

That is, the combined offset is  $t_1o_1(\mathbf{p}) + t_2o_2(\mathbf{p})$ , while the combined stride is  $(s_1 s_2)/g$ , the least common multiple of  $s_1$  and  $s_2$ .

Example 5.4. Consider the schedule domain

$$\{(i): \exists \alpha, \beta: 0 < i < 100 \land n - i + 6\alpha = 0 \land m - i + 10\beta = 0\},$$

(21)

with n and m symbolic constants. For the constraint  $n-i+6\alpha=0$ , we have, using the notation of (16),  $h(\mathbf{p})=n$ , u=1, v=-1, s=6 and  $f(\alpha)=\alpha$ . We may take a=-1 and b=0 to find  $o_1(\mathbf{p})=n$  with  $s_1=6$ . We similarly find  $o_2(\mathbf{p})=m$  and  $s_2=10$ . We have g=2 and may take c=2 and d=-1, resulting in a combined stride of 30 and a combined offset of -5n+6m. To see that this combined offset satisfies both stride constraints, note that the combination of the original two stride constraints implies that n-m is a multiple of two. That is, the bounds set (from which the existentially

quantified variables have been eliminated) is of the form

$$\{(i): 0 \le i \le 100 \land 2 \left| \frac{m-n}{2} \right| = m-n \}.$$

(22)

We therefore have that m - (-5n + 6m) = 5(n - m) is indeed a multiple of 10.

5.3.2. Loop Constraints. After detecting the strides, we add the constraints enforced by the for loop generated for the current schedule dimension to the stock that will be used in the construction of descendant nodes such that these constraints may be used to simplify those descendant nodes. The actual construction of the for loop corresponding to the current schedule dimension is only performed after these descendant nodes have been created. At that point we will need to make a distinction between the constraints that are enforced by the bounds of the for loop and the constraints that may need to be enforced by an extra if conditional. We therefore take this difference into account while updating the stock, even though this distinction has no influence on the descendant nodes.

In order to determine which constraints are enforced by the for loop corresponding to the current schedule dimension, we first need to know if we are even going to construct a for loop. In particular, based on the constraints in the current stock, the constraints in bounds and the stride constraints (if any), we may be able to determine that the current schedule dimension can attain only a single value. In this case, we will generate a special "degenerate" for loop which we allow the user to translate to an assignment of the initial value to the loop iterator. Note that this single value will in general be specified as a piecewise quasi-affine expression in the symbolic constants and the outer loop iterators. If it turns out that this expression consists of a single quasi-affine expression, then we do not generate any for loop at all, but instead substitute the current schedule dimension for this single quasi-affine expression in the executed relation. We refer to this case as an eliminated for loop. The reason for only performing this substitution when the single value is described by a single quasi-affine expression is that otherwise we would be introducing additional disjuncts in the executed relation. In the eliminated case, we eliminate the current schedule dimension from bounds and add the result to the pending constraints. In the other cases, we add the constraints in bounds that do not involve the current schedule dimension to the pending constraints and we add the remaining constraints in bounds as well as the stride constraint (i.e., the fact that the schedule dimension is equal to the offset plus a multiple of the stride) to the generated constraints.

# Example 5.5. Consider the schedule domain

$$\{(i): i \ge 1 \land n - 1 \le i \le n \land 4 \left\lfloor \frac{i-2}{4} \right\rfloor = i - 2\},$$

(23)

where n is a symbolic constant. The stride constraint  $4 \lfloor (i-2)/4 \rfloor = i-2$  does not appear in bounds, but it is added back for the purpose of looking for a single value. From these constraints, we can see that i attains a single value of  $4 \lfloor (n+2)/4 \rfloor - 2$  and that this value is represented as a single quasi-affine expression. Substituting this value in the schedule domain, we obtain

$$\{(): n \ge 2 \land \left\lfloor \frac{n}{4} \right\rfloor \le n - 2\}. \tag{24}$$

These constraints are then added as guards to the annotated AST at the innermost level.

A:18 Grosser et al.

Note that degenerate loops that are not also eliminated are fairly rare in practice. We only report our handling of this situation for completeness, but it may very well not be close to optimal. In most of the remaining rare cases, the loop could in fact be eliminated, but we simply fail to derive an appropriate single quasi-affine expression. In fact, these cases used to occur more frequently, but most of these have been resolved through an improved detection of single quasi-affine expressions.

After generating an annotated AST for the body of the for-node, we know which constraints on the symbolic constants and outer loop iterators are enforced by this subtree and we can (optionally) use them to simplify the pending constraints. Additionally, the pending constraints are simplified with respect to the generated constraints. The simplified pending constraints are then combined with the constraints hoisted from the annotated AST for the body (see Section 5.9) and an additional set of *implied* constraints. The implied constraints are those constraints that are implied by the generated constraints, but that may not be implied by their AST expression counterparts. In particular, these are the constraints implied by the stride constraints. In case of a degenerate loop, this also includes the constraints implied by the generated constraints. Since we are allowing the user to consider a degenerate for loop as an assignment, the fact that the upper bound is greater than or equal to the lower bound (i.e., that there even is a single iteration of the loop) is not enforced by this assignment and therefore needs to be considered separately. The combination of the simplified pending constraints, the hoisted constraints and the implied constraints will then definitely be generated either at the current level or hoisted up to a higher level. From this point on, in particular for the construction of the AST expressions for the if conditions that have not been hoisted out of the body and those for the bounds of the for loop, they may therefore be considered as generated constraints.

Example 5.6. As an example of the effect of exploiting enforced constraints, consider the iteration domain

$$\{ S(i,j) : 0 \le i < m \land 0 \le j < n \},$$

(25)

where m and n are symbolic constants, with schedule

$$\{ S(i,j) \to (i,j) \}. \tag{26}$$

Projection of the schedule domain onto the outer dimension yields

$$\{(i): 0 \le i < m \land n \ge 1\}.$$

(27)

The single pending constraint at this level is therefore  $n \geq 1$ . At the inner level, the schedule domain, simplified with respect to the stock constraints, is

$$\{(i,j): 0 \le j < n\}.$$

(28)

The for loop generated at this inner level enforces the constraint  $n \geq 1$  so it can optionally be used to simplify the pending constraint at the outer level. If we exploit this enforced constraint, we generate the code

```

for (int c0 = 0; c0 < m; c0 += 1)

for (int c1 = 0; c1 < n; c1 += 1)

S(c0, c1);

```

Otherwise, the pending constraint is turned into an if condition and we generate the code

```

if (n >= 1)

for (int c0 = 0; c0 < m; c0 += 1)

for (int c1 = 0; c1 < n; c1 += 1)

S(c0, c1);</pre>

```

*Example* 5.7. As an example of constraints implied by a stride constraint, consider the schedule

$$\{ S(t) \to (t) : \exists \alpha : 2t - n = 4\alpha \land 0 \le t \le 100 \},$$

(29)

with n a symbolic constant. Stride detection finds a stride of 2 and an offset of n/2. The stride constraint  $(n/2 - t) \mod 2 = 0$  is encoded as

$$n - 2t - 4 \left| \frac{n + 2t}{4} \right| = 0. {(30)}$$

This constraint implies that n is a multiple of 2. Since this stride constraint is added to the generated constraints, this fact may be simplified away at the deeper levels. However, it is not implied by the actually generated for loop. We therefore eliminate t from (30) and add the resulting constraints to the constraints that need to be generated at the outer level. The final code is

Note that we have exploited the fact that n is a multiple of 2 while generating the loop initialization.

5.3.3. AST Expressions. Let us now consider the construction of the initialization and the condition of the generated for loop from the lower and upper bounds on the current schedule dimension. Since the bounds set may be an overapproximation of the schedule domain, it may in rare cases not involve lower and/or upper bounds. If they are missing, then we derive a single piecewise quasi-affine bound from the domain set using parametric integer programming [Feautrier 1988]. If this set does not have a lower bound, then an error is reported. If it has no upper bound, then an infinite for-node is generated. In the standard case where there is one or more lower bound constraint  $h(\mathbf{p}) + vi \geq 0$  with v > 0, each of the constraints is converted to a lower bound  $\ell(\mathbf{p}) = \lceil -h(\mathbf{p})/v \rceil$  and the lower bound on the for-node is set to the maximum (as an AST expression) of these lower bounds. If the loop is strided, however, then we need to make sure that this lower bound has the right value modulo the stride. We therefore first replace each of the lower bounds  $\ell(\mathbf{p})$  by  $o(\mathbf{p}) + s \lceil (l(\mathbf{p}) - o(\mathbf{p}))/s \rceil$ .

Example 5.8. Consider the iteration domain

$$\{ S1(i) : 0 \le i \le M; S2() \},$$

(31)

where M is a symbolic constant, with schedule

$$\{ S1(i) \to (i,0); S2() \to (0,1) \}.$$

(32)

Assume that at the outer level, we want to generate a single loop for both statements, as explained in Section 5.4, with bounds set  $\{(i):i\geq 0\}$ . This bounds set does not have any upper bound on the current schedule dimension so we consider the schedule domain

$$\{(0);(i):0\leq i\leq M\}\tag{33}$$

instead. From this set, we can derive the upper bound

$$\begin{cases} 0 & \text{if } M \le 0 \\ M - 1 & \text{otherwise.} \end{cases}$$

(34)

The generated code is as follows.

A:20 Grosser et al.

```

for (int c0 = 0; c0 <= (M <= 0 ? 0 : M); c0 += 1) {

if (M >= c0)

S1(c0);

if (c0 == 0)

S2(0);

}

```

*Example* 5.9. Continued from Example 5.4. The bounds set in (22) has only a single lower bound on the current schedule dimension,  $i \ge 0$ . The default for loop initialization would therefore be  $\max\{\lceil -0/1\rceil\} = 0$ . This value may however not satisfy the stride constraint, depending on the values of m and n. It is therefore replaced by

$$-5n + 6m + 30 \left\lceil \frac{5n - 6m}{30} \right\rceil = -5n + 6m + 30 \left\lfloor \frac{5n - 6m + 29}{30} \right\rfloor.$$

(35)

Depending on a user setting, the for-node upper bound condition is constructed either as a single comparison of the loop iterator to a minimum of upper bounds, derived analogously to the lower bounds, or as a conjunction of comparisons, each derived directly from an upper bound constraint. The single upper bound is expected by the OpenMP support of some compilers while the conjunction is more efficient on FPGAs [Zuo et al. 2013]. Finally, the independent constraints are added to the annotated AST holding the for-node.

Example 5.10. Consider upper bounds of the form

$$M \ge c_3 + 1 \land c_1 \ge 3c_3 + 8 \tag{36}$$

If the user has selected the generation of a single upper bound, then an upper bound condition of the form c3 < min((c1 + 1) / 3 - 2), M) is generated, while in the other case, an upper bound condition of the form M >= c3 + 1 && c1 >= 3 \* c3 + 8 is generated.

# 5.4. Separation

The schedule domain(s) computed in Algorithm 1 may be arbitrary Presburger sets, which in isl are represented in disjunctive normal form. The creation of a for-node in Algorithm 3, however, takes a single-disjunct set as input. The responsibility of the intermediate Algorithm 2 is then to replace the schedule domain by an ordered sequence of disjoint single-disjunct domains. There are essentially two ways to obtain such single-disjunct domains, either the entire domain is approximated by a single-disjunct domain or the domain is broken up into single-disjunct parts. The first option may require the introduction of additional guards in the descendants of the currently constructed for-node, possibly leading to run-time overhead. The second option can lead to code duplication since different instances of the same domain may end up in different single-disjunct schedule domain parts.

For each schedule dimension, the user can specify which of these options to take. Alternatively, the user may also specify that the schedule dimension should be unrolled (Section 5.5) or she may leave the option unspecified, in which case the schedule domain is broken up into a list of single-disjunct domains in a pragmatic way.

Let us consider the two main options in some more detail. If the "separate" option is specified, then the schedule domains are computed for each statement separately. Each of these schedule domains is broken up into disjoint single-disjunct sets and a common refinement is computed. This is the standard separation of the "Quilleré et al." algorithm [Quilleré et al. 2000; Bastoul 2004]. In the "atomic" case, the *shared constraints* are used. That is, the constraints of the disjuncts are considered in turn and only those are kept that are satisfied by the entire schedule domain. This process

may in some cases result in the absence of a lower and/or upper bound, a case we discussed in Section 5.3.

*Example* 5.11. Continued from Example 5.8. Consider the schedule domain at the outer dimension in (33), repeated here

$$\{(0);(i):0\leq i\leq M\}.$$

(37)

In case of separation, we consider the schedule domains for each statement separately, i.e.,  $\{(0)\}$  and  $\{(i): 0 \le i \le M\}$ , and apply the standard separation algorithm, breaking up these sets into disjoint single-disjunct sets, resulting in

$$\{(0): M < -1\}, \{(0): M > 0\} \text{ and } \{(i): 1 < i < M\}.$$

(38)

The generated code is as follows.

```

if (M <= -1) {

S2(0);

} else {

S1(0);

S2(0);

for (int c0 = 1; c0 <= M; c0 += 1)

S1(c0);

}</pre>

```

In the atomic case, we consider the constraints shared by the disjuncts in (33). In this example, there is only one such constraint, i.e.,  $i \ge 0$ . Note that the equality constraint i = 0 in the first disjunct is equivalent to  $i \ge 0 \land i \le 0$ . The generated code for this case is shown in Example 5.8.

### 5.5. Unrolling

Unrolling in the AST generation works by taking slices of the schedule domain for successive values of the current schedule dimension and by calling "create" for each of these slices. By construction, the schedule dimension has a fixed quasi-affine value in each of the slices and no actual for-node will be created. Two factors play an important role in unrolling: stride detection and the selection of the most appropriate lower bound. Stride detection is performed as explained in Section 5.3.1. If any stride is found, then it is substituted ( $i = o(\mathbf{p}) + si'$ ) in the schedule domain for the purpose of selecting a lower bound.

*Example* 5.12. If the schedule domain is of the form

$$\{i: 0 \le i \le 1024 \land i \bmod 256 = 0\},$$

(39)

then it is replaced by  $\{i': 0 \le i' < 4\}$ .

The lower bound identification requires a single disjunct so we consider once more the shared constraints of the schedule domain, although in this case we also allow constant shifts of the constraints. For each lower bound constraint  $h(\mathbf{p}) + vi \geq 0$  with v > 0, we compute the maximum value of  $i+1-\lceil -h(\mathbf{p})/v \rceil$  over the schedule domain. If the maximum exists and has value n then we know we can cover the schedule domain with at most n slices of the form  $i = \lceil -h(\mathbf{p})/v \rceil + t$  with  $0 \leq t < n$ . We take the lower bound with the smallest such n. If no suitable lower bound can be found, then we report an error.

Example 5.13. For the schedule domain

$$\{i: 0 \le i < 1000 \land N \le i < N+4\},$$

(40)

A:22 Grosser et al.

we would prefer the lower bound N (with 4 slices) over the lower bound 0 (with 1000 slices).

#### 5.6. Isolation

Isolation in Algorithm 1 is controlled by an option specified by the user. If set, the option describes a part of the schedule domain that should be isolated from the other parts of the schedule domain. The typical use cases are the isolation of full tiles from partial tiles or the isolation of a vectorizable loop from its prologue and epilogue. The atomic/separate/unroll option can be specified separately for the isolated part and the rest of the schedule domain. For any given level, the isolated domain is first projected onto the first level dimensions as in Section 5.2. In particular, the inner dimensions are projected out and all existentially quantified variables and all quasi-affine expressions involving the current dimension are eliminated. We subsequently replace the set by its shared constraints to ensure that the center part is contiguous. An intersection with the current schedule domain yields the center part of the isolation. The "before" part is obtained by first constructing a set of iterations that are executed before some iteration in the center part and then subtracting that center part. Similarly, the "after" part is obtained by first constructing a set of iterations that are executed after some iteration in the center part and then subtracting both the center part and the "before" part. The "other" part is obtained by subtracting the before, center, and after parts from the current schedule domain and consists of those iterations that are incomparable to the center part. If any atomic/separate/unroll option is specified for the rest of the schedule domain, then it is applied to the before, after, and other part separately.

Example 5.14. Assume we have an iteration domain

$$\{ S(i) : m \le i < n \},$$

(41)

where m and n are symbolic constants, with initial schedule

$$\{ \mathbf{S}(i) \to (i) \} \tag{42}$$

and that we want to strip-mine the loop by 4, a factor that has been derived to allow the backend compiler to vectorize the inner loop, e.g., by considering the data types used in the computation or the target vector instruction set. We first modify the schedule to

$$\{S(i) \to \left(4 \left| \frac{i}{4} \right|, i\right)\} \tag{43}$$

and then we want to single out those iterations that result in an inner loop of exactly four iterations. In particular, we need to make sure that the first schedule dimension  $t=4\lfloor i/4\rfloor$  belongs to the schedule domain of the second dimension and that so does t+3. We therefore isolate the values of the first schedule dimension that satisfy

$$\{(t): m \le t \land t + 3 < n\}.$$

(44)

Projecting out inner dimensions and replacing the set by its shared constraints does not modify the isolated set. The before part is

$$\{(t): n \ge 4 + m \land t \le m - 1\},$$

(45)

the after part is

$$\{(t): n > 4 + m \land t > n - 3\}$$

(46)

and the other part is

$$\{(t): m-3 \le t \le n-1 \land n \le m+3 \land n \ge m+1\}.$$

(47)

The generated code (shown below) consists of a single loop performing the prologue computation, two—now easily vectorizable—loops that enumerate the center part, and one loop that forms the epilogue computation. There is also an additional loop nest for the other part, which is executed in case the values of n and m yield an empty center part. In certain cases, it is possible to avoid the generation of dedicated code for the other part by instead enumerating the relevant iterations as part of the before and after parts. We currently do not perform such an optimization.

```

{

if (n >= m + 4)

for (int c1 = m; c1 <= 4 * floord(m - 1, 4) + 3; c1 += 1)

S(c1);

for (int c0 = 4 * floord(m - 1, 4) + 4; c0 < n - 3; c0 += 4)

for (int c1 = c0; c1 <= c0 + 3; c1 += 1)

S(c1);

if (n >= m + 4 && 4 * floord(n - 1, 4) + 3 >= n) {

for (int c1 = 4 * floord(n - 1, 4); c1 < n; c1 += 1)

S(c1);

} else if (m + 3 >= n)

for (int c0 = 4 * floord(m, 4); c0 < n; c0 += 4)

for (int c1 = max(m, c0); c1 <= min(n - 1, c0 + 3); c1 += 1)

S(c1);

}</pre>

```

*Example* 5.15. We also briefly illustrate isolation on multiple dimensions. Assume we have an iteration domain

$$\{ S(i,j) : 0 \le i < n \land 0 \le j < m \},$$

(48)

where n and m are symbolic constants, with initial schedule

$$\{ S(i,j) \to (i,j) \}, \tag{49}$$

which we want to tile to improve register reuse. To implement such a register tiling (e.g., by  $3 \times 4$ ), we modify the schedule to

$$\{ S(i,j) \to (3 \left\lfloor \frac{i}{3} \right\rfloor, 4 \left\lfloor \frac{j}{4} \right\rfloor, i, j) \}.$$

(50)

We then want to single out those iterations that result in two inner loops with together exactly 12 iterations, aiming to generate loops that can be fully unrolled without introducing conditions that hinder the use of registers. To implement this, we isolate the tiles of the schedule dimensions  $t_3=i, t_4=j$  that lie entirely in the schedule domain  $\{(t_3,t_4): 0 \leq t_3 < n \land 0 \leq t_4 < m\}$ . In particular, the tile at  $t_1=3 \lfloor t_3/3 \rfloor$ ,  $t_2=4 \lfloor t_4/4 \rfloor$  belongs to the schedule domain if both  $(t_1,t_2)$  and  $(t_1+2,t_2+3)$  satisfy these constraints. We therefore isolate the values of the first two schedule dimensions that satisfy

$$\{ (t_1, t_2) : 0 \le t_1 \land t_1 + 2 < n \land 0 \le t_2 \land t_2 + 3 < m \}.$$

(51)

The generated AST for this example (shown below) consists of two loop nests at the outer level. The first iterates over tiles that are complete in the first dimension, while the second iterates over tiles that are partial in this dimension. At the second level inside the first loop nest, the tiles are further split into those that are complete and those that are partial in the second dimension. Note that when generating the AST below, we have specified in the input (through a context node, see Section 6) that n and m are known to not be very small ( $n > 2 \land m > 3$ ). Without this extra piece of information, the AST generator would generate additional code for such small values of n and m, corresponding to the "other" parts of the isolation.

A:24 Grosser et al.

```

{

for (int c0 = 0; c0 < n - 2; c0 += 3) {

for (int c1 = 0; c1 < m - 3; c1 += 4)

for (int c2 = c0; c2 <= c0 + 2; c2 += 1)

for (int c3 = c1; c3 <= c1 + 3; c3 += 1)

S(c2, c3);

if ((m - 1) % 4 <= 2)

for (int c2 = c0; c2 <= c0 + 2; c2 += 1)

for (int c3 = -((m - 1) % 4) + m - 1; c3 < m; c3 += 1)

S(c2, c3);

}

if ((n - 1) % 3 <= 1)

for (int c1 = 0; c1 < m; c1 += 4)

for (int c2 = -((n - 1) % 3) + n - 1; c2 < n; c2 += 1)

for (int c3 = c1; c3 <= min(m - 1, c1 + 3); c3 += 1)

S(c2, c3);

}</pre>

```

### 5.7. Components