Radboud University Nijmegen

# Implementation Aspects of Security and Privacy in Embedded Design

Josep Balasch

March 2014

Radboud University Nijmegen

# Implementation Aspects of Security and Privacy in Embedded Design

Josep Balasch

March 2014

Copyright © Josep Balasch, 2014

D/2014/7515/39 ISBN 978-94-6018-815-2

### Implementation Aspects of Security and Privacy in Embedded Design

Proefschrift

ter verkrijging van de graad van doctor aan de Radboud Universiteit Nijmegen op gezag van de rector magnificus prof. dr. S.C.J.J. Kortmann volgens besluit van het college van decanen en ter verkrijging van de graad van doctor in de ingenieurswetenschappen aan de KU Leuven op gezag van rector prof. dr. R. Torfs

in het openbaar te verdedigen op dinsdag 11 maart 2014 om 10:30 uur precies

$\operatorname{door}$

Josep M. Balasch Masoliver

geboren op 3 juli 1982 te Vic, Spanje.

#### **Promotoren:**

$\begin{array}{c} {\rm Prof. \ dr. \ Ingrid \ Verbauwhede} \\ {\it KU \ Leuven, \ Belgium} \end{array}$

Prof. dr. Bart P.F. Jacobs

#### Manuscriptcommissie:

Prof. dr. Lejla Batina

Prof. dr. Claudia Diaz KU Leuven, Belgium

Dr. Benedikt Gierlichs KU Leuven, Belgium

Prof. dr. Rudy Lauwereins KU Leuven, Belgium

Prof. dr. François-Xavier Standaert Université Catholique de Louvain, Belgium

Prof. dr. Eric R. Verheul

Prof. dr. Yves Willems KU Leuven, Belgium

### Implementation Aspects of Security and Privacy in Embedded Design

DOCTORAL THESIS

to obtain the degree of doctor from Radboud University Nijmegen on the authority of the Rector Magnificus, prof. dr. S.C.J.J. Kortmann, according to the decision of the Council of Deans

> and to obtain the degree of doctor of engineering science from KU Leuven on the authority of rector prof. dr. R. Torfs

to be defended in public on Tuesday, 11 March 2014 at 10:30 hours

by

Josep M. Balasch Masoliver

born in Vic, Spain on 3 July 1982.

#### Supervisors:

Prof. dr. Ingrid Verbauwhede KU Leuven, Belgium

Prof. dr. Bart P.F. Jacobs

#### **Doctoral Thesis Committee:**

Prof. dr. Lejla Batina

Prof. dr. Claudia Diaz KU Leuven, Belgium

Dr. Benedikt Gierlichs KU Leuven, Belgium

Prof. dr. Rudy Lauwereins KU Leuven, Belgium

Prof. dr. François-Xavier Standaert Université Catholique de Louvain, Belgium

Prof. dr. Eric R. Verheul

Prof. dr. Yves Willems KU Leuven, Belgium To the memory of my father

## Acknowledgments

After seemingly endless months of typing and correcting, the time has come to write the last part of this thesis. I will take this opportunity to thank several people who, in one way or another, have greatly influenced the journey leading to this dissertation.

First of all, great appreciation goes to my supervisors Prof. Ingrid Verbauwhede and Prof. Bart Jacobs for giving me the chance to pursue a joint PhD degree. I am grateful for the freedom I have been given during my research, and the guidance and advice provided when needed.

I would like to extend my gratitude to Prof. Rudy Lauwereins, Prof. Lejla Batina and Prof. Claudia Diaz, my assessors during the PhD study, for many valuable advice along the way. My appreciation also to Prof. François-Xavier Standaert, Dr. Benedikt Gierlichs, Prof. Yves Willems and Prof. Eric Verheul for kindly accepting to be members of my Doctoral Examination Committee.

It has been (and still is) a pleasure to be part of a research group like COSIC. I will not attempt to do a one-by-one enumeration of colleagues and friends to whom I am indebted. Instead, I want to thank my multiple office and lab mates, for making working hours more enjoyable; the one o'clock Alma crew, for sharing lunches and stories; the occasional Friday beer gathering, for providing a fun space outside work; and the COSIC futsal team, for that ever present reminder that not everything is about winning. A particular thanks goes to Péla and Elsy for the countless times they have helped me with bureaucratic and financial issues.

Throughout my PhD I had the luck to work together with excellent researchers and to learn a lot from them. I am indebted to many co-authors with whom I share the credit of my works. I am particularly grateful to Carmela, Benedikt, Alfredo and Claudia not only for the close collaboration we had during our days in COSIC, but also for guiding me during the always difficult first stages of research life. My appreciation goes also to Prof. Bart Preneel for allowing me to join the COSIC research group in the first place, before the start of my PhD.

Last but definitely not least, I would like to thank my family, including inlaws, for their encouragement and support during my stay abroad. Also to my childhood friends back in Avinyó, for reminding me that no matter the distance, home will always be home. And finally to Sarah, for constantly being there in good and in bad times and for her unconditional support along the way.

To all of you, moltissimes gràcies!

Josep M. Balasch Masoliver March 2014

### Abstract

Embedded devices are nowadays largely represented across the compute continuum. From mobile phones to smart cards and RFID tags, digital devices are becoming increasingly ubiquitous, mobile and integrated with their environment. This gradual shift towards pervasive computing envisions many benefits in sectors as diverse as financial, entertainment, health care, information access, or automotive. Along with these possibilities however, there are also inherent risks to be addressed. It is in this context that this dissertation is situated. It provides contributions to the security of embedded devices and the privacy of the humans interacting with them.

The first part of the thesis is devoted to physical security. Many existing and future applications have built-in security capabilities which rely on keeping cryptographic keys secret. Typical examples include payment tokens, digital identity documents, or access control cards. As these devices operate in hostile environments, they need protection against physical attacks. Among these, side channel attacks and fault attacks represent two of the major threats in the security of embedded devices.

Our contributions in this area encompass three different but related aspects. First, we provide an in-depth analysis of vulnerabilities that lead to physical attacks. In particular, we characterize the effects of fault injections based on setup-time violations on a low-end microcontroller. Second, we show how physical attacks are still a prominent threat for secure devices by successfully attacking a widely used family of secure memories. And third, we devise and thoroughly evaluate a high-level mitigation against side channel attacks. More specifically, we employ the inner product construction to design a masking-based countermeasure implementable at any order.

The second part of the thesis deals with privacy aspects. Systems such as location-based services, health-care monitoring, or smart homes rely on the collection and processing of fine-grained information about users. Hazards derived from mining, sharing or misusing collected data are numerous, e.g. from discrimination, persecution or reputation damage for end users to large scale surveillance of individuals. Privacy-preserving methods to minimize the processing and/or disclosure of personal data is paramount for the acceptance of these systems.

We select Electronic Toll Pricing (ETP) as case study, a major representative of location-based services. This envisioned system allows governments to levy taxes on the use of public roads by deploying in-vehicle On-Board Units (OBUs). Our main contribution is the design, analysis and implementation of PrETP, a privacy-preserving ETP solution. The privacy guarantees of our system are achieved by letting OBUs compute their road fees locally. At the same time, we provide means for service providers to ensure that OBUs carry out correct computations.

## Samenvatting

Van mobiele telefoons tot smartcards en RFID-tags, digitale apparaten zijn alomtegenwoordig, mobiel en geïntegreerd met hun omgeving. Deze geleidelijke verschuiving in de richting van pervasive computing leidt tot vele voordelen in diverse sectoren zoals de financiële, entertainment, gezondheidszorg, informatietoegang, of de automobielsector. Naast deze mogelijkheden zijn er echter ook inherente risico's die gemitigeerd dienen te worden. Deze risico's en hoe ze aangepakt kunnen worden vormen het onderwerp van dit proefschrift. Het behandelt de veiligheid van ingebedde apparaten en de privacy van de gebruikers van zulke apparaten.

Het eerste deel van deze thesis handelt over fysieke beveiliging. Vele bestaande en toekomstige toepassingen hebben ingebouwde beveiligingscapaciteiten die steunen op de geheimhouding van cryptografische sleutels. Typische voorbeelden hiervan zijn betalingstokens, digitale identiteitsdocumenten of kaarten voor toegangscontrole. Aangezien deze apparaten werken in een vijandige omgeving, hebben ze bescherming nodig tegen fysieke aanvallen. Nevenkanaalaanvallen en foutaanvallen vormen de twee grootste bedreigingen in de beveiliging van ingebedde apparaten.

De bijdragen in dit proefschrift omvatten drie verschillende, maar verwante, aspecten. Ten eerste analyseren we de kwetsbaarheden die leiden tot fysieke aanvallen. In het bijzonder karakteriseren we de effecten van foutinjecties gedurende de setup van een low-end microcontroller. Ten tweede tonen we aan hoe fysieke aanvallen nog steeds een belangrijke bedreiging vormen voor beveiligde apparaten door een succesvolle aanval uit te voeren op een veel gebruikte familie van beveiligde geheugens. Tenslotte ontwerpen en analyseren we een hoog-niveau beveiliging tegen nevenkanaalaanvallen. Meer specifiek gebruiken we een constructie gebaseerd op het inwendig product om een maskeringsgebaseerde tegenmaatregel te ontwerpen die implementeerbaar met een willekeurig aantal delen. Het tweede deel van deze thesis handelt over privacy-aspecten. Systemen zoals locatie-gebaseerde diensten, monitoring voor gezondheidszorg, of slimme huizen steunen op de verzameling en verwerking van fijnkorrelige informatie over de gebruikers. De gevaren die voortkomen uit het analyseren, delen of misbruiken van zulke gegevens zijn bijvoorbeeld discriminatie, vervolging of reputatieschade voor eindgebruikers tot het observeren van individuen op grote schaal. Privacybewarende methoden die het bewerken en/of vrijgeven van persoonlijke gegevens minimaliseren zijn van groot belang om deze systemen in praktijk te aanvaarden.

Als voorbeeld van een locatie-gebaseerde dienst beschouwen we elektronische tolheffing. Dit systeem laat overheden toe om belastingen te heffen op het gebruik van openbare wegen door middel van een ingebedde eenheid in het voertuig. Onze belangrijkste bijdrage is het ontwerp, de analyse en de implementatie van PrETP, een privacy-bewarende oplossing voor elektronische tolheffing. De garanties die ons systeem biedt op vlak van privacy worden bereikt door de ingebedde eenheden in staat te stellen om de correcte wegentol lokaal te berekenen. Tegelijkertijd zijn de dienstverleners in staat om te controleren dat de ingebedde eenheden de juiste berekeningen uitvoeren.

# Abbreviations

| AES    | Advanced Encryption Standard             |

|--------|------------------------------------------|

| ALU    | Arithmetic Logic Unit                    |

| APDU   | Application Protocol Data Unit           |

| CMOS   | Complementary Metal-Oxide-Semiconductor  |

| CFA    | Collision Fault Analysis                 |

| CPA    | Correlation Power Analysis               |

| CPU    | Central Processing Unit                  |

| CRT    | Chinese Remainder Theorem                |

| DEMA   | Differential Electromagnetic Analysis    |

| DES    | Data Encryption Standard                 |

| DFA    | Differential Fault Analysis              |

| DoM    | Difference of Means                      |

| DPA    | Differential Power Analysis              |

| DRAM   | Dynamic Random-Access Memory             |

| DRP    | Dual-Rail Precharge                      |

| DSA    | Digital Signature Algorithm              |

| ECC    | Elliptic Curve Cryptography              |

| EEPROM | Electronically Erasable Programmable ROM |

| EM     | Electromagnetic                          |

| ETP    | Electronic Toll Pricing                  |

| FIB                       | Focused Ion Beam                           |

|---------------------------|--------------------------------------------|

| $\mathbf{FF}$             | Flip-Flop                                  |

| FPGA                      | Field-Programmable Gate Array              |

| GPS                       | Global Positioning System                  |

| $\operatorname{GSM}$      | Global System for Mobile Communications    |

| HD                        | Hamming Distance                           |

| HW                        | Hamming Weight                             |

| $\mathrm{HW}/\mathrm{SW}$ | Hardware/Software                          |

| ICT                       | Information and Communication Technologies |

| IFA                       | Ineffective Fault Analysis                 |

| IO                        | Input/Output                               |

| IoT                       | Internet of Things                         |

| ITS                       | Intelligent Transport Systems              |

| MCU                       | Microcontroller Unit                       |

| MI5                       | Military Intelligence, Section 5           |

| MIA                       | Mutual Information Analysis                |

| NSA                       | National Security Agency                   |

| OBU                       | On-Board Unit                              |

| OP                        | Optimistic Payment                         |

| PAYD                      | Pay As You Drive                           |

| PETs                      | Privacy-Enhancing Technologies             |

| POI                       | Point of Interest                          |

| PUF                       | Physical Unclonable Function               |

| RAM                       | Random-Access Memory                       |

| RFID                      | Radio-Frequency Identification             |

| RISC                      | Reduced Instruction Set Computing          |

| RNG                       | Random Number Generator                    |

| ROM                       | Read-Only Memory                           |

| RSA                  | Rivest-Shamir-Adleman Algorithm  |

|----------------------|----------------------------------|

| SABL                 | Sense Amplifier Based Logic      |

| SEA                  | Safe-Error Analysis              |

| SEM                  | Scanning Electron Microscope     |

| SEMA                 | Simple Electromagnetic Analysis  |

| SHA                  | Secure Hash Algorithm            |

| SNR                  | Signal to Noise Ratio            |

| SPA                  | Simple Power Analysis            |

| $\operatorname{SPN}$ | Substitution-Permutation Network |

| SSL                  | Secure Sockets Layer             |

| $\mathrm{TC}$        | Toll Charger                     |

| TSP                  | Toll Service Provider            |

| WDDL                 | Wave Dynamic Differential Logic  |

|                      |                                  |

\_\_\_\_\_ ix

# Contents

| A  | bstrac | ct      |                                             | iii  |

|----|--------|---------|---------------------------------------------|------|

| A  | bbrevi | iations |                                             | vii  |

| C  | onten  | ts      |                                             | xi   |

| Li | st of  | Figures | 5                                           | xv   |

| Li | st of  | Tables  |                                             | xvii |

| 1  | Intro  | oductic | on                                          | 1    |

|    | 1.1    | About   | t this Thesis                               | 9    |

| 2  | An     | Insight | into Physical Vulnerabilities               | 15   |

|    | 2.1    | Side (  | Channel Attacks                             | 15   |

|    |        | 2.1.1   | An Overview of Side Channels                | 16   |

|    |        | 2.1.2   | Side Channel Leakage in Integrated Circuits | 19   |

|    |        | 2.1.3   | Exploitation of Traces                      | 24   |

|    | 2.2    | Fault   | Attacks                                     | 33   |

|    |        | 2.2.1   | Fault Analysis                              | 34   |

|    |        | 2.2.2   | Fault Injection                             | 38   |

|   |                     | 2.2.3    | Fault Attacks based on Setup Time Violations | 40 |

|---|---------------------|----------|----------------------------------------------|----|

|   | 2.3 Countermeasures |          | ermeasures                                   | 58 |

|   |                     | 2.3.1    | Against Side Channel Attacks                 | 59 |

|   |                     | 2.3.2    | Against Fault Attacks                        | 60 |

|   | 2.4                 | Conclu   | usions                                       | 61 |

| 3 | ΑN                  | lotivati | ng Example                                   | 63 |

|   | 3.1                 | Introd   | uction                                       | 64 |

|   | 3.2                 | Relate   | ed Work and Background                       | 66 |

|   | 3.3                 | Develo   | pping an Attack Path                         | 69 |

|   |                     | 3.3.1    | Experimental Setup                           | 70 |

|   |                     | 3.3.2    | Initial Investigation of Power Traces        | 71 |

|   |                     | 3.3.3    | Overcoming Authentication Attempt Counters   | 73 |

|   | 3.4                 | Power    | Analysis Attack                              | 75 |

|   | 3.5                 | Implic   | ations and Countermeasures                   | 77 |

|   | 3.6                 | Conclu   | usions                                       | 78 |

| 4 | Mas                 | sking at | Algorithm Level                              | 79 |

|   | 4.1                 | Introd   | uction                                       | 79 |

|   | 4.2                 | Maski    | ng Block Ciphers                             | 80 |

|   |                     | 4.2.1    | 1st-Order Masking                            | 81 |

|   |                     | 4.2.2    | Higher-Order Attacks                         | 82 |

|   |                     | 4.2.3    | Higher-Order Masking                         | 84 |

|   | 4.3                 | Inner    | Product (IP) Masking                         | 85 |

|   |                     | 4.3.1    | Construction of IP Masking.                  | 86 |

|   |                     | 4.3.2    | Security Evaluation                          | 91 |

|   |                     | 4.3.3    | Performance Evaluation                       | 95 |

|   | 4.4                 | A 1st-   | order Attack Against (IP) Masking            | 98 |

|    | 4.5                                   | Conclusions                                             | 99    |

|----|---------------------------------------|---------------------------------------------------------|-------|

| 5  | 5 Enabling Privacy in Embedded Design |                                                         |       |

|    | 5.1                                   | Introduction                                            | . 101 |

|    | 5.2                                   | Privacy-Preserving Systems                              | 102   |

|    | 5.3                                   | Use Case: Electronic Toll Pricing                       | 104   |

|    |                                       | 5.3.1 PrETP: Privacy-Preserving Electronic Toll Pricing | 106   |

|    | 5.4                                   | Conclusions                                             | 124   |

| 6  | Con                                   | clusions and Open Problems                              | 125   |

| Bi | Bibliography                          |                                                         |       |

| Cι | Curriculum                            |                                                         |       |

# **List of Figures**

| 1.1  | The black-box security model                                                                                      | 3  |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | The grey-box security model                                                                                       | 4  |

| 1.3  | The embedded design space                                                                                         | 7  |

| 1.4  | Centralized architecture for exemplary monitoring systems                                                         | 8  |

| 1.5  | Thesis organization and link to embedded design space                                                             | 10 |

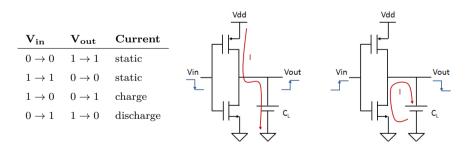

| 2.1  | CMOS inverter. Transition table (left), charge circuit (center), discharge circuit (right).                       | 19 |

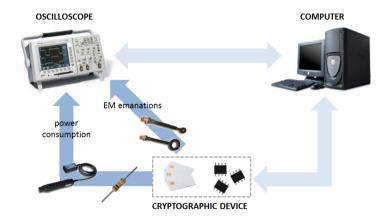

| 2.2  | Typical non-invasive side channel measurement setup. $\ldots$ .                                                   | 20 |

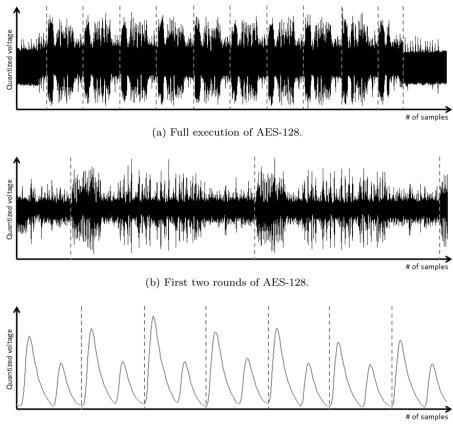

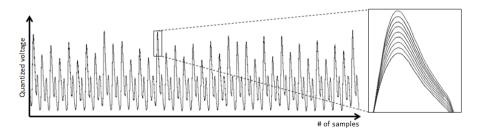

| 2.4  | Transitions on the data bus of a CMOS device                                                                      | 23 |

| 2.6  | General overview of DPA                                                                                           | 27 |

| 2.7  | Initial flow of operations in AES                                                                                 | 28 |

| 2.8  | Results of single-bit DPA attack on AES for the correct key hypothesis (left) and a wrong key hypothesis (right). | 30 |

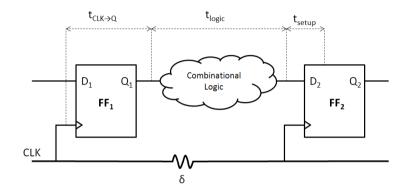

| 2.9  | Timing Constraints in Synchronous Logic                                                                           | 41 |

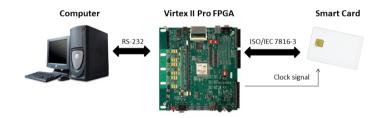

| 2.10 | Experimental Setup                                                                                                | 43 |

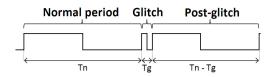

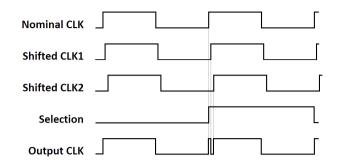

| 2.11 | Injection of a glitch in the clock signal $\ldots \ldots \ldots \ldots \ldots$                                    | 44 |

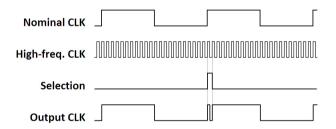

| 2.12 | Glitch generation using high-frequency signal                                                                     | 44 |

| 2.13 | Glitch generation using phase-shifted signals                                                                     | 45 |

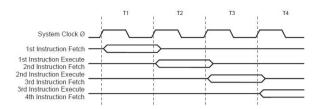

| 2.14 | Pipeline in AVR controllers (source: ATMega163 datasheet).                                                        | 46 |

| 2.15 | Code example for NOP (I)                                                                                             | 47  |

|------|----------------------------------------------------------------------------------------------------------------------|-----|

| 2.16 | Code example for NOP (II)                                                                                            | 48  |

| 2.17 | Code example for NOP (III)                                                                                           | 48  |

| 2.18 | Code example for NOP (IV)                                                                                            | 49  |

| 2.19 | Code example for BREQ.                                                                                               | 50  |

| 2.20 | Code example for single-cycle instructions                                                                           | 52  |

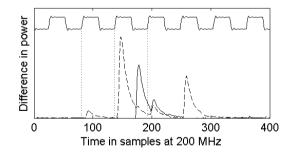

| 2.21 | Difference of means for different executions of $\mathtt{LD}$                                                        | 53  |

| 2.22 | Code example for LD                                                                                                  | 54  |

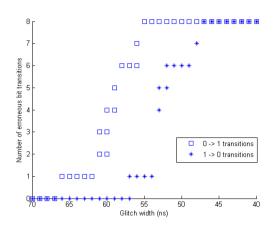

| 2.23 | Number of erroneous transitions in the data bus when decreasing the glitch width.                                    | 55  |

| 2.24 | Code example for LPM                                                                                                 | 55  |

| 3.1  | Atmel CryptoMemory Family                                                                                            | 64  |

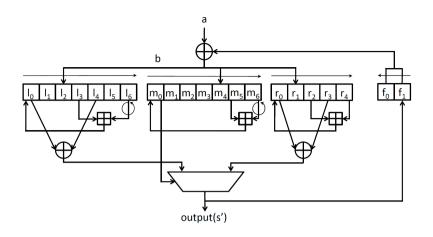

| 3.2  | Atmel cipher                                                                                                         | 67  |

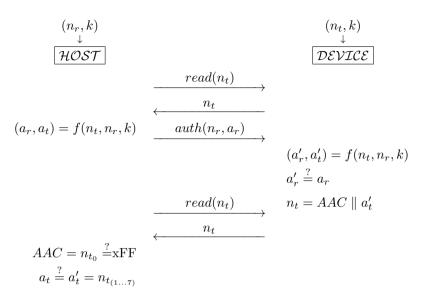

| 3.3  | CryptoMemory mutual authentication protocol                                                                          | 68  |

| 3.4  | Generation of authenticators $(a_r, a_t)$ and $K_s$ given inputs $(n_t, n_r, k)$ .                                   | 69  |

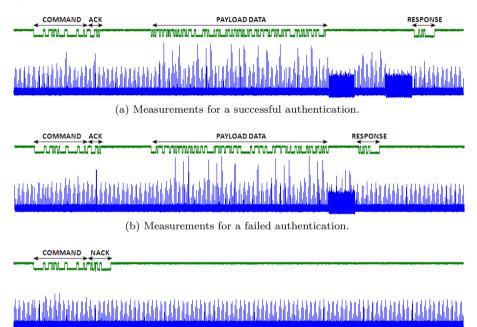

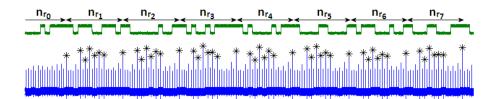

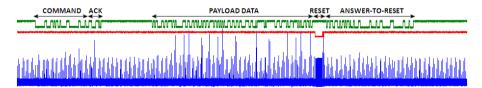

| 3.6  | I/O and power traces during the transmission of $n_r$ in authentication command. Interesting peaks are marked with * | 73  |

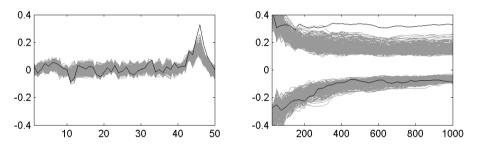

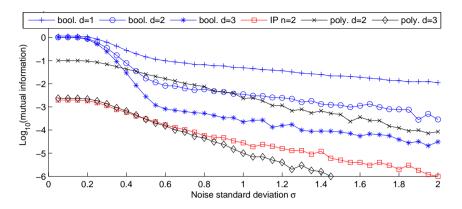

| 4.1  | Mutual information $(\log_{10})$ over increasing noise standard deviation $\sigma$ for different masking schemes.    | 94  |

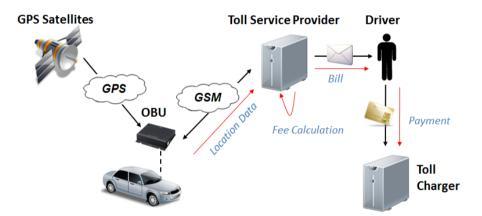

| 5.1  | Straightforward model for Electronic Toll Pricing.                                                                   | 105 |

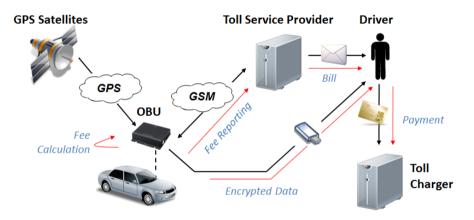

| 5.2  | PriPAYD-based architecture for Electronic Toll Pricing                                                               | 107 |

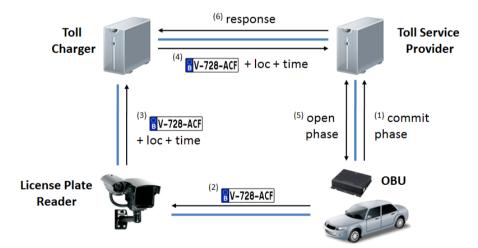

| 5.3  | PrETP enforcement spot-check model                                                                                   | 110 |

# List of Tables

| 4.1 | Complexity of IP masked operations and comparison to $d^{th}$ order<br>boolean masked operations and polynomial masked operations<br>in the literature.                                                                          | . 91  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.2 | Performance evaluation (in clock cycles) of AES round trans-<br>formations and AES encryption with IP masking scheme with<br>$n = 2. \ldots \ldots$ | 98    |

| 5.1 | Protocol between OBU and TSP during taxing phase                                                                                                                                                                                 | 115   |

| 5.2 | Length of the parameters (in bits) $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                   | 118   |

| 5.3 | Execution times (in seconds) for an hour journey of 24 km, for all possible security scenarios.                                                                                                                                  | . 121 |

| 5.4 | Timings (in seconds) for the execution of VerifyPayment() in the TSP                                                                                                                                                             | 122   |

| 5.5 | Number of OBUs supported by a single TSP                                                                                                                                                                                         | 122   |

### Chapter 1

### Introduction

Security and Privacy Aspects of Embedded Systems

With roots dating back to the ancient civilizations, *cryptography* - the art of concealing written information - is a well-studied area that has developed through the ages in an arms race with its counterpart *cryptanalysis* - the art of analyzing and breaking codes. Both disciplines, encompassed under the science of *cryptology*, have historically addressed military and diplomatic demands for secret communications. From the simple substitution ciphers of the Roman Empire to the complex rotor machines used in World War II, *cryptosystems* and *cryptodevices* have evolved through history in parallel with technology. In the last decades, the advent of Information and Communication Technologies (ICT) has triggered major advances in the field. The historical goal of ensuring secrecy over an insecure channel has been updated and extended to support secure communication protocols in the Internet era. Today, confidentiality, message integrity, and entity authentication provide security pillars that enable online applications such as e-mail, e-commerce, or e-banking.

The current paradigm of pervasive computing constitutes an ongoing shift towards a scenario in which billions of ubiquitous and inter-connected devices are being deployed worldwide. Mobile phones, radio-frequency identification tags (RFIDs), medical electronics, automotive components, home appliances, and a myriad of other *embedded devices* are representative of this trend. With physical constraints in resources, size, and computing power, these devices not only inherit the complex security requirements of networked devices, but face a whole range of new problems due to their embedded nature. Attack points are no longer restricted to insecure communication channels, as cryptodevices themselves operate in hostile environments and in physical possession of potential adversaries. Credit cards, electronic IDs and passports, or multimedia players are examples of ideal targets for malicious users or organizations aiming at financial fraud, identity theft, or product counterfeiting. Adding sound protection mechanisms to such already constrained devices goes beyond the design of secure cryptosystems, opening a challenging and active research area in the field of *physical security*.

The foreseen interconnection of billions of uniquely identifiable and addressable smart devices in the so-called Internet of Things (IoT) not only involves new security challenges. The deployment of *monitoring systems* with abilities to collect, process, and communicate data about themselves and their close environment is already raising *privacy* concerns, as this may reveal personal information about the person to whom the device is associated. While this information can be used to the user's benefit, for instance to improve and personalize services, it can also be shared or misused to build user profiles that can result in discrimination, persecution or reputation damage. Ignoring privacy concerns may result in undesired consequences for service providers, as illustrated by the recent revocation of the Dutch smart metering bill [77]. The integration of *Privacy-Enhancing Technologies* (PETs) into these envisioned services is a complex problem that requires balancing technical aspects with social, legal, and even ethical concerns.

### The Black-Box Security Model

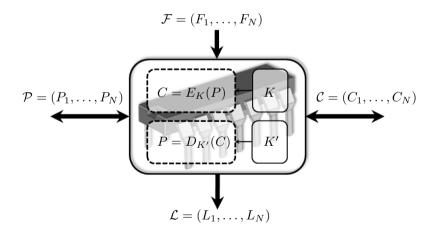

One of the first enabling foundations of modern cryptography was the work of Auguste Kerckhoffs in the second half of the 19th century [133]. In his article *La Cryptographie Militaire*, Kerckhoffs gave a series of recommendations for the design of military ciphers. Amongst them, the so-called *Kerckhoffs' principle* states that the security of a cryptosystem should not rely on the secrecy of the employed algorithms, but *only* on the secrecy of the key(s). This axiom has been long embraced by the cryptographic community to support the need for open cryptographic design, and has laid down the basis for the black-box security model depicted in Figure 1.1.

The cipher is an abstract mathematical object composed by two algorithms: encryption under key K, denoted as  $E_K$ , is the process of converting an input message P (the *plaintext*) to an unreadable string C (the *ciphertext*); decryption under key K', denoted as  $D_{K'}$ , is the complementary operation to revert an input ciphertext C to the original plaintext P. The keys need to be accordingly distributed between the communicating parties, i.e. an encryption key K must be in possession of the *sender*, whereas the corresponding decryption key K'

2

must be in possession of the *receiver*. When the key used for both encryption and decryption is the same we talk about *symmetric-key cryptography*, whereas when the keys are different - although somehow related - we talk about *public-key cryptography*. Block ciphers such as DES [5] or AES [6] and stream ciphers such as Trivium [82] are exemplary of the former category, whereas cryptosystems such as RSA [189] or ECC [163, 138] are representative of the latter.

$$\mathcal{P} = (P_1, \dots, P_N) \underbrace{\left(\begin{array}{c} C = E_K(P) \\ P = D_{K'}(C) \end{array}\right)} \mathcal{C} = (C_1, \dots, C_N)$$

Figure 1.1: The black-box security model.

The black-box model provides a framework to assess the mathematical security of a cryptographic algorithm against an attacker whose goal is typically the extraction of either of its secret key(s) K or K'. The adversary is assumed to have knowledge of both encryption E and decryption D functions. Additionally, he is given the ability to query the black-box by providing a set of plaintexts  $\mathcal{P}$ (resp. ciphertexts  $\mathcal{C}$ ) and analyze the encryption (resp. decryption) results of the black-box under the key K (resp. K'). Depending on the message selection and the control the adversary has on setting them, the literature often distinguishes between different forms of black-box cryptanalysis. Ciphertext-only attacks, known-plaintext attacks, chosen-plaintext attacks, chosen-ciphertext attacks, adaptive chosen-plaintext attacks, and adaptive chosen-ciphertext attacks [158] are the most common ones.

The security assessment of cryptographic primitives depends also on their type. Symmetric-key algorithms rely on their resistance to probabilistic methods such as linear cryptanalysis [154] or differential cryptanalysis [41]. Public-key algorithms on the other hand are based on the computational intractability of certain mathematical problems such as integer factorization in RSA or the elliptic curve discrete logarithm problem in ECC. Independently of the approach followed, a cryptographic primitive is considered secure as long as the best known attack is the exhaustive search of the key, i.e. check plaintext/ciphertext pairs against all key space. If the search space is such that it exceeds the computational resources of an adversary, then the algorithm is assumed to be *computationally secure*.

### The Grey-Box Security Model

In the late 90s, the diversification of cryptographic services and applications towards the world of low-end embedded devices triggered the appearance of a whole new range of threats often referred to as *physical attacks*. Contrary to black-box attackers, physical adversaries do not target the mathematical strength of cryptographic algorithms by solely analyzing input/output messages. Rather differently, they exploit additional leakage sources that stem from the particular *implementation* of the algorithms and/or from the embedded essence of the target device.

A cryptographic implementation on an integrated circuit is inherently subject to physical phenomena of various natures: temporal, electrical, electromagnetic, or optical, to name a few. Measurable quantities linked to internal states and operations performed by a circuit are naturally emanated through these channels. As such, they constitute a rich source of information that can be passively captured and analyzed by adversaries aiming to break the device's security properties. In addition to this, most of these physical channels can be actively altered and exploited by adversaries in possession of the circuits. By disrupting or manipulating the expected behavior of the device, it is possible to trigger errors that open the door to unexpected vulnerabilities. The grey-box model depicted in Figure 1.2 takes these considerations into account to provide an assessment framework for practical realizations of cryptography.

Figure 1.2: The grey-box security model.

The capabilities of a physical adversary are extended by two new interfaces.

A first channel denoted by  $\mathcal{L}$  models any measurable leakage source that can be naturally captured from the device under attack. These leakage data, in what follows called *side channel information*, can be later exploited by *side channel analysis*. A second channel denoted by  $\mathcal{F}$  models any physical alteration performed by an adversary on the cryptographic device, typically with the aim of disturbing its computation(s). The outcome of this disruption is often the reception of a set of corrupted outputs  $\tilde{\mathcal{C}}$  (resp.  $\tilde{\mathcal{P}}$ ) such that  $\tilde{C} \neq C$ (resp.  $\tilde{P} \neq P$ ). The *faulty information* collected as a result of this external manipulation may be subsequently exploited using *fault analysis* techniques.

#### **Adversarial Models**

Classifying the type of adversaries and their abilities is critical to determine the security requirements of a system. In the following we provide a widely accepted taxonomy originally introduced by IBM [8] and later adopted by Anderson and Kuhn [16] to the case of tamper-resistant embedded devices. It groups physical adversaries into three classes depending on their strength:

- Clever Outsider (*Class I*). An often very intelligent attacker, but constrained in terms of budget, time, and expertise. He possesses only limited information on the system under attack, e.g. publicly available documents. Adversaries in this category are likely to exploit known weaknesses rather than creating new ones.

- Knowledgeable Insider (*Class II*). A skilled specialist with vast experience and prior technical training. He possesses a wide knowledge of the targeted system, often a result of inside information. While his resources are not unlimited, he is likely to have access to advanced equipment.

- Funded Organisation (*Class III*). The most powerful adversarial model. It is often composed of a team of specialists backed by great funding resources, for instance, a country, a large corporation, or even a criminal organisation. Because of this, this adversary is capable of carrying out highly sophisticated attacks that require the possession - or even the design - of professional tools.

#### **Taxonomy of Attacks**

The wide range of existing physical attacks gives rise to multiple categorization options. Time, cost, or expertise, are just a few factors that can enable different partitions of the attack space. In the following, and as commonly accepted in the field, we categorize physical attacks according to two criteria [151].

The first criterion allows to divide physical attacks according to how an adversary manipulates the target device under the grey-box model. We denote *passive* attacks those in which the cryptographic device operates according to its functional specifications and the adversary simply collects data by monitoring the physical information channel  $\mathcal{L}$ . Side channel attacks fall in this category. In contrast, we denote *active* attacks those in which the expected normal functioning of the target device is intentionally manipulated through the channel  $\mathcal{F}$  with the goal of inducing an erroneous or unexpected behavior. Fault attacks are part of this category. Note that these attack approaches are not mutually exclusive, and therefore can be carried out simultaneously by an adversary. This is commonly referred to as *combined* attacks.

Orthogonally to the previous classification, a second criterion allows to divide physical attacks according to the level of *intrusion* performed on the circuit. Non-invasive attacks are those in which no physical alterations are performed on the device. In other words, the adversary operates the circuit in its original manufacturing form. Semi-invasive attacks on the other hand involve a certain degree of physical intrusion on the device, typically conditioned to the passivation layer not being damaged. In practice, all approaches based on decapsulation, i.e. eroding the chip surface by mechanical or chemical means, fall in this category. Finally, invasive attacks are not subject to any limitations and typically involve access to the inner elements and circuitry of the target device.

Besides providing a more granular taxonomy, the latter classification gives an intuition of the cost of the attack, i.e. the higher the degree of intrusion, the higher the cost of the equipment required to mount the attack. Invasive attacks may involve expensive equipment such as Scanning Electron Microscopes (SEM) or Focused Ion Beams (FIB). Due to this, they are out of reach to most physical adversaries including those in Class I.

### **Embedded Design for Physical Security**

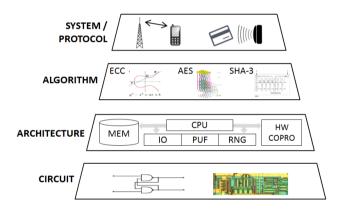

The grey-box model underlines the importance of securing embedded systems. In fact, the selection of computationally secure cryptographic primitives and protocols is only one of many steps. Integrating countermeasures against physical attacks is critical to obtain robust systems. Along with throughput, area, or energy consumption, security must be considered as a dimension of the design space [191]. For designers, this implies to follow a systematic approach considering all abstraction layers of the embedded design space, as illustrated in Figure 1.3.

The system/protocol layer specifies the security properties of the system, e.g. confidentiality, integrity, entity/data authentication, or non-repudiation. These are derived from the functionality and/or goals of the end application, and they are achieved through secure cryptographic protocols. The algorithm layer contains the building blocks required to instantiate the secure cryptographic protocols. These may include cryptographic primitives such as public-key algorithms, symmetric-key ciphers, and hash functions. The architecture layer determines the platform in which cryptographic algorithms are implemented. Depending on the system requirements, these may be developed in software (executed on a microcontroller), in hardware (executed on a dedicated coprocessor), or even in a partitioning of both approaches represented by hardware/software co-design space [190]. Finally, the circuit layer provides the mapping of the architecture level at transistor level.

Figure 1.3: The embedded design space.

Mitigations against physical attacks can be instantiated at any of these levels of the design space. However, it is important to highlight at this point that no perfect solution exists to counter all physical attacks. While one mitigation strategy may be suitable against a certain class of attacks, it is often the case that its security may be compromised when considering other approaches. In practice, chip manufacturers and smart card developers often opt for a suitable combination of countermeasures against a well-defined adversary. A product is considered secure when the amount of resources needed for breaking it outweighs the capabilities of the attacker. In practice, the resistance of security-related products against physical attacks is evaluated by specialized labs prior to obtaining a security certificate.

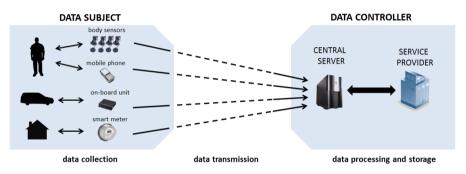

#### **Embedded Design for Privacy**

Nowadays, most deployed monitoring systems are implemented following a centralized architecture as depicted in Figure 1.4. Users (*data subjects*) provide information about themselves or their direct environment to the service provider (*data controller*), who can later process, analyze, and store it in order to provide the service. This data can range from the vital signs registered by body sensors, to the electrical consumption measurements of a smart meter or the location data collected by smartphones and in-vehicle tolling devices. From a practical perspective this kind of centralized architectures are easy to design and deploy. The intelligence and core functionality of the system resides in the domain of the data controller, which is the central element in the system. This results in minimal computing requirements for the monitoring devices and, subsequently, cheaper development costs.

Figure 1.4: Centralized architecture for exemplary monitoring systems.

From a privacy perspective however, these type of architectures suffer from a major downside. The data controller is assumed to be a *trusted party* who acts as a well-behaved keeper of users' personal information. If that is not the case, then the information disclosed by users is not secret and privacy assurances do not hold. Malicious service providers have the motivation and ability for exploiting the collected data, for instance, in order to obtain advantageous business positions. Other attack scenarios include external adversaries - or even rogue employees - accessing or sharing the collected data driven by economical incentives. Overall, it is easy to see that a central entity storing all collected information represents a *single point of failure*. Furthermore, its existence opens the possibility of personal information being systematically accessed by national law enforcement agencies, see for instance the NSA Prism program [7]. This leads to a scenario in which customers' privacy is not only violated, but in fact individuals are subject to massive *surveillance*.

The development of architectures offering strong privacy guarantees is an active area of research. The goal of these approaches is to integrate Privacy-Enhancing Technologies (PETs) as part of the system. Following the lines in [86], we define PETs as a series of technological solutions aiming to the elimination of the single point of failure inherent to centralized architectures and to the application of data minimization principles in the system's flow of information. Such guarantees can be achieved by applying a data pre-processing in the monitoring device, in such a way that only the minimum amount of information required for the provision of the service is actually disclosed to the data controller. Intuitively, this implies to de-centralize (part of) the computing functionalities from central servers to the embedded devices, resulting in potentially higher deployment costs. In contrast, the reduction of personal data within their databases may benefit data controllers. First, by reducing maintenance costs. And second, by lowering the risk of financial impact and damage to their reputation due to potential privacy breaches.

Practical deployments of privacy-preserving architectures are nevertheless not straightforward, and multiple system aspects have to be considered. Data minimization techniques must be applied without being detrimental for the provision of the service. As there is no generic mechanism or set of rules to be applied, every system requires a careful balance between its functional requirements and the privacy of users. Moreover, the integration of PETs in the system should not open the door to security vulnerabilities. This requires to perform careful threat analyses considering, among others, the applicability of physical attacks on the monitoring devices. Finally, the proposed solutions should rely on realistic assumptions and its deployment cost should not be prohibitive for the service provider.

# **1.1** About this Thesis

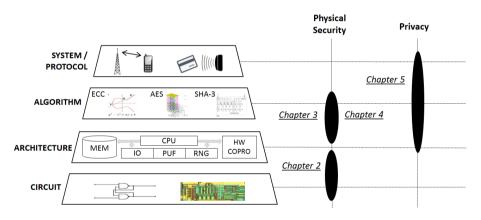

This thesis deals with implementation aspects of security and privacy into embedded systems. Its contents can be mapped to the embedded design pyramid [191] as illustrated in Figure 1.5. The focus of the first part of the dissertation is devoted to physical attacks and covers three main aspects: analysis of low-level vulnerabilities, exploitation of physical attacks, and design of mitigation techniques. Because of the broad nature of the field, our latter studies are restricted to the exploitation of *non-invasive* techniques and to the design of *high-level* countermeasures.

On the exploitation side our choice originates from vulnerability assessment. As non-invasive attacks can be carried out with relatively inexpensive equipment and limited specialized training, weaknesses identified by attackers and brought to the public knowledge can consequently be reproduced at large scale by a myriad of potential adversaries. This poses a serious threat to the security of real world embedded systems. On the mitigation side our choice arises from the fact that security provided by high-level countermeasures can often be formally proven. In other words, mitigations for physical attacks can be designed while acknowledging the physical vulnerabilities of the low-level layers.

The focus of the second part of the dissertation is devoted to privacy. Here, we show how the integration of PETs in a system can lead to strong privacy guarantees for end users. As a use case for our study, we select a high impact representative application of monitoring systems: Electronic Toll Pricing (ETP). This envisioned system is expected to be deployed in the European Union to enable variable vehicle taxing. As this system requires to process fine-grained location data about citizens, ensuring privacy protection becomes a critical design condition.

Figure 1.5: Thesis organization and link to embedded design space.

#### **Outline and Summary of Contributions**

This thesis is structured in six chapters. A description of their content and our personal contributions within each of them follows:

**Chapter 1.** The first chapter gives a brief introduction to the topics of embedded design for physical security and privacy. We first describe and compare the security assessment frameworks provided by the black-box and the grey-box models. Then, we introduce a taxonomy for physical adversaries and physical attacks, and we introduce the characteristics of the embedded design space. Next, we analyze how architectures for monitoring systems may lead to an invasion of users' privacy and how the integration of PETs can address this issue. We finish by defining the scope of this thesis and by summarizing the contents and contributions of each chapter.

**Chapter 2.** The second chapter entitled "An Insight into Physical Vulnerabilities" dives deeper into the topic of physical attacks. It explores which particularities of embedded devices and/or their implementations result in vulnerabilities. The goal of the chapter is to gain insight into the origin of physical security issues, particularly, what type of information leakage is exploited in side channel analysis and which type of induced errors enable fault analysis. A review of state-of-the-art countermeasures against physical attacks is also provided.

Our contribution within this chapter is a complete study and characterization of the effects of fault injections based on setup-time violations. These results are presented by Balasch, Gierlichs and Verbauwhede [23] at the workshop on Fault Diagnosis and Tolerance in Cryptography (FDTC 2011).

**Chapter 3.** The third chapter entitled "A Motivating Example" describes a combination of non-invasive attacks against a widely used family of secure EEPROM memories. The goal of this chapter is twofold. First, to illustrate the threat that even nowadays is posed by non-invasive physical attacks; and second, to clearly motivate the need for sound mitigation techniques.

Our contribution within this chapter is a security evaluation of the Atmel CryptoMemory family of secure EEPROMs against physical attacks. These results are presented by Balasch, Gierlichs, Verdult, Batina and Verbauwhede [24] at the Cryptographers' Track at the RSA Conference (CT-RSA 2012).

**Chapter 4.** The fourth chapter entitled "Masking at Algorithm Level" dives into the topic of high-level countermeasures, in particular, mitigations based on masking. As these techniques can be implemented at algorithm level and their security formally proven, they represent an active research area of countermeasures. We provide a comprehensive review of both state-of-the-art masking techniques and higher-order side channel attacks.

Our contribution within this chapter is the design and implementation of a novel masking scheme based on the *inner product* that can be implemented at any order. These results are presented by Balasch, Faust, Gierlichs and Verbauwhede [22] at the Annual International Conference on Theory and Application of Cryptology and Information Security (ASIACRYPT 2012).

**Chapter 5.** The fifth chapter entitled "Enabling Privacy in Embedded Design" focuses on the topic of privacy integration on monitoring systems. After

reviewing common issues with currently deployed architectures, we discuss how the use of PETs can guarantee certain privacy properties for end users.

Our contribution within this chapter is the design, analysis, and implementation of PrETP, a privacy-preserving scheme for envisioned ETP applications. These results are presented by Balasch, Rial, Troncoso, Geuens, Preneel and Verbauwhede [26] at the USENIX Security Symposium (USENIX 2010).

**Chapter 6:** The last chapter concludes this thesis and discusses open security and privacy issues in the field of embedded systems.

#### **Other Contributions**

This dissertation includes only a selection of our published works in the fields of security and privacy. In the following we summarize our remaining contributions which are not included in the core of this thesis. The publications are grouped according to their main topic.

ATTACKS ON CRYPTOGRAPHIC DEVICES.

Gone in 360 Seconds: Hijacking with Hitag2, presented by Verdult, Garcia and Balasch [222] at the USENIX Security Symposium (USENIX 2012). The work introduces a series of vulnerabilities in the Hitag2 transponders, a family of vehicle immobilizers widely used in the automotive industry. Hitag2 allows replaying reader data to the transponder, provides an unlimited keystream oracle, and uses only one low-entropy nonce to randomize a session. When wireless access to the vehicle and key is available, these weaknesses can be exploited by adversaries to recover the secret key within seconds. If only a single communication with the vehicle is possible, the running time of the attack is still less than six minutes. All proposed attacks are demonstrated in practice by experimenting with more than 20 vehicles of various makes and models.

CRYPTOGRAPHIC IMPLEMENTATIONS.

**Teaching HW/SW Co-Design With a Public Key Cryptography Application**, presented by Uhsadel, Ullrich, Das, Karaklajic, Balasch, Verbauwhede and Dehaene [218] in IEEE Transactions on Education. The work describes a lab session-based course on hardware/software co-design. The goal of the course is twofold. First, to illustrate the multiple alternative solutions available in the embedded design space. And second, to teach the fundamental concepts of hardware/software co-design. The sample application for the course project is a basic public-key application based on RSA. The project follows a step wise approach with assignments that build on each other. Students are required to make their own decisions as to the partitioning between hardware and software, the design of a communication interface, and the optimization goals. Besides imparting hard skills in embedded design, students gain several soft skills often overlooked in engineering, particularly, decision making, presentation skills, teamwork, and design creativity.

Compact Implementation and Performance Evaluation of Hash Functions in ATtiny Devices, presented by Balasch, Ege, Eisenbarth, Gérard, Gong, Güneysu, Heyse, Kerckhof, Koeune, Plos, Pöppelmann, Regazzoni, Standaert, Van Assche, Van Keer, van Oldeneel tot Oldenzeel and von Maurich [21] at the Smart Card Research and Advanced Application Conference (CARDIS 2012). The work provides a study on the software performance of multiple hash functions including the SHA-3 finalist candidates, SHA-256, recent lightweight proposals, and constructions based on block ciphers. All designs are implemented in software using an Atmel AVR ATtiny45 target platform, with the goal of minimizing code size and memory utilization. Using a common interface, the performance of all implementations is evaluated based on three main metrics: code size, RAM usage, and cycle counts for different message sizes.

PRIVACY-PRESERVING SYSTEMS.

A Privacy-Preserving Buyer–Seller Watermarking Protocol Based on Priced Oblivious Transfer presented by Rial, Balasch and Preneel [186] in IEEE Transactions on Information Forensics and Security. The work proposes a novel approach for the design of privacy-preserving buyer-seller watermarking protocols. In the proposed system, the seller authenticates buyers without learning which items are purchased. As buyers are not anonymous, customer management is eased and currently deployed methods of payment can be utilized. We define an ideal functionality for privacy-preserving copyright protection protocols. To realize our functionality, a protocol must ensure that buyers pay the right price without disclosing the purchased item, and that sellers are able to identify buyers that released pirated copies. We construct a protocol based on priced oblivious transfer and on existing techniques for asymmetric watermark embedding. Furthermore, we implement and evaluate the efficiency of our protocol, and we explain how to extend it in order to achieve optimistic fair exchange.

An Embedded Platform for Privacy-Friendly Road Charging Applications presented by Balasch, Verbauwhede and Preneel [27] in Design,

Automation and Test in Europe (DATE 2010). The work presents a practical and functional ETP system based on PriPAYD [215]. We develop a functional on-board-unit capable of processing location data in real-time, while minimizing overheads required to ensure security and privacy. The performance of our software-based prototype is tested and proves that the deployment of a privacyfriendly solution can be achieved within a minimum cost increment compared to existing schemes.

**PriPAYD:** Privacy Friendly Pay-As-You-Drive Insurance (Journal version) presented by Troncoso, Danezis, Kosta, Balasch and Preneel [214] in IEEE Transactions on Dependable and Secure Computing. This works is an updated and extended publication resulting from merging the original PriPAYD proposal in [215] and our work in [27].

# Chapter 2

# An Insight into Physical Vulnerabilities

Understanding Leakage Sources on Embedded Devices

The aim of this chapter is to give an overview of the works in the research area of physical attacks. We divide the contents of the chapter in three main blocks: side channel attacks, fault attacks, and countermeasures. The two former focus on historical and state-of-the-art aspects related to attacks on cryptographic implementations, including descriptions of the origins of leakages exploited by physical adversaries. The latter block gives an overview of mitigation techniques currently employed to secure cryptographic devices.

# 2.1 Side Channel Attacks

A side channel attack is a particular type of physical attack carried out by a *passive* adversary. Its core idea is to exploit leakage sources present in cryptographic implementations of computationally secure mathematical algorithms. This leaked information - often referred to as *side channel* - stems from observable and measurable phenomenons caused by the physical essence of digital circuits. As such, its origin is often unintentional and in most cases difficult to prevent, resulting in a major threat for the security of practical realizations of cryptography.

One of the first successful applications of side channel attacks to break

cryptographic devices is documented by former MI5 scientist Peter Wright in his memoirs [228]. Among others, the book relates the efforts of the British secret services during 1965 to intercept the communications of the Egyptian embassy, which were encrypted by a Hagelin rotor machine under a daily updated key. Wright suggested to place a microphone close to the cipher machine in order to record the sound of the rotors when new keys were being set. This additional information, together with the possession of an exact replica of the Hagelin machine, enabled MI5 to deduce the position of a few rotors, facilitating the extraction of the Egyptian secret keys.

In addition to its historical relevance, this story provides a perfect illustration of the powerful nature of side channel attacks. An adversary limited by his computational power in front of a computationally secure cipher, may use other sources of information to simplify cryptanalysis.

The rest of this section deals with the topic of side channel attacks. We start by reviewing the most common types of side channels reported in the open literature, distinguishing whether they can be accessed non-invasively or, in contrast, they require a certain degree of invasion on the device. Then, we dive deeper into the study of leakage in CMOS devices. We provide some insight on the source of these vulnerabilities and describe the most relevant attacks in the field.

## 2.1.1 An Overview of Side Channels

#### 2.1.1.1 Non-Invasive Side Channels

**Execution Time.** The first side channel attack published in the open literature dates from 1996 and is due to Paul Kocher [140]. The leakage source targeted in this seminal work is the variable execution time of cryptographic implementations. Because of optimizations in the underlying software libraries, certain arithmetic operations require more or less time to execute given different input parameters. Kocher showed how timing variances in modular multiplications allow an adversary to recover private keys used in cryptosystems such as Diffie-Hellman [87] and RSA [189] after applying some statistical analysis.

Follow-up works such as Dhem *et al.* [85] demonstrated the applicability of timing attacks on portable cryptographic tokens, while Brumley and Boneh [56] successfully targeted RSA implementations running on a local OpenSSL-based web server.

Power Consumption. Three years after the introduction of timing attacks,

Kocher, Jaffe and Jun [141] published a yet more threatening form of side channel: the power consumption. Kocher *et al.* showed that the instantaneous power consumption of a circuit over time is linked to the intermediate values and operations being processed, and presented two attacks capable of evaluating this dependence:

- Simple Power Analysis (SPA) exploits key-dependent patterns in the power consumption present in one (or very few) leakage measurements, often by simple visual inspection. Although the interpretation of power measurements requires some expertise and/or knowledge on the circuit and on the implementation, this form of attack is particularly devastating for algorithms where power patterns can be directly linked to key-bit dependent operations or branches.

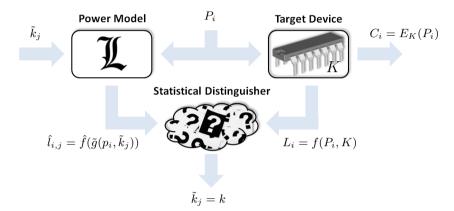

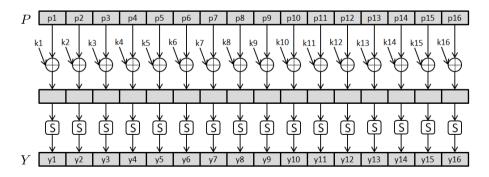

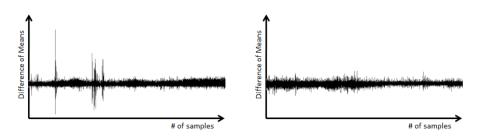

- Differential Power Analysis (DPA) exploits the leakage present on a larger set of leakage measurements. As opposed to SPA, it does not require knowledge on implementation details and its basic principles are not algorithm dependent. The first step in a DPA attack consists in building a model to estimate the power consumption of the device given a set of possibilities on a computationally suitable (sub-)key space. The second step consists in evaluating the dependence between the power model and the leakage measurements using a statistical distinguisher that yields the strongest dependency for the correct key guess.

**Electromagnetic Emanations.** The electromagnetic (EM) side channel was independently proposed by Gandolfi *et al.* [101] and Quisquater and Samyde [182] in the early 2000s. Every changing current or voltage within a circuit generates an electromagnetic field. Measurements of this field over time inherently carry information about the circuit's internal behavior, which may in turn relate to the execution of a cryptographic algorithm.

Due to their similar leakage origin, attacks exploiting the EM side channel are analogous to the ones exploiting power consumption, namely *Simple EM Analysis* (SEMA) and *Differential EM Analysis* (DEMA). Note however that while power consumption is typically tied to *global* observations of a circuit, the electromagnetic field allows to focus on *local* elements over its surface.

**Other Non-invasive Side Channels.** While execution time, power consumption, and EM emanations are often acknowledged as the most relevant and threatening side channels, other leakage sources that can be potentially exploited in a non-invasive manner have been introduced in related works:

- Temperature. Brouchier et al. [55] show how it is possible for concurrent processes running on a computer to exploit the temperature side channel, i.e. heat dissipation of the CPU, in order to gain knowledge on internal computations. Access to this side channel can indirectly be done by software commands querying the speed of the CPU fan. A recent work by Hutter and Schmidt [123] characterizes the temperature side channel on embedded microcontrollers and identifies a (low-frequency) linear relationship between heat radiation and circuit activity.

- *Visual.* Kuhn [146] delineates a mechanism to eavesdrop contents displayed by a cathode-ray tube monitor at a distance, using off-the-shelf components such as a photomultiplier tube and a computer equipped with a fast analog-to-digital converter.

- Acoustic. Along with the previously mentioned attack of Wright [228], a study by Shamir and Tromer [203] demonstrates that some patterns of operations can be recognized by the sound emanated by a CPU. This low-frequency side channel stems from mechanical stress due to continuous heating and cooling effects.

#### 2.1.1.2 (Semi-) and Invasive Side Channels

The previous side channels can be accessed in the vicinity of the target device, i.e. without need of tampering with its physical structure. However, it may be the case that adversaries can profit from a certain level of intrusion if it is within their capabilities. For instance, a semi-invasive approach based on chip decapsulation allows to bring the EM coil close to the passivation layer and therefore improve the signal to noise ratio of the leakage measurements [101].

Ferrigno and Hlavác [97] recently introduced the optical side channel, exploiting the number of photons that are emitted by transistors of an integrated circuit when changing their state. Access to such information not only requires techniques to thin down and polish the silicon layer on the backside of the die, but also specialized equipment to measure emitted photons. Recent works by Schlosser *et al.* [193] and Kramer *et al.* [144] have shown how this side channel can be exploited similar to SPA and DPA techniques, respectively, while proposing alternatives to lower the cost of the equipment.

A particular type of invasive attacks is based on (micro-)probing techniques [143]. These attacks target inner elements of a circuit that store or transport sensitive information, for instance, secret cryptographic key(s). By placing a thin needle on top of such elements adversaries can directly read out values processed by the circuit. Due to this, probing based attacks are often not considered as

side channel attacks, but rather a particular case of passive invasive attacks. Needless to say, access to such fine grained information requires expensive equipment and thus its applicability is bounded to specialized labs or attackers.

#### 2.1.2 Side Channel Leakage in Integrated Circuits

Complementary Metal-Oxide-Semiconductor (CMOS) is the predominant technology used nowadays in integrated circuits. One of the characteristics of CMOS, which justifies its dominance in the field, is its low energy usage. In fact most of the energy consumption of CMOS devices occurs dynamically as the circuit changes its state, while the static power consumption of the device is only significantly increasing in deep submicron technologies. Logic cells in a circuit are typically implemented using complementary transistors, i.e. there exist a pull-up network composed of P-transistors connected to  $V_{DD}$  and a pull-down network of N-transistors connected to GND.

For illustrative purposes let us consider the case of one of the simplest CMOS cells: an inverter, whose input/output transition table is depicted in Figure 2.1 (left). When there is no input transition the inverter circuit remains idle, and only the (rather low) static component of the current flows through the conducting transistor. When there is an input transition from high to low  $(1 \rightarrow 0)$ , the pull-up network of the circuit (P-transistor) becomes active. A dynamic current flows through the circuit in order to charge the load capacitance, as shown in Figure 2.1 (middle), effectively generating an output transition from low to high  $(0 \rightarrow 1)$ . Finally, when the input transition goes from low to high  $(0 \rightarrow 1)$  the pull-down network becomes active. In this case there appears a short-circuit current that causes the load capacitance to be discharged, producing an output transition from high to low  $(1 \rightarrow 0)$ .

Figure 2.1: CMOS inverter. Transition table (left), charge circuit (center), discharge circuit (right).

The previous example highlights the inherent information leakage behavior of CMOS cells: dynamic current reveals information about inner transitions. As digital circuits are comprised of many logic cells, this effect can be observed at a global scale. Note however that several aspects influence and determine this leakage, for instance, the total number of logic cells, their interconnections, or the manufacturing process, among others.

#### 2.1.2.1 Access to Side Channel Data

How to access and measure the leakage of CMOS devices is the first issue a side channel adversary must tackle. Figure 2.2 depicts the typical main elements of a measurement setup, namely a computer, an oscilloscope, and a target cryptographic device. The computer acts as the central element of the setup. It communicates with the cryptographic device, e.g. to provide commands/plaintexts and to collect ciphertexts, as well as with the oscilloscope, e.g. to retrieve digitized side channel measurements. The oscilloscope is required to acquire and record side channel signals from the target device *while* executing a cryptographic operation. Note however that oscilloscopes can only measure voltages, so the adversary needs to provide a means to "convert" the side channel of interest, i.e. power consumption or EM emanations, into a voltage signal.

Figure 2.2: Typical non-invasive side channel measurement setup.

The instantaneous power consumption of the circuit over time can be measured by probing the voltage drop over a shunt resistor - typically of a few *Ohms* placed into the  $V_{DD}$  or GND line of the target device. From Ohm's Law it follows that the voltage drop over this resistor is proportional to the current that flows through it, which corresponds to the current drawn by the device. This, in turn, is proportional to the device's instantaneous power consumption. Alternatively, one can directly employ current probes internally equipped with circuitry to convert the current in the  $V_{DD}$  or GND lines to voltage.

The electromagnetic field caused by the electrical activity of the circuit can be measured by means of H-field or E-field probes placed over the surface of the target device. These probes provide a voltage signal proportional to the field's amplitude. The size of the coil determines the granularity of the measurements; it can cover larger or smaller areas of the target device.

Independently of the leakage source selection, it is clear that the cost for building a non-invasive side channel measurement setup is rather low, particularly when compared to the equipment necessary to carry out invasive attacks. It is important to remark that timing side channels are also captured with such measurement setup, as oscilloscopes inherently measure over time.

#### 2.1.2.2 Inspection of Traces

A trace captured by an oscilloscope during the execution of a cryptographic operation carries several types of information of interest to an adversary: the existence of *patterns* within the measurement is related to the structure of its implementation; the *amplitude* of the curve peaks carries information about the type of operation being performed and the data being processed; and the *timing* allows to distinguish variations in the program flow.

In order to illustrate these effects, let us consider an adversary in possession of a cryptographic device that performs bulk encryption. Let us further assume that specifications of the device, i.e. hardware or software implementation, processor type, etc., are not known to the attacker. Using a suitable measurement setup, the adversary captures a trace as shown in Figure 2.3. A quick observation of the global trace in Figure 2.3a reveals a series of patterns (highlighted by dotted lines) that stem from the structure of the algorithm's implementation. In particular, one can easily identify nine identical patterns followed by a shorter, yet rather similar one. Such a construction is consistent with the 128-bit version of the Advanced Encryption Standard (AES-128), composed of 10 encryption rounds with the particularity that the last round omits one operation.

Zooming into the rounds as illustrated in Figure 2.3b allows to visualize their inner structure. The round operations of AES - SubBytes, ShiftRows, MixColumns and AddRoundKey - give rise to four distinguishable patterns. Notice that the amplitude of some peaks within the SubBytes and MixColumns computations is slightly higher than the rest. As these operations are often implemented by means of look-up tables in memory, one can infer that memory

(c) A few cycles during the execution of AES-128.

Figure 2.3: A trace of an AES execution on an embedded device (a), zooming into first rounds (b), and zooming of a few cycles (c).

access operations consume more power than e.g. atomic operations in the Arithmetic Logic Unit (ALU).

Finally, a further zoom into a few clock cycles is depicted in Figure 2.3c. One can clearly notice here the charging/discharging effects of the CMOS cells within the circuit. The dotted lines denote the separation between consecutive clock periods; the two peaks within a single cycle indicate this particular circuit performs activities at both the rising and falling clock edges.

#### 2.1.2.3 Modeling Traces

The information contained in a single point of a trace is often modeled as the sum of four main components [151]:

$$P_{total} = P_{op} + P_{data} + P_{noise} + P_{const}.$$

The two first components -  $P_{op}$  and  $P_{data}$  - denote the operation-dependent and data-dependent contributions, respectively;  $P_{noise}$  corresponds to electrical noise inherently caused by the measurement setup, and can be modeled as a normal distribution [151]; finally,  $P_{const}$  represents a constant independent of the operation or data processed.

Quantifying the data-dependent component  $P_{data}$  of a circuit is one of the first goals of an adversary, as this can help enhancing attacks at a later stage. One of the most employed models in the literature is the *Hamming Weight* (HW) model. It basically assumes that the data-dependent power consumption of a digital circuit is directly correlated to the number of bits equal to one in the data being processed. In other words, the power consumption of a device processing a variable Y on a certain clock cycle is proportional to HW(Y).

Other models, such as the Hamming Distance (HD) model, take into account data transitions within consecutive clock cycles. In this case the power consumption of a device when switching from a value X to a value Y is given by  $HD(X,Y) = HW(X \oplus Y)$ . Figure 2.4 depicts a series of traces obtained from a CMOS device when performing data transitions on an 8-bit data bus. For each power trace, two random 8-bit values ranging from 0 to 255 are consecutively loaded from RAM to CPU registers. We average all traces with equal Hamming distance in order to remove the effects of the noise. By doing this, one can easily verify that the data-dependency of this device follows a Hamming distance model: the number of bit transitions between memory operations determines the amplitude of the measurement peak.

Figure 2.4: Transitions on the data bus of a CMOS device.

Further leakage models proposed in the literature aim to consider different bit transition leakages [171]. The research area of profiled attacks, which will be discussed later in the chapter, uses advanced statistical tools to fully characterize a device's leakage [63, 192].

# 2.1.3 Exploitation of Traces

So far we have introduced the type of information observed and/or expected in power and EM measurements. In the following we review the most common types of *power analysis* attacks proposed in the literature. Note that these attacks can be carried out with EM measurements instead of power traces.

#### 2.1.3.1 Simple Power Analysis

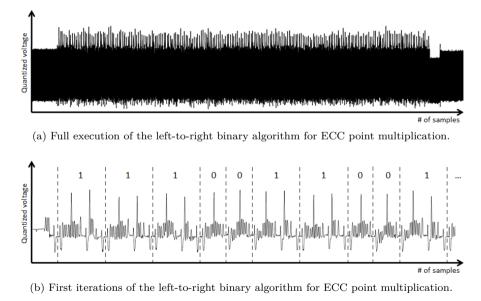

Simple Power Analysis (SPA) was introduced in the seminal work by Kocher *et al.* [141]. The core idea of this attack is the direct exploitation of key-dependent leakages present in one or a small number of power traces. Its application is often based on heuristic analyses of visually identifiable leakages within traces. Because of this, and contrary to its name, it often requires experienced adversaries with detailed knowledge of the cryptographic implementation and the architecture of the target device.