#### KATHOLIEKE UNIVERSITEIT LEUVEN

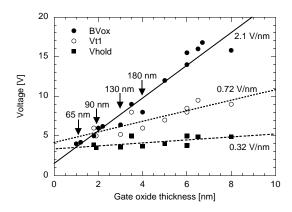

FACULTEIT INGENIEURSWETENSCHAPPEN DEPARTEMENT ELEKTROTECHNIEK AFDELING ESAT - DIVISIE INSYS Kasteelpark Arenberg 10, B-3001 Leuven, België

### ESD Protection for Multiple Gate Field Effect Devices and for RF CMOS Circuits

Promotor : Prof. Dr. Ir. Guido GROESENEKEN Proefschrift voorgedragen tot het behalen van het doctoraat in de Ingenieurswetenschappen

door

Steven THIJS

September 2009

In samenwerking met

Interuniversitair Micro-Elektronica Centrum Kapeldreef 75 B-3001 Leuven (België)

#### KATHOLIEKE UNIVERSITEIT LEUVEN

FACULTEIT INGENIEURSWETENSCHAPPEN DEPARTEMENT ELEKTROTECHNIEK AFDELING ESAT - DIVISIE INSYS Kasteelpark Arenberg 10, B-3001 Leuven, België

### ESD Protection for Multiple Gate Field Effect Devices and for RF CMOS Circuits

Examencommissie:

Prof. Dr. Ir.

A. Haegemans, voorzitter

Prof. Dr. Ir.

G. Groeseneken, promotor

Prof. Dr. Ir. G. Vandenbosch

Prof. Dr. Ir. H. Maes

Prof. Dr. Ir. G. Meneghesso

Dr. Ir. M. Jurczak Dr. Ir. H. Gossner Proefschrift voorgedragen tot het behalen van het doctoraat in de Ingenieurswetenschappen

door

Steven THIJS

September 2009

In samenwerking met

Interuniversitair Micro-Elektronica Centrum Kapeldreef 75 B-3001 Leuven (België)

©2009 Katholieke Universiteit Leuven - Faculteit Ingenieurswetenschappen Arenbergkasteel, B-3001 Heverlee (België)

Alle rechten voorbehouden. Niets van deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt door middel van druk, fotocopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever.

All rights reserved. No part of this publication may be reproduced in any form by print, photoprint, microfilm, or any other means without written permission from the publisher.

ISBN: 978-94-6018-104-7

Wettelijke depotnummer: D/2009/7515/87

## Acknowledgements

Even though there's only one author mentioned on the title page of this PhD, the work of the past three years would have never been possible without being surrounded by many world-class experts, each in their own field. Therefore, I would like to express my gratitude to everybody who helped me in achieving my goals, not only for writing this thesis, but also for allowing me to grow in my professional career.

First, I would like to thank Professor Guido Groeseneken for making it possible for me to return to IMEC to start this PhD and for his excellent work promoting my thesis. Every time I thought I finished some part, Guido would read it and would make some suggestions of things to change or things to add... and every time it was a wise thing to follow these suggestions.

Secondly, I would like to acknowledge my jury for their careful review and contributions: Prof. Dr. Ir. Guy Vandenbosch, Prof. Dr. Ir. Herman Maes, Prof. Dr. Ir. Gaudenzio Meneghesso, Dr. Ir. Harald Gossner and Dr. Ir. Malgorzata Jurczak.

Special thanks need to go out to my colleagues Dimitri Linten and Mirko Scholz. They assisted me in so many ways in finishing this PhD! Even more important, they always were in for a good laugh. Everyday it was a pleasure to come to work and I'm very proud of being a member of our successful ESD Expertise Center.

Also, I need to acknowledge the European FinFET ESD members, Christian Russ, David Trémouilles and Alessio Griffoni. It just makes it so much easier, when you can work together with such experts!

The benefit of working at IMEC is that the experts are always closeby, you only need to find their office. During this PhD work, I was able to find Rita Rooyackers, Nadine Collaert, Ann De Keersgieter, Jonathan Borremans, Kuba Raczkowski, Morin Dehan, Bertrand Parvais, Piet Wambacq, Sandeep Sangameswaran and Abdelkarim Mercha. Thank you all for taking your time to listen to my numerous questions and for all the joint publications!

I must also thank my former ESD colleagues who helped me taking my first steps in the fascinating ESD world. They have made it possible that I am where I am today. Thank you Vesselin Vassilev, Vincent De Heyn, Tom Daenen, Vaidyanathan Subramanian (Vaidy) and Natarajan Mahadeva Iyer (Raju)! Especially Raju deserves an extra word here. He has taught me many things, not only in my professional life, but also in my personal life. Sometimes it's just hard to believe how generous and kind people can be.

Finally I would like to thank my parents for giving me the chance to start studying and make something of my life. Also, I would like to thank my wife Katarina for all the support she has given me and for her patience of dealing with me everyday. En natuurlijk ook een dikke kus van papa aan zijn twee liefste schatjes Nyo en Ime!

Thank you all!

Steven Thijs Leuven, September 2009

### Abstract

This thesis addresses two main ESD challenges which lie ahead. First, FinFET technology has a limited available silicon volume to dissipate the ESD current. Therefore, a detailed ESD analysis on FinFET devices is required. Secondly, as technology downscaling allows RF applications operating at higher RF frequencies and wider bandwidths, to be implemented in CMOS, adequate ESD protection needs to be developed without compromising RF performance. Moreover, these enabling technologies simultaneously become more susceptile to ESD stress due to reduced gate oxide breakdown voltages and device power handling capabilities.

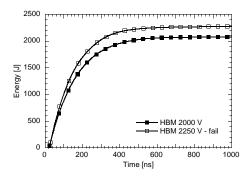

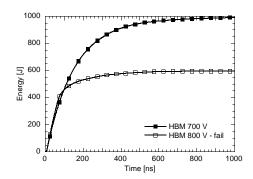

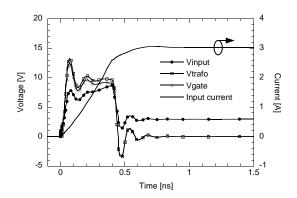

To be able to investigate these two challenges in more detail, limitations of the current commercially available ESD measurement equipment need to be overcome. In this thesis, three enhanced ESD characterization and analysis techniques have been developed. First, a Multi-level TLP system was developed enabling the measurement of the true holding voltage as well as the real device physics under ESD stress. Secondly, as gate oxides become more fragile due to technology scaling, the transient turn-on response of the ESD protection devices becomes critical. This turn-on is investigated by a newly developed method to calibrate and analyze the TLP voltage and current waveforms. We have developed a fast, powerful method referred to as HBM-IV, where during an HBM stress pulse, besides the similar quasi-static information as from TLP, also the transient turn-on information is obtained. HBM-IV on a high voltage example shows that under HBM stress, voltage and current overshoots can occur which cannot be reproduced by TLP pulses.

ESD analysis has been performed on ESD protection structures, implemented in SOI FinFET technology. It is found that a new normalization methodology is needed for correct interpretation of the ESD results. Complex dependencies of the different ESD performance parameters on both device geometry and process technology are found. Non-uniform failure exists for grounded gate NMOS devices at high current levels which can be improved by increasing gate length and various ballasting techniques. Narrow fin devices have improved cooling properties but suffer from reduced area efficiency. Well doping, selective

epitaxial growth, strain and silicide blocking can improve the ESD performance. From RF point of view, the large overhead capacitance of the narrow fin devices degrades the RF figure of merit with respect to the wide fin devices, making wide fin devices the preferred choice. To be able to cope with this complex set of dependencies, a design methodology is developed which allows optimization towards a given ESD target while taking these dependencies into account. As such, efficient ESD protection can be designed in FinFET technology, achieving product level HBM levels.

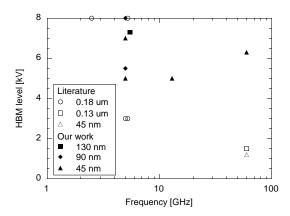

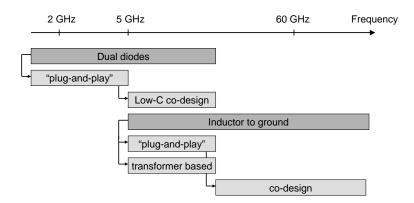

Classical low-capacitive RF-ESD solutions become worse when RF frequencies increase resulting in either degraded RF or ESD performance. Further, CDM protection needs more attention due to its fast rising, high current pulses, travelling along unknown current paths, causing voltage overshoots and turn-on of parasitic current paths. We propose inductive ESD protection as narrowband RF-ESD solution due to its high ESD robustness, low RF impact and large frequency scaling potential. It can be either implemented as a "plug-and-play" inductor to ground, or using an RF-ESD co-designed transformer. CDM robustness is predicted by means of on-wafer VFTLP measurements, allowing identification of possible weak spots at an early design stage. High-quality inductors in combination with voltage clamping diodes can provide very high VFTLP robustness. The future scaling possibilities of the inductor to ground approach are demonstrated in 45 nm planar and FinFET CMOS technologies, up to RF frequencies of 60 GHz. At these frequencies, less ESD signal couples into the RF circuit and due to the decreased inductance of the inductor to ground, less voltage overshoot is present. Therefore, with increasing frequency, the inductor to ground methodology becomes better in terms of RF performance, ESD performance and area consumption, yielding world-record results.

Two-novel wideband RF-ESD protection solutions are proposed with the potential of providing high ESD protection levels at very large bandwidths. First, the "T-diode"-concept uses a transformer to tune out the parasitic capacitance of the ESD protection devices over a wide frequency band. Input matching is maintained from DC to 16.1 GHz, in a 90 m digital CMOS technology. Local clamping and additional turn-off circuitry to prevent failure of parasitic current paths inside the RF core circuit, further increase the ESD robustness level. Secondly, a novel distributed ESD concept (Center Balanced Distributed ESD) is developed, specifically for distributed amplifier circuits. A 1-110 GHz distributed amplifier in 45 nm CMOS is protected using this methodology, yielding excellent ESD robustness.

In conclusion, ESD is not a showstopper for the introduction of FinFET technology. Further, efficient ESD solutions can be implemented for narrow- and wideband RF circuits which exhibit both excellent RF and ESD performance.

# List of Acronyms

ADAnalog-Digital BCDBipolar CMOS DMOS (smart power IC technology) BEOLBack End of Line BiCMOS Bipolar Complementary Metal Oxide Semiconductor (technology) BJTBipolar Junction Transistor Buried Oxide BOXBVBreakdown Voltage BWBandWidth CCTLPCapacitively Coupled Transmission Line Pulse Contact Etch Stop Layer CESLCBDESD Center Balanced - Distributed ESD CDMCharged Device Model CNTCarbon Nano Tube CMOSComplimentary Metal Oxide Semiconductor (technology) DADistributed Amplifier DCDirect Current DIBLDrain Induced Barrier Lowering Design Rule Check DRCDTSCRDiode Triggered Silicon Controlled Rectifier DUTDevice Under Test EOTEquivalent Oxide Thickness ESDElectro Static Discharge ESDAElectro Static Discharge Association EOSElectrical Overstress FDSOIFully Depleted Silicon On Insulator FEDField Effect Diode FEOLFront End of Line FinFETFin Field Effect Transistor FOMFigure of Merit ggNMOS grounded-gate NMOS HARViHigh Aspect Ratio Via HBMHuman Body Model

HMM Human Metal Model

HV High Voltage IC Integrated Circuit

IEC International Electrotechnical Commission

IMD Inter-Metal Dielectric

ITRS International Technology Roadmap for Semiconductors

JEDEC Joint Electron Device Engineering Council

LDD Lightly Doped Drain LNA Low Noise Amplifier

LVTSCR Low Voltage Triggered Silicon Controlled Rectifier

M Multiplication Factor

MEMS MicroElectroMechanical System

MIM Metal Insulator Metal

MM Machine Model MOM Metal Oxide Metal

MOCVD Metal-Organic Chemical Vapour Deposition

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MTLP Multi Level Transmission Line Pulse OEM Original Equipment Manufacturers OPC Optical Proximity Correction

PA Power Amplifier PC Power Clamp

PDSOI Partially Depleted Silicon On Insulator

RF Radio Frequency SB Silicide Blocking SCE Short Channel Effect SCC Short Channel Control SCR Silicon Controlled Rectifier

SDF Spacer Defined Fins

SEG Selective Epitaxial Growth SEM Scanning Electron Microscope

SOI Silicon On Insulater STI Shallow Trench Isolation

TCAD Technology Computer Aided Design tCESL tensile Contact Etch Stop Layer TDR Time Domain Reflectometry TDT Time Domain Transmission TEM Transmission Electron Microscope TIM Transient Interferometric Mapping

$\begin{array}{ll} TSV & \text{Through-Silicon Via} \\ TLP & \text{Transmission Line Pulse} \\ TWA & \text{Traveling Wave Amplifier} \end{array}$

VDMOS Vertical Diffused Metal Oxide Semiconductor

VFTLP Very Fast Transmission Line Pulse

$\begin{array}{ll} UTB & \quad \text{Ultra Thin Body} \\ UWB & \quad \text{Ultra WideBand} \end{array}$

WCDMA Wideband Code Division Multiple Access

WLAN Wireless Local Access Network

WLP Wafer Level Packaging

# List of Symbols

$\beta$  Weibull Slope

$BV_{CBO}$  Common Base Breakdown Voltage  $BV_{CEO}$  Common Emitter Breakdown Voltage

$BV_{ox}$  Oxide Breakdown Voltage

$C_B$  Board Capacitance  $C_{CDM}$  CDM DUT Capacitance

$C_{DUT}$  DUT Capacitance

$C_{ESD}$  Capacitance of ESD Device

$C_{HBM}$  HBM Capacitance  $C_j$  Junction Capacitance  $C_{MM}$  MM Capacitance

$C_{narrow}$  Capacitance of Narrow Fin Device

$C_{oh}$  Overhead Capacitance

$C_{pla}$  Capacitance of Wide (Planar) Fin Device

$C_{PROB}$  Voltage Probe Capacitance  $C_{tot}$  Total Device Capacitance

E(t) Dissipated Energy as function of Time

$f_C$  Corner Frequency

$f_T$  Unity Current Gain Cutoff Frequency

$\gamma$  Voltage Acceleration Factor

GBW Gain Band Width  $g_{ds}$  Output Conductance  $g_m$  Transconductance

$H_{fin}$  Fin Height

$I_d$  Diffusion Leakage Current  $I_{ds}$  Drain to Source Current

$I_{ESD}$  ESD Current

IIP3 Third Order Input referred Intercept Point

$I_m$  Modulated Current  $I_{on}$  MOS Drive Current

I(t) Current as function of Time

$egin{array}{ll} It_1 & {

m Trigger~Current} \\ It_2 & {

m Failure~Current} \\ k & {

m Coupling~Factor} \\ \end{array}$

$L_{cont}$  Size of Source/Drain Contact Area  $L_{ESD}$  Inductance of ESD Protection Inductor

$L_g$  Gate Length  $L_s$  Series Inductance

$L_{SD}$  Distance between Source/Drain Contact Area

and Gate

M Mutual Inductance M Multiplication Factor

$M_n$  Electron Current Multiplication Factor  $M_p$  Hole Current Multiplication Factor

n Turn Ratio of transformer

N Number of Fins

nblocks Number of Parallel Device Blocks

NF Noise Figure

$q_e$  Injected Charge due to Diffusion Current

$\begin{array}{ll} q_m & \text{Charge in the Base Region} \\ R_{CDM} & \text{CDM Discharge Resistance} \\ R_{HBM} & \text{HBM Discharge Resistance} \\ R_{mo} & \text{Initial Bulk Resistance} \end{array}$

$R_{on}$  On-Resistance

$R_s$  Series Resistance  $R_s$  Source Impedance

$R_{s,ESD}$  Series Resistance of ESD Device

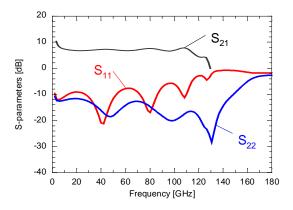

$R_{tot}$  Total Resistance  $S_{11}$  Input Matching  $S_{12}$  Reverse Isolation

$S_{21}$  Gain

$S_{22}$  Output Matching

$S_{norm}$  Normalized Fin Spacing

$egin{array}{ll} S & & {

m Fin \ Spacing} \\ au & {

m Carrier \ Lifetime} \\ au & {

m Electrical \ Delay} \\ \end{array}$

$T_{BOX}$  Thickness Buried Oxide Layer

$t_{fr}$  Forward Recovery Time

$\begin{array}{ll} T_m & \text{Transit Time} \\ V_{BD} & \text{Breakdown Voltage} \\ V_{CDM} & \text{CDM Precharge Voltage} \\ V_{DD} & \text{Power Supply Voltage} \\ V_{drop} & \text{Voltage Drop during ESD} \end{array}$

$V_{GS}$  Gate to Source Voltage

$V_h$  Holding Voltage

$V_{HBM}$  HBM Precharge Voltage

$V_j$  Junction Voltage  $V_M$  Modulated Voltage

$V_{max}$  Maximum Allowed Voltage  $V_{MM}$  MM Precharge Voltage  $V_{CR}$  Ground Potential

$V_{SS}$  Ground Potential  $V_T$  Threshold Voltage

V(t) Voltage as function of Time

$Vt_1$  Trigger Voltage  $Vt_2$  Failure Voltage  $W_{chan}$  Channel Width  $W_{eff}$  Effective Width  $W_{ext}$  Overlap Gate on Fins

$\begin{array}{ll} W_{fin} & \text{Fin Width} \\ W_{gen} & \text{Generic Width} \\ W_{intr} & \text{Intrinsic Width} \\ W_{layout} & \text{Total Layout Width} \\ W_{norm} & \text{Normalized Width} \end{array}$

$Z_c$  Characteristic Impedance  $Z_{ESD}$  Impedance of ESD Device

## Publication list

#### Journal Contributions - First Author

- J1 S. Thijs, M. I. Natarajan, D. Linten, W. Jeamsaksiri, T. Daenen, R. Degraeve, A. J. Scholten, S. Decoutere and G. Groeseneken, "Implementation of Plug-and-Play ESD Protection in 5.5 GHz 90 nm RF CMOS LNAs Concepts, Constraints and Solutions", *Microelectronics Reliability*, Vol. 46, Issues 5-6, pp. 702-712, May-June 2006.

- J2 S. Thijs, D. Trémouilles, C. Russ, A. Griffoni, N. Collaert, R. Rooyackers, D. Linten, M. Scholz, C. Duvvury, H. Gossner, M. Jurczak and G. Groeseneken, "Characterization and Optimization of Sub-32nm Fin-FET Devices for ESD Applications", *IEEE Transactions on Electron Devices*, Vol. 55, no. 12, pp. 3507-3516, December 2008.

#### Journal Contributions - Second Author

- J3 V. Vassilev, S. Thijs, P. L. Segura, P. Wambacq, P. Leroux, M. I. Natara-jan, G. Groeseneken, H. E. Maes and M. Steyaert, "ESD RF Co-Design Methodology for the State of the Art RF-CMOS Blocks", *Microelectronics Reliability*, Vol. 45, Issue 2, pp. 255-268, February 2005.

- J4 D. Linten, S. Thijs, M. I. Natarajan, W. Jeamsaksiri, J. Ramos, A. Mercha, S. Jenei, S. Donnay and S. Decoutere, "A 5-GHz Fully Integrated ESD-Protected Low-Noise Amplifier in 90-nm RF CMOS", *IEEE Journal of Solid-State Circuits*, Vol. 40, Issue 7, pp. 1434-1442, July 2005.

- J5 D. Trémouilles, S. Thijs, Ph. Roussel, M. I. Natarajan, V. Vassilev and G. Groeseneken, "Transient Voltage Overshoot in TLP Testing - Real or Artifact?", Microelectronics Reliability, Vol. 47, Issue 7, pp. 1016-1024, July 2007.

- **J6** J. Borremans, **S. Thijs**, P. Wambacq, Y. Rolain, D. Linten and M. Kuijk, "A Fully-Integrated 7.3 kV HBM ESD-Protected Transformer-Based 4.5-6 GHz CMOS LNA", *Journal of Solid-State Circuits*, Vol. 44, Number 2,

- pp. 344-353, February 2009.

- J7 D. Linten, S. Thijs, J. Borremans, M. Dehan, D. Trémouilles, M. Scholz, M. I. Natarajan, P. Wambacq, S. Decoutere, and G. Groeseneken, "A Plug-and-Play Wideband RF Circuit ESD Protection Methodology: T-Diodes", Microelectronics Reliability, To be published, 2009.

- J8 A. Griffoni, S. Thijs, C. Russ, D. Trémouilles, D. Linten, M. Scholz, E. Simoen, C. Claeys, G. Meneghesso and G. Groeseneken, "Electrical-Based ESD Characterization Methodology for Ultrathin Body SOI MOS-FETs", IEEE Transactions on Device and Materials Reliability, Submitted, 2009.

#### Journal Contributions - Co-Author

- J9 V. Vassilev, S. Jenei, G. Groeseneken, R. Venegas, S. Thijs, V. De Heyn, M. I. Natarajan, M. Steyaert and H. E. Maes, "High Frequency Characterization and Modelling of the Parasitic RC Performance of Two Terminal ESD CMOS Protection Devices", Microelectronics Reliability, Vol. 43, Issue 7, pp. 1011-1020, July 2003.

- J10 A. Mercha, W. Jeamsaksiri, J. Ramos, M. Dehan, D. Linten, S. Thijs, S. Jenei, P. Wambacq, G. Carchon and S. Decoutere, "Potentials of the 90nm CMOS Technology for Monolithic Integration", HF Revue - HF Tijdschrift, Issue 2, pp. 17-28, 2005.

- J11 M. Scholz, D. Linten, S. Thijs, S. Sangameswaran, M. Sawada, T. Nakaei, T. Hasebe and G. Groeseneken, "ESD On-Wafer Characterization: Is TLP still the Right Measurement Tool?", IEEE Transactions on Instrumentation and Measurements, To be published, 2009.

#### Conference Contributions - First Author

- C1 S. Thijs, V. De Heyn, M. I. Natarajan, V. Vassilev, W. Jeamsaksiri, D. Linten, T. Daenen, V. Subramanian, G. Groeseneken, M. Jurczak and R. Rooyackers, "Impact of Elevated Source Drain Architecture on ESD Protection Devices for a 90nm CMOS Technology Node", EOS/ESD Symposium, pp. 242-249, 2003.

- C2 S. Thijs, M. I. Natarajan, D. Linten, V. Vassilev, T. Daenen, A. J. Scholten, R. Degraeve, P. Wambacq and G. Groeseneken, "ESD Protection for a 5.5 GHz LNA in 90 nm RF CMOS Implementation Concepts, Constraints and Solutions", *EOS/ESD Symposium*, pp. 40-49, 2004. Best paper award

- C3 S. Thijs, M. I. Natarajan, D. Linten, V. Vassilev, T. Daenen, A. J. Scholten, R. Degraeve, P. Wambacq and G. Groeseneken, "ESD Protection for a 5.5 GHz LNA in 90 nm RF CMOS Implementation Concepts, Constraints and Solutions", *Reliability Center for Electronic Components of Japan Symposium*, 2004.

- C4 S. Thijs, D. Linten, M. I. Natarajan, W. Jeamsaksiri, A. Mercha, J. Ramos, X. Sun, G. Carchon, P. Soussan, T. Nakaie, M. Sawada, T. Hasebe, P. Wambacq, S. Decoutere and G. Groeseneken, "Class 3 HBM and Class C MM ESD Protected 5.5 GHz LNA in 90 nm RF CMOS using Above-IC Inductors", EOS/ESD Symposium, pp. 25-32, 2005.

- C5 S. Thijs, D. Linten, M. I. Natarajan, W. Jeamsaksiri, A. Mercha, J. Ramos, X. Sun, G. Carchon, P. Soussan, T. Nakaie, M. Sawada, T. Hasebe, P. Wambacq, S. Decoutere and G. Groeseneken, "Class 3 HBM and Class C MM ESD Protected 5.5 GHz LNA in 90 nm RF CMOS using Above-IC Inductors", Reliability Center for Electronic Components of Japan Symposium, 2006.

- C6 S. Thijs, C. Russ, D. Trémouilles, D. Linten, M. Scholz, M. Jurczak, N. Collaert, R. Rooyackers, C. Duvvury, H. Gossner and G. Groeseneken, "Design Methodology for FinFET GG-NMOS ESD Protection Devices", International ESD Workshop, 2008.

- C7 S. Thijs, C. Russ, D. Trémouilles, A. Griffonis, D. Linten, M. Scholz, N. Collaert, R. Rooyackers, M. Jurczak, M. Sawada, T. Nakaie, T. Hasebe, C. Duvvury, H. Gossner and G. Groeseneken, "Design Methodology of FinFET Devices that Meet IC-Level HBM ESD Targets", EOS/ESD Symposium, pp. 295-303, 2008.

- C8 S. Thijs, M. Okushima, J. Borremans, P. Jansen, D. Linten, M. Scholz, P. Wambacq and G. Groeseneken, "Inductor-based ESD Protection under CDM-like ESD Stress Conditions for RF Applications", *IEEE Custom Integrated Circuits Conference*, pp. 49-52, 2008.

- C9 S. Thijs, D. Trémouilles, A. Griffoni, C. Russ, D. Linten, M. Scholz, N. Collaert, R. Rooyackers, C. Duvvury and G. Groeseneken, "Electrical and Thermal Scaling Trends for SOI FinFET ESD Design", EOS/ESD Symposium, To be published, 2009.

- C10 S. Thijs, K. Raczkowski, D. Linten, M. Scholz, A. Griffoni and G. Groeseneken, "CDM and HBM Analysis of ESD Protected 60 GHz Power Amplifier in 45 nm Low-Power Digital CMOS", EOS/ESD Symposium, To be published, 2009.

C11 S. Thijs, D. Linten, C. Pavageau, M. Scholz and G. Groeseneken, "Center Balanced Distributed ESD Protection for 1-110 GHz Distributed Amplifier in 45 nm CMOS Technology", *EOS/ESD Symposium*, To be published, 2009.

#### Conference Contributions - Second Author

- C12 V. Vassilev, S. Thijs, P. L. Segura, P. Leroux, P. Wambacq, G. Groeseneken, M. I. Natarajan, M. Steyaert and H. E. Maes, "Co-Design Methodology to Provide High ESD Protection Levels in the Advanced RF Circuits", EOS/ESD Symposium, pp. 195-203, 2003.

- C13 D. Linten, S. Thijs, W. Jeamsaksiri, M. I. Natarajan, V. De Heyn, V. Vassilev, G. Groeseneken, A. J. Scholten, G. Badenes, M. Jurczak, S. Decoutere, S. Donnay and P. Wambacq, "Design-Driven Optimization of a 90 nm RF CMOS Process by use of Elevated Source/Drain", European Solid-State Device Research Conference, pp. 43-46, 2003.

- C14 T. Daenen, S. Thijs, M. I. Natarajan, V. Vassilev, V. De Heyn and G. Groeseneken, "Multilevel Transmission Line Pulse (MTLP) Tester", EOS/ESD Symposium, pp. 316-321, 2004.

- C15 D. Linten, S. Thijs, M. I. Natarajan, P. Wambacq, W. Jeamsaksiri, J. Ramos, A. Mercha, S. Jenei, S.Donnay and S. Decoutere, "A 5 GHz Fully Integrated ESD-Protected Low-Noise Amplifier in 90 nm RF CMOS", European Solid-State Circuits Conference, pp. 291-294, 2004.

- C16 D. Linten, S. Thijs, W. Jeamsaksiri, J. Ramos, A. Mercha, P. Wambacq, A. J. Scholten and S. Decoutere, "An integrated 5 GHz Low-Noise Amplifier with 5.5 kV HBM ESD protection in 90 nm RF CMOS", *IEEE Symposium on VLSI Circuits*, pp. 86-89, 2005.

- C17 D. Trémouilles, S. Thijs, Ph. Roussel, M. I. Natarajan, V. Vassilev and G. Groeseneken, "Transient Voltage Overshoot in TLP Testing - Real or Artifact?", EOS/ESD Symposium, pp. 152-160, 2005.

- C18 Ph. Jansen, S. Thijs, D. Linten, M. I. Natarajan, V. Vassilev, M. Liu, A. Concannon, D. Trémouilles, T. Nakaie, M. Sawada, V. A. Vashchenko, M. ter Beek, T. Hasebe, S. Decoutere and G. Groeseneken, "RF ESD Protection strategies The design and performance trade-off challenges", IEEE Custom Integrated Circuits Conference, pp. 489-496, 2005.

- C19 D. Linten, S. Thijs, J. Borremans, M. Dehan, D. Trémouilles, M. Scholz, M. I. Natarajan, P. Wambacq and G. Groeseneken, "T-Diodes - A Novel

- Plug-and-Play Wideband RF Circuit ESD Protection Methodology", *EOS/ESD Symposium*, pp. 242-249, 2007.

- C20 D. Linten, S. Thijs, J. Borremans, M. Dehan, D. Trémouilles, M. Scholz, M. I. Natarajan, P. Wambacq and G. Groeseneken, "T-Diodes A Novel Plug-and-Play Wideband RF Circuit ESD Protection Methodology", Reliability Center for Electronic Components of Japan Symposium, 2007.

- C21 D. Trémouilles, S. Thijs, C. Russ, J. Schneider, C. Duvvury, N. Collaert, D. Linten, M. Scholz, M. Jurczak, H. Gossner and G. Groeseneken, "Understanding the Optimization of Sub-45nm FinFET Devices for ESD Applications", EOS/ESD Symposium, pp. 408-415, 2007.

- C22 J. Borremans, S. Thijs, P. Wambacq, D. Linten, Y. Rolain, and M. Kuijk, "A 5 kV HBM Transformer-Based ESD Protected 5-6 GHz LNA", *IEEE Symposium on VLSI Circuits*, pp. 100-101, 2007.

- C23 M. Scholz, S. Thijs, D. Linten, D. Trémouilles, M. Sawada, T. Nakaie, T. Hasebe, M. I. Natarajan and G. Groeseneken, "Calibrated Wafer-Level HBM Measurements for Quasi-Static and Transient Device Analysis", EOS/ESD Symposium, pp. 89-94, 2007.

- C24 D. Linten, S. Thijs, M. Scholz, D. Trémouilles, M. Sawada, T. Nakaie, T. Hasebe and G. Groeseneken, "Characterization and Modeling of Diodes in Sub-45 nm CMOS Technologies under HBM Stress Conditions", EOS/ESD Symposium, pp. 158-164, 2007.

- C25 M. I. Natarajan, S. Thijs, D. Trémouilles, D. Linten, J. Loo, N. Collaert, M. Sawada, T. Hasebe, M. Jurczak, S. Decoutere and G. Groeseneken, "ESD protection for sub-45 nm MugFET Technology", 14th IEEE International Symposium on Physical and Failure Analysis, 2007.

- C26 G. Groeseneken, S. Thijs, D. Linten, M. Scholz, J. Borremans, N. Collaert and M. Jurczak, "Challenges and solutions for ESD protection in advanced logic and RF CMOS technologies", *International ESD Workshop*, 2008.

- C27 A. Griffoni, S. Thijs, C. Russ, D. Trémouilles, M. Scholz, D. Linten, N. Collaert, R. Rooyackers, C. Duvvury, H. Gossner, G. Meneghesso and G. Groeseneken, "Impact of Strain on ESD Robustness of FinFET Devices", IEEE International Electron Device Meeting, pp. 341-344, 2008.

- C28 A. Griffoni, S. Thijs, C. Russ, D. Trémouilles, D. Linten, M. Scholz, N. Collaert, L. Witters, G. Meneghesso and G. Groeseneken, "Next Generation FinFET Devices in Bulk Silicon Technology and Their Benefits for ESD Robustness", EOS/ESD Symposium, To be published, 2009.

- C29 D. Linten, S. Thijs, M. Okushima, J. Borremans, M. Scholz, M. Dehan and G. Groeseneken, "A 4.5 kV HBM, 300 V CDM ESD protected DC-to-16.1 GHz wideband LNA in 90 nm CMOS", EOS/ESD Symposium, To be published, 2009.

- C30 J. Borremans, S. Thijs, S. Decoutere and P. Wambacq, "Low-Cost Feedback-Enabled LNAs in 45nm CMOS", European Solid-State Circuits Conference, paper 3048, 2009.

- C31 A. Griffoni, S. Thijs, D. Linten, M. Scholz, G. Groeseneken and G. Meneghesso, "An Insight into the Parasitic Capacitances of SOI and Bulk FinFET Devices", *European Heterostructure Technology Workshop*, To be published, 2009.

- C32 A. Griffoni, S. Thijs, C. Russ, D. Trémouilles, D. Linten, M. Scholz, N. Collaert, L. Witters, G. Meneghesso and G. Groeseneken, "Next Generation FinFET Devices in Bulk Silicon Technology and Their Benefits for ESD Robustness", Reliability Center for Electronic Components of Japan Symposium, To be published, 2009.

#### Conference Contributions - Co-Author

- C33 V. Vassilev, M. Lorenzini, Ph. Jansen, V. A. Vashchenko, J. J. Yang, A. Concannon, D. Archer, G. Groeseneken, M. I. Natarajan, M. ter Beek, S. Thijs, B. J. Choi, M. Steyaert and H. E. Maes, "Snapback Circuit Model for Cascoded NMOS ESD Over-Voltage Protection Structures", European Solid-State Device Research Conference, pp. 561-564, 2003.

- C34 M. I. Natarajan, V. Vassilev, S. Thijs, V. De Heyn, T. Daenen and G. Groeseneken, "ESD Reliability Issues in Sub-Micron CMOS Trends and Challenges", 2nd MRS International Conference on Materials for Advanced Technologies & IUMRS, 2003.

- C35 W. Jeamsaksiri, A. Mercha, J. Ramos, D. Linten, S. Thijs, S. Jenei, C. Detcheverry, P. Wambacq, R. Velghe and S. Decoutere, "Integration of a 90nm RF CMOS Technology (200 GHz fmax 150 GHz fT NMOS) Demonstrated on a 5 GHz LNA", *IEEE Symposium on VLSI Technology*, pp. 100-101, 2004.

- C36 V. Vassilev, M. Lorenzini, Ph. Jansen, G. Groeseneken, S. Thijs, M. I. Natarajan, M. Steyaert and H. E. Maes, "Advanced Modeling and Parameter Extraction of the MOSFET ESD Breakdown Triggering in the 90nm CMOS Node Technologies", EOS/ESD Symposium, pp. 98-106, 2004.

- C37 J. Ramos, A. Mercha, W. Jeamsaksiri, D. Linten, S. Jenei, R. Rooyackers, R. Verbeeck, S. Thijs, A. J. Scholten, P. Wambacq, I. Debusschere and S. Decoutere "90nm RF CMOS Technology for Low-Power 900 MHz Applications", European Solid-State Device Research Conference, pp. 329-332, 2004.

- C38 M. I. Natarajan, V. Vassilev, S. Thijs and G. Groeseneken, "Modeling and Simulation for ESD Protection Circuit Design and Optimization", Proceedings International Conference on Semiconductor Electronics, pp. A12-A18, 2004.

- C39 D. Linten, L. Aspemeyr, W. Jeamsaksiri, J. Ramos, A. Mercha, S. Jenei, S. Thijs, R. Garcia, H. Jacobsson, P. Wambacq, S. Donnay and G. Groeseneken, "Low-Power 5 GHz LNA and VCO in 90 nm RF CMOS", IEEE Symposium on VLSI Circuits, pp. 372-375, 2004.

- C40 M. I. Natarajan, V. Vassilev, S. Thijs and G. Groeseneken, "ESD Protection Challenges in RFCMOS Circuits an Overview", *IEEE International Symposium on Microwaves*, 2004.

- C41 J. Ramos, W. Jeamsaksiri, A. Mercha, S. Thijs, D. Linten, P. Wambacq, B. De Jaeger, I. Debusschere, S. Biesemans and S. Decoutere "Hot-Carrier Degradation on the Analogue/RF Performances of a 90 nm RF-CMOS Technology Demonstrated in a 900 MHz Low-Power LNA", Proceedings IEEE VLSI-TSA International Symposium on VLSI Technology, pp. 64-65, 2005.

- C42 W. Jeamsaksiri, D. Linten, S. Thijs, G. Carchon, J. Ramos, A. Mercha, X. Sun, P. Soussan, M. Dehan, T. Chiarella, R. Venegas, V. Subramanian, A. J. Scholten, P. Wambacq, R. Velghe, G. Mannaert, N. Heylen, R. Verbeeck, W. Boullart, I. Heyvaert, M. I. Natarajan, G. Groeseneken, I. Debusschere, S. Biesemans and S. Decoutere, "A Low-Cost 90 nm RF-CMOS Platform for Record RF Circuit Performance", IEEE Symposium on VLSI Technology, pp. 60-61, 2005.

- C43 D. Linten, X. Sun, S. Thijs, M. I. Natarajan, A. Mercha, G. Carchon, P. Wambacq, T. Nakaie and S. Decoutere, "Low-Power Low-Noise Highly ESD Robust LNA and VCO Design Using Above IC Inductors", *IEEE*

- C44 M. I. Natarajan, D. Linten, S. Thijs, Ph. Jansen, D. Trémouilles, W. Jeamsaksiri, T. Nakaie, M. Sawada, T. Hasebe, S. Decoutere and G. Groeseneken, "RFCMOS ESD Protection and Reliability", 12th IEEE International Symposium on Physical and Failure Analysis, 2005.

- C45 D. Linten, M. I. Natarajan, S. Thijs, S. Van Huylenbroeck, S. Xiao, G. Carchon, S. Decoutere, M. Sawada, T. Hasebe and G. Groeseneken, "Implementation of 6 kV ESD Protection for a 17 GHz LNA in 130nm SiGeC BiCMOS", IEEE International Conference on Semiconductor Electronics, pp. A7-A12, 2006.

- C46 V. A. Vashchenko, Ph. Jansen, M. Scholz, P. Hopper, M. Sawada, T. Nakaei, T. Hasebe and S. Thijs, "Voltage Overshoot Study in 20V DeMOS-SCR Devices", EOS/ESD Symposium, pp. 53-57, 2007.

- C47 P. Wambacq, A. Mercha, K. Scheir, B. Verbruggen, J. Borremans, V. De Heyn, S. Thijs, D. Linten, G. Van der Plas, B. Parvais, M. Dehan, S. Decoutere, C. Soens, N. Collaert and M. Jurczak, "Advanced Planar Bulk and Multigate CMOS Technology: Analog Circuit Benchmarking up to mm-wave Frequencies", *IEEE International Solid-State Circuits Conference*, pp. 528-533, 2008.

- C48 G. Groeseneken, F. Crupi, A. Shickova, S. Thijs, D. Linten, B. Kaczer, N. Collaert, M. Jurczak, "Reliability Issues in MugFET Nanodevices", *IEEE International Reliability Physics Symposium*, 2008.

- C49 D. Linten, V. Vashchenko, M. Scholz, P. Jansen, D. Lafonteese, S. Thijs, M. Sawada, T. Hasebe, P. Hopper, and G. Groeseneken, "Analysis of High Voltage ESD Protection Devices under HBM ESD stress", *International ESD Workshop*, 2008.

- C50 S. Sangameswaran, J. De Coster, D. Linten, M. Scholz, S. Thijs, L. Haspeslagh, A. Witvrouw, C. Van Hoof, G. Groeseneken and I. De Wolf, "ESD Issues in MEMS: A case study in Micromirrors", *International ESD Workshop*, 2008.

- C51 D. Linten, V. Vashchenko, M. Scholz, P. Jansen, D. Lafonteese, S. Thijs, M. Sawada, T. Hasebe, P. Hopper, and G. Groeseneken, "Extreme Voltage and Current Overshoots in HV Snapback Devices during HBM ESD stress", EOS/ESD Symposium, pp. 204-210, 2008.

- C52 S. Sangameswaran, J. De Coster, D. Linten, M. Scholz, S. Thijs, L. Haspeslagh, A. Witvrouw, C. Van Hoof, G. Groeseneken and I. De Wolf, "ESD Reliability issues in Microelectromechanical Systems (MEMS): A case study in micromirrors", EOS/ESD Symposium, pp. 249-257, 2008.

- C53 J. Borremans, B. Parvais, M. Dehan, S. Thijs, P. Wambacq, A. Mercha, M. Kuijk, G. Carchon and S. Decoutere, "Perspective of RF design in future planar and FinFET CMOS", IEEE Radio Frequency Integrated Circuits Symposium, pp. 75-78, 2008.

- C54 M. Scholz, D. Linten, S. Thijs, M. Sawada, T. Nakaei, T. Hasebe and G. Groeseneken, "On-wafer Human Metal Model System-level ESD Stress on Component Level", *Reliability Center for Electronic Components of Japan Symposium*, 2008.

- C55 K. Raczkowski, S. Thijs, W. De Raedt, B. Nauwelaers and P. Wambacq, "50-67 GHz ESD Protected Power Amplifiers in Digital 45 nm LP CMOS", *International Solid-State Circuits Conference*, paper 22.5, 2009.

- C56 M. Scholz, D. Linten, S. Thijs, M. Sawada, T. Nakaei, T. Hasebe, D. Lafonteese, V. Vashchenko, G. Vandersteen, G. Groeseneken, "Onwafer Human Metal Model measurements for System-level ESD analysis", EOS/ESD Symposium, To be published, 2009.

- C57 D. LaFonteese, V. Vashchenko, D. Linten, M. Scholz, S. Thijs, A. Kozyrev, M. Sawada, T. Nakaei, T. Hasebe, P. Hopper and G. Groeseneken, "Self-Protection Capability of Power Arrays", EOS/ESD Symposium, To be published, 2009.

- C58 S. Sangameswaran, J. Coster, M. Scholz, D. Linten, S. Thijs, C. Van Hoof, I. De Wolf and G. Groeseneken, "A Study of Breakdown Mechanisms in Electrostatic Actuators using Mechanical Response under EOS-ESD Stress", EOS/ESD Symposium, To be published, 2009.

- C59 D. Linten, P. Roussel, M. Scholz, S. Thijs, A. Griffoni, M. Sawada, T. Hasebe and G. Groeseneken, "Calibration of Very Fast TLP Transients", EOS/ESD Symposium, To be published, 2009.

- C60 D. Linten, P. Roussel, M. Scholz, S. Thijs, A. Griffoni, M. Sawada, T. Hasebe and G. Groeseneken, "Calibration of Very Fast TLP Transients", Reliability Center for Electronic Components of Japan Symposium, To be published, 2009.

C61 M. Scholz, D. Linten, S. Thijs, M. Sawada, T. Nakaei, T. Hasebe, D. Lafonteese, V. Vashchenko, G. Vandersteen, G. Groeseneken, "Onwafer Human Metal Model measurements for System-level ESD analysis", Reliability Center for Electronic Components of Japan Symposium, To be published, 2009.

#### Workshops and Tutorials

- W1 J. Ramos, A. Mercha, W. Jeamsaksiri, D. Linten, S. Jenei, S. Thijs, A. J. Scholten, P. Wambacq, I. Debusschere and S. Decoutere, "RF CMOS Modeling for Circuit Design", Microwave Device Modeling & Design of Microwave Systems, 2004.

- W2 J. Ramos, A. Mercha, W. Jeamsaksiri, D. Linten, S. Jenei, S. Thijs, A. J. Scholten, P. Wambacq, I. Debusschere and S. Decoutere, "A 90 nm RF CMOS Technology Supported by Device Modeling and Circuit Demonstrators", MOS-AK/ESSCIRC Workshop, 2004.

- **T1** D. Linten, **S. Thijs**, M. Scholz, D. Trémouilles, M. I. Natarajan and G. Groeseneken, "Technology-Aware ESD-Reliable RF CMOS Circuit Design", *IEEE Custom Integrated Circuits Conference Tutorial*, 2006.

- **T2** D. Linten, **S. Thijs** and M. I. Natarajan, "ESD Protection for Wideband RFCMOS Circuits Challenges, Options and Trade-offs", *IEEE Radio Frequency Integrated Circuits Symposium Tutorial*, 2006.

- W3 S. Thijs, "RF ESD Protection Trends and Outlook", Reliability Center for Electronic Components of Japan Symposium Workshop, 2006.

- **T3** M. I. Natarajan, D. Linten, **S. Thijs** and G. Groeseneken, "ESD Protection for Semiconductor Devices", *IEEE International Symposium on Physical and Failure Analysis Tutorial*, 2007.

- W4 S. Thijs and D. Linten, "Protecting High Frequency Circuits", EOS/ESD Symposium Workshop, 2007.

- W5 D. Linten, S. Thijs and M. Scholz, "Exploring ESD Protection in Sub-32 nm CMOS Technology", Reliability Center for Electronic Components of Japan Workshop, 2007.

- **T4** D. Linten and **S. Thijs**, "Advanced RF Implementation Flow Course Electrostatic discharge (ESD) protection", *IDESA Implementation of Widespread IC Design Skills in Advanced deep Submicron Technologies at European Academia*, 2008-2009.

#### **Patents**

**P1 S. Thijs**, N. M. Iyer, V. Vassilev, T. Daenen and V. De Heyn, "Method of Determing Current-Voltage Characteristics of a Device", *United States Patent*, US 7,181,352, 2004.

#### Patent Applications

- **P2 S. Thijs**, N. M. Iyer, V. Vassilev, T. Daenen and V. De Heyn, "Method of Determing Current-Voltage Characteristics of a Device", *European Patent Application*, EP 1,480,046,A1, 2003.

- P3 S. Thijs, N. M. Iyer and D. Linten, "Electrostatic Discharge Protected Circuits", United States Patent Application Publication, US 2007/0058308.

- **P4 S. Thijs** and D. Trémouilles, "Fast Triggering ESD Protection Device and Method for Designing Same", *United States Patent Application Publication*, US 2009/0073621, A1.

- **P5 S. Thijs** and D. Trémouilles, "Fast Triggering ESD Protection Device and Method for Designing Same", *European Patent Application*, EP 2037501, A1, 2007.

- P6 S. Thijs, D. Trémouilles and C. Russ, "Electronic Circuit and Method of Manufacturing an Electronic Circuit", *United States Patent Application Publication*, US 2009/0065868, A1.

- **P7 S. Thijs**, M. Scholz, D. Trémouilles and D. Linten, "Method for Calibrating an Electrostatic Discharge Tester", *United States Patent Application Publication*, US 0027063A1, 2009.

- **P8 S. Thijs**, M. Scholz, D. Trémouilles and D. Linten, "Method for Calibrating an Electrostatic Discharge Tester", *European Patent Application*, EP 1972953 A1, 2008.

- **P9 S. Thijs**, D. Trémouilles and D. Linten, "ESD design methodology for ESD protection devices in FinFET technology", *European Patent Application*, EP 09159669.2, 2009.

#### **Patent Submissions**

**P10 S. Thijs** and D. Trémouilles, "Field Effect Diode (FED) in FinFET technology"

- **P11 S. Thijs** and D. Trémouilles, "Silicon Controlled Rectifier (SCR) in FinFET technology"

- **P12 S. Thijs**, D. Linten and D. Trémouilles, "Bidirectional ESD power clamp for SOI CMOS technologies (e.g. FinFET)"

- **P13 S. Thijs**, D. Linten and D. Trémouilles, "Keep-off circuit for ESD protection devices"

- P14 S. Thijs and D. Linten, "Center Balanced Distributed ESD protection"

- P15 S. Thijs and D. Linten, "Turn Off of parasitic path in core circuit"

# Nederlandstalige Samenvatting

### ESD Bescherming voor Meervoudige Gate Veld Effect Structuren en voor RF CMOS Circuits

#### Inleiding

Twee grote uitdagingen liggen in het verschiet voor de ESD ontwerpingenieur. Is ESD enerzijds een spelbreker voor de introductie van FinFET technologie door het geringe silicium volume van de structuren? Is anderzijds een goede ESD bescherming compatibel met de strenge vereisten voor RF circuits met steeds hoger wordende RF frequenties? Voor deze laatste uitdaging zijn zowel oplossingen nodig voor smalbandige als breedbandige RF toepassingen. Ook moet er meer aandacht besteed worden aan CDM bescherming ten opzichte van HBM, omdat dit type ESD stress meer kritisch is en er moeilijker tegen te beschermen valt. Om deze twee uitdagingen goed aan te kunnen gaan, moeten eerst de beperkingen van de huidige meetsystemen worden weggewerkt.

#### ESD Karakterisatie en Analyze Technieken

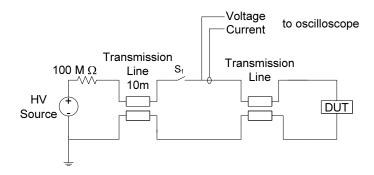

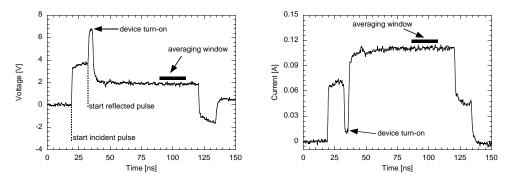

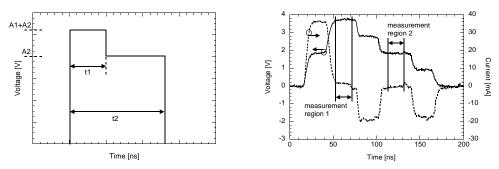

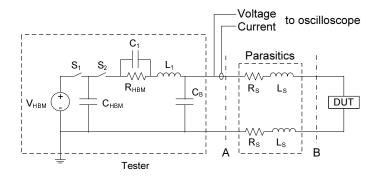

In deze thesis werden er drie nieuwe ESD karakterisatie en analyze technieken ontworpen die de bestaande technieken en meetsystemen verder uitbreiden. Eerst hebben we een Multi-Level Transmissie Lijn Puls (MTLP) meetsysteem ontworpen. Vervolgens hebben we een transient analyze uitgevoerd op ESD protectiestructuren door gebruik te maken van de spannings- en stroomgolfvormen verkregen tijdens een klassieke TLP meting. Als laatste hebben we een Human Body Model-IV (HBM-IV) curve verkregen door de transient spannings- en stroomgolfvormen van een HBM meting te combineren.

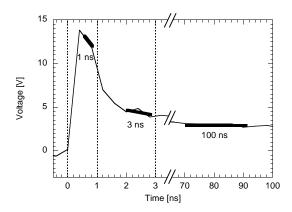

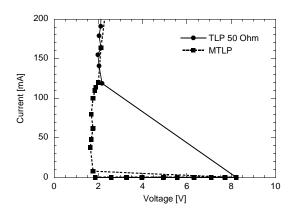

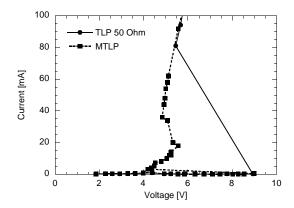

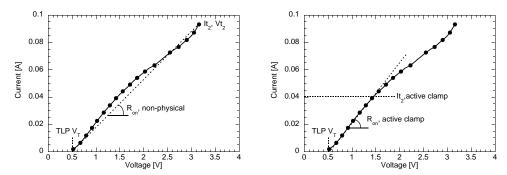

Door MTLP te gebruiken kan een TLP-IV curve gegenereerd worden die niet beperkt is door de impedantie van het meetsysteem, typisch 50  $\Omega$ . Eerst wordt de te onderzoeken structuur aangeschakeld door een puls aan te leggen

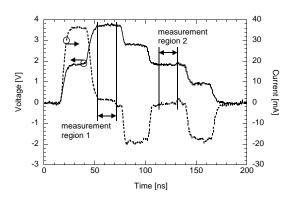

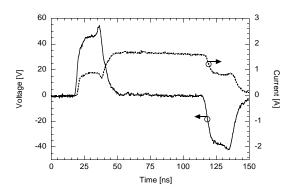

Figuur 0.1: Resulterende spannings en stroom golfvormen tijdens een MTLP meting op een open belasting.

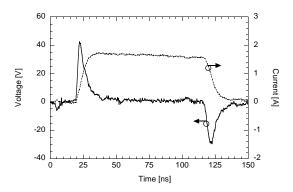

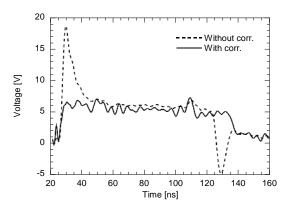

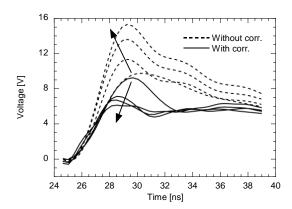

Figuur 0.2: Ruwe en gekalibreerde spannings golfvorm voor een ggNMOS transistor in een 90 nm CMOS technologie tijdens een 500 mA TLP stroom puls.

met voldoende grote amplitude. Na het aanschakelen wordt de amplitude van de puls verlaagd zonder deze af te schakelen, zodat de structuur vanuit aangeschakelde toestand naar een toestand met lage stroom wordt gebracht en bijgevolg niet beperkt is door de systeemimpedantie. Een voorbeeld van een resulterende spannings en stroom golfvorm tijdens dergelijke MTLP meting op een open belasting wordt getoond in Fig. 0.1.

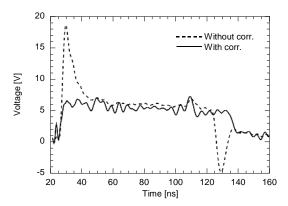

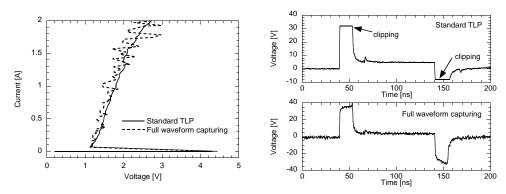

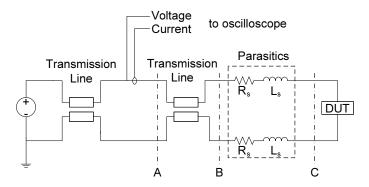

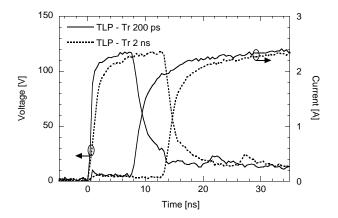

Uit de spannings- en stroomgolfvormen die verkregen worden tijdens een TLP meting kan naast de quasi-statische TLP-IV curve ook informatie verkregen worden over het transient schakelgedrag van de structuur door het tijdsgedrag van de golfvormen te analyzeren. Het is hiervoor belangrijk dat de oscilloscoop zodanig ingesteld is dat de volledige golfvormen opgemeten kunnen worden zonder tegen de limieten van het instelbereik van de oscilloscoop aan te lopen. Verder is het noodzakelijk om de parasitaire elementen van het meetsysteem

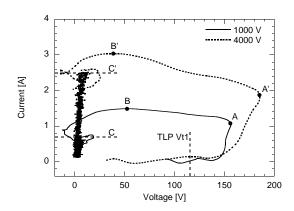

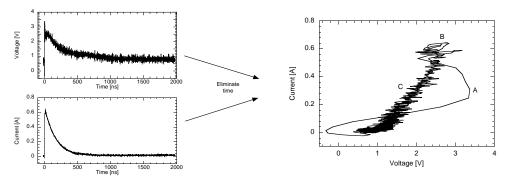

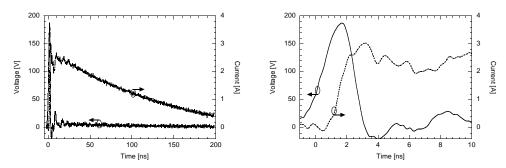

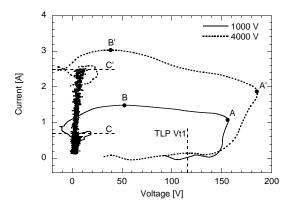

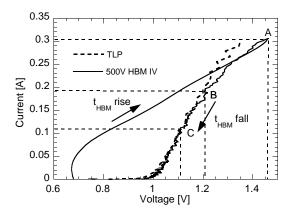

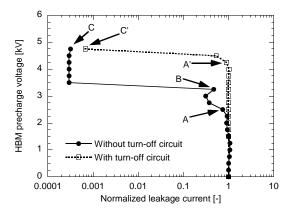

Figuur 0.3: HBM-IV curve gegenereerd uit spannings en stroom golfvormen van een VDMOS SCR structuur, voor 1000 V en 4000 V HBM stress niveau's. Punt A toont een spanningspiek aan, punt B een stroompiek en punt C toont het verwachte stroomniveau gebaseerd op de HBM spanning.

op te meten en een nauwkeurige kalibratie uit te voeren om de invloed ervan te verwijderen. Op die manier wordt het transient schakelgedrag van de te onderzoeken structuur bekomen. Een voorbeeld hiervan wordt getoond op een ggNMOS transistor in Fig. 0.2 waar een spanningspiek opgemeten wordt zonder kalibratie en die volledig verdwenen is na de kalibratie. Er treedt bijgevolg bij het aanschakelen van dergelijke ggNMOS transistor geen spanningspiek op.

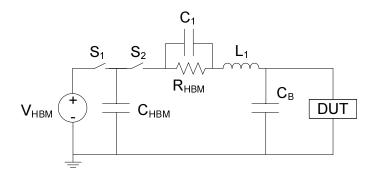

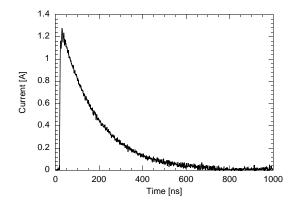

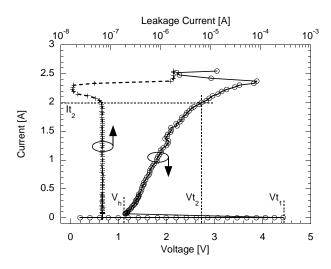

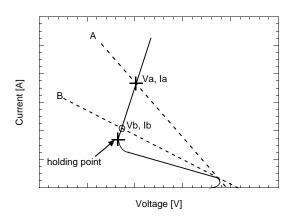

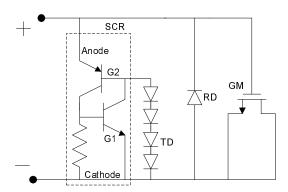

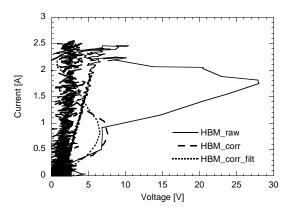

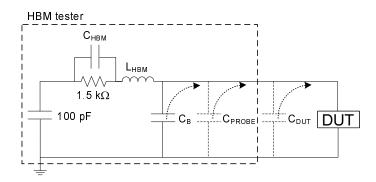

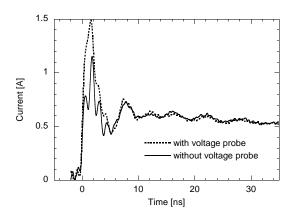

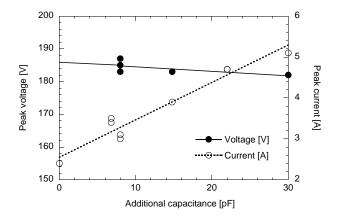

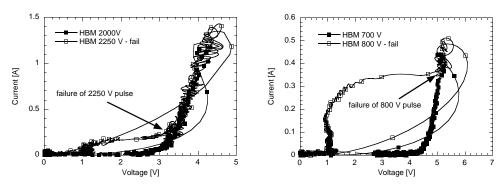

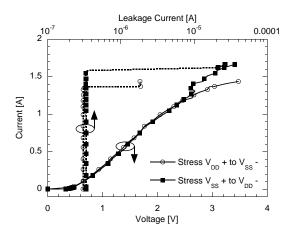

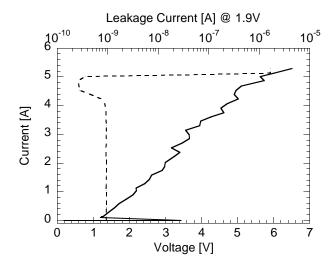

Vanuit de opgemeten spannings en stroom golfvormen tijdens een HBM meting op een ESD structuur kan een HBM-IV curve gegenereerd worden door eliminatie van de tijd. Naast dezelfde quasi-statische parameters die ook met TLP bekomen worden, kunnen nog een aantal bijzondere effecten opgemeten worden die ontstaan uit de interactie tussen de structuur en de HBM tester. Deze effecten zijn uniek voor de HBM meting en kunnen niet met TLP bekomen worden. Het is ook belangrijk om op te merken dat de impedantie van de HBM tester, met name  $1.5~\mathrm{k}\Omega$ , een grote rol speelt in deze interactie. Bijgevolg zullen  $50~\Omega$  implementaties van een HBM tester tot foutieve resultaten leiden. Een voorbeeld van een  $1000~\mathrm{V}$  en  $4000~\mathrm{V}$  HBM-IV curve voor een VDMOS SCR structuur wordt getoond in Fig. 0.3. Er is duidelijk een spanningspiek zichtbaar bovenop de quasi-statische TLP trigger spanning  $Vt_1$ , en een stroompiek bovenop het verwachte stroomniveau gebaseerd op de HBM spanning. Deze spannings- en stroompieken kunnen aan de basis liggen voor miscorrelatie tussen HBM en TLP resultaten.

#### ESD Bescherming in FinFET Technologie

Volgens de Internationale Technologie Roadmap voor Halfgeleiders (ITRS) 2007, zal de fysieke gate lengte van een transistor 9 nm bereiken in 2016. Het gebruik van bulk CMOS zal dan beperkt worden door een aantal korte-

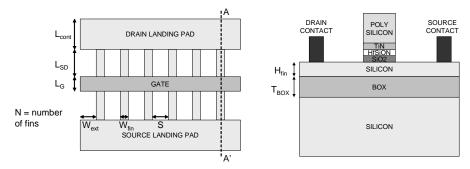

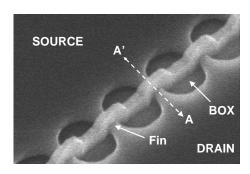

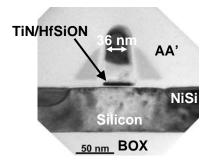

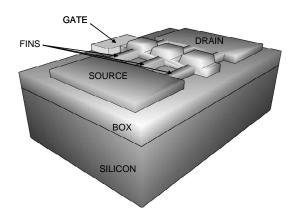

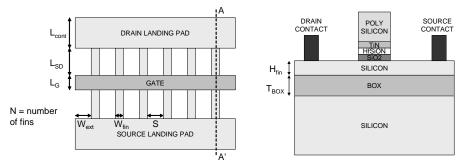

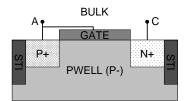

Figuur 0.4: Vereenvoudigd horizontaal zicht (links) en vertikale doorsnede volgens de snede A-A' (rechts) van een FinFET structuur met aanduiding van de belangrijkste geometrische parameters (niet op schaal).

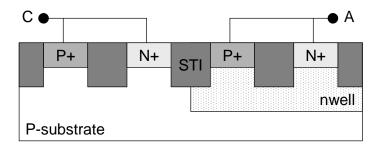

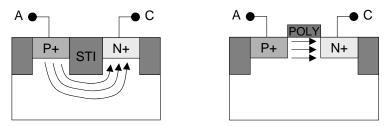

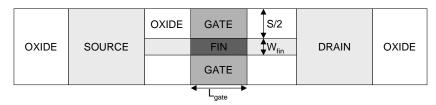

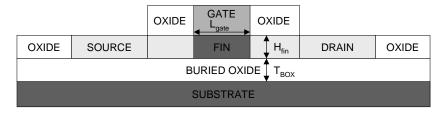

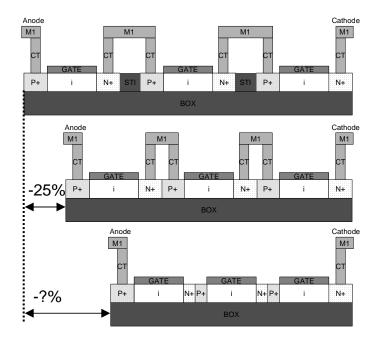

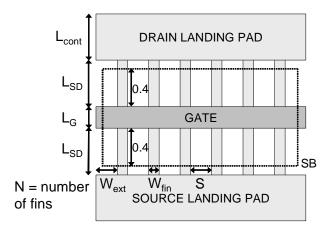

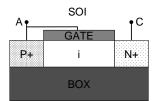

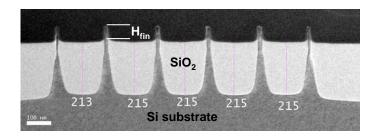

kanaaleffecten, die gepaard gaan met transistor schaling. Om deze barrière te overwinnen, worden er nieuwe structuren ontwikkeld, waarbij de meervoudige gate structuren de meest veelbelovende resultaten geven. Een FinFET is een dergelijke meervoudige gate structuur met heel goede controle over de korte-kanaaleffecten en waarvan de processing compatibel is met standaard CMOS processing. Fig. 0.4 toont een horizontaal bovenaanzicht (links) en een vertikale doorsnede (rechts) van een FinFET structuur, met aanduiding van de belangrijkste geometrische parameters. De structuur is opgebouwd uit parallelle silicium 'vinnen' ('fins') waarvan het kanaal aan de zijkanten en de bovenkant gecontroleerd wordt door de gate.

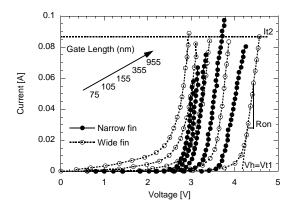

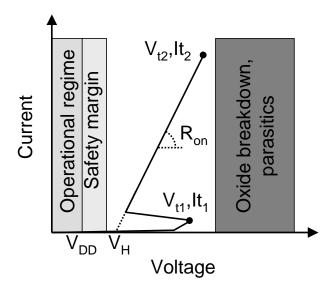

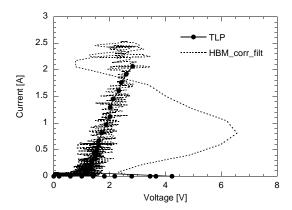

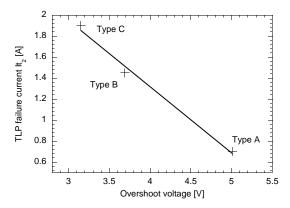

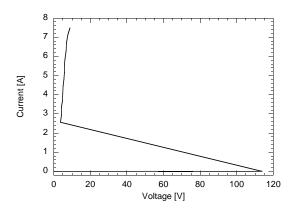

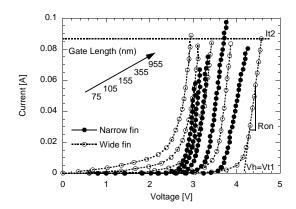

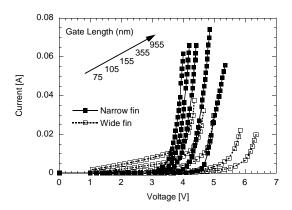

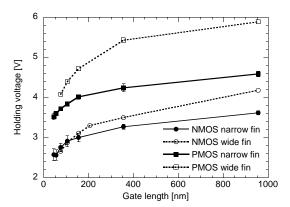

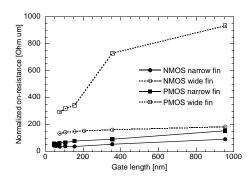

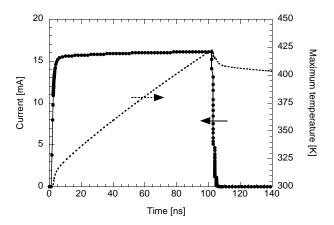

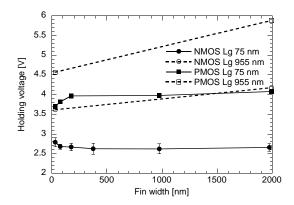

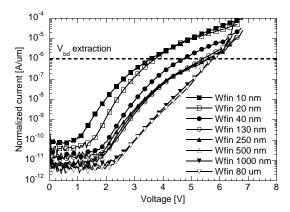

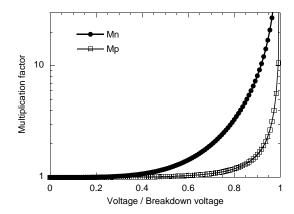

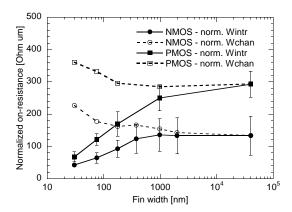

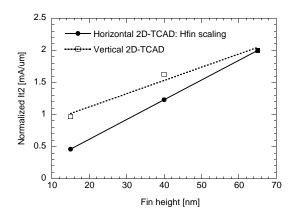

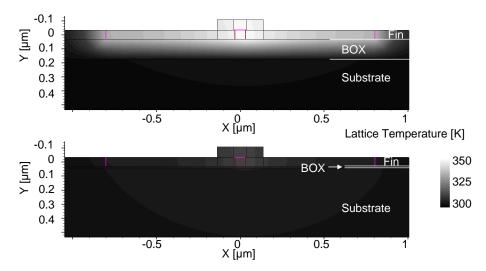

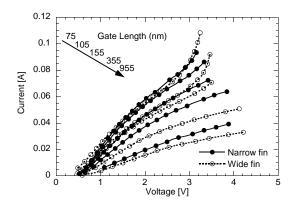

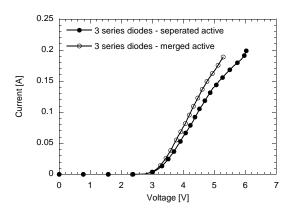

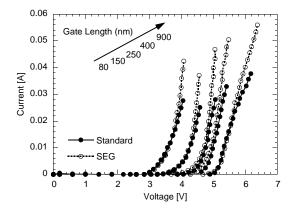

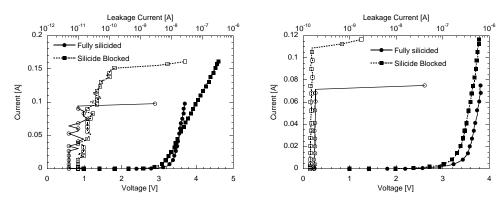

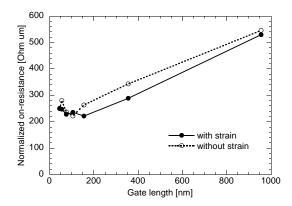

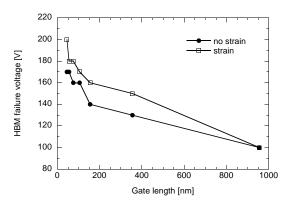

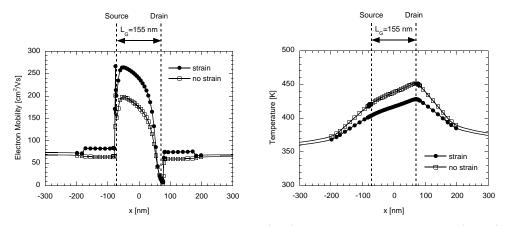

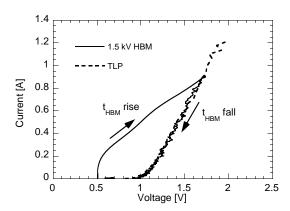

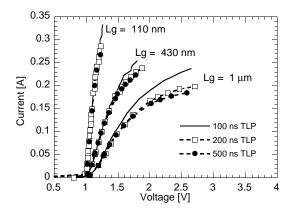

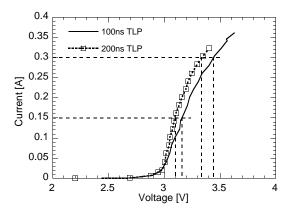

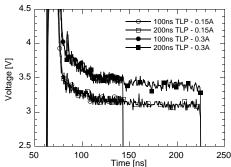

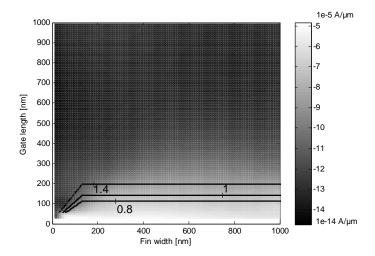

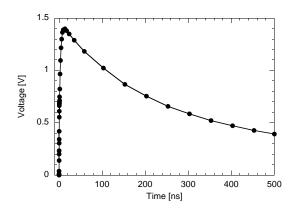

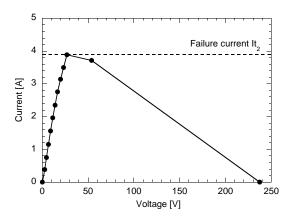

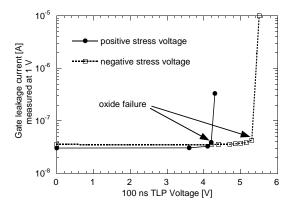

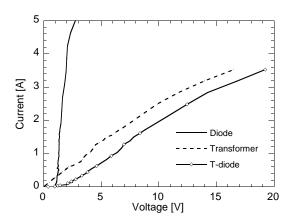

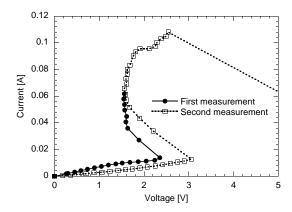

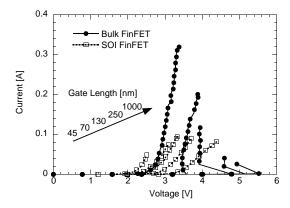

Fig. 0.5 toont een set van TLP metingen op een N-type FinFET in bipolaire mode voor zowel structuren met smalle als met brede fins. Door de SOI-technologie is de basis van de bipolaire structuur vlottend, zodat er geen typische 'snapback' karakteristiek in de TLP-IV curve waargenomen wordt. De structuren gaan zonder spanningsterugval over naar de bipolaire werkingsmodus wanneer hun houdspanning  $V_h$  bereikt wordt. De faalstroom  $It_2$  is sterk afhankelijk van de verschillende geometrische parameters.

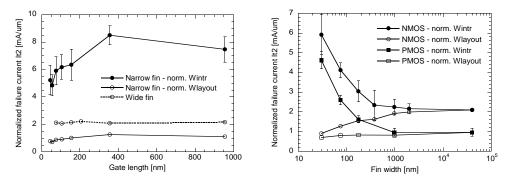

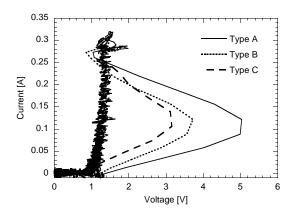

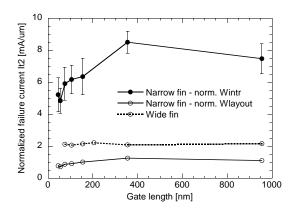

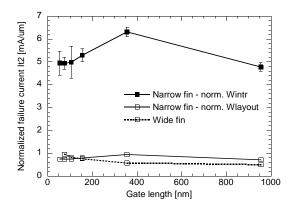

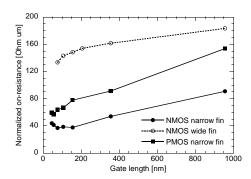

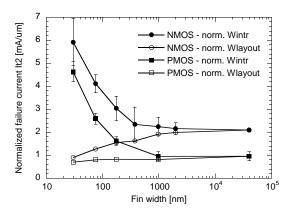

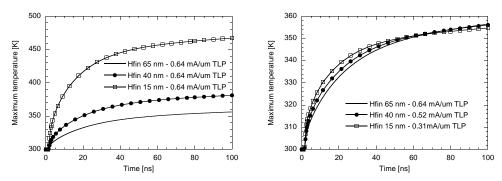

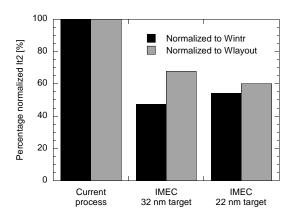

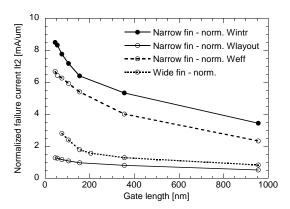

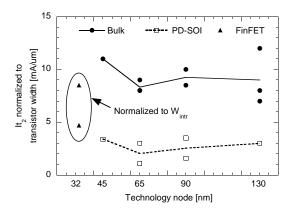

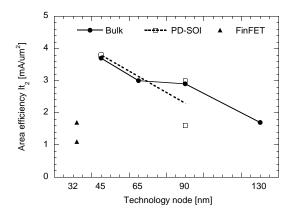

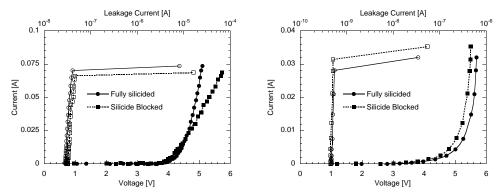

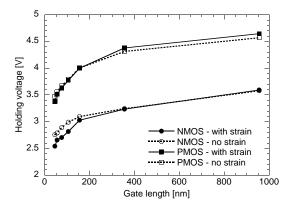

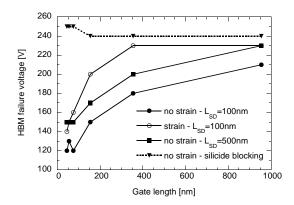

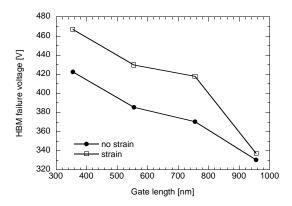

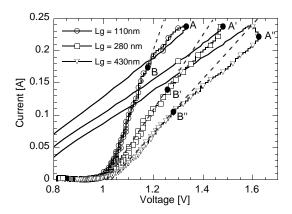

In Fig. 0.6 wordt  $It_2$  getoond als functie van gate lengte (links) en fin breedte (rechts). Voor N-type structuren met smalle fins is er een verbetering merkbaar in  $It_2$  bij grotere gate lengte door een meer uniforme faling tussen de verschillende fins. Deze verbetering is zichtbaar voor de twee gebruikte normalizaties. De intrinsieke performantie wordt geanalyzeerd door te normalizeren ten opzichte van  $W_{intr}$  die de effectieve silicium breedte aanduidt, en de layout efficiëntie ten opzichte van  $W_{layout}$  die de totaal gebruikte layout breedte weergeeft. Wanneer de gate lengte echter te groot wordt, wordt het gedissipeerde vermogen te groot, zodat  $It_2$  terug daalt. Voor brede fin structuren is er geen afhankelijkheid van  $It_2$  ten opzichte van de gate lengte.

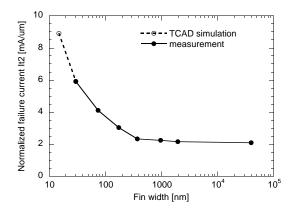

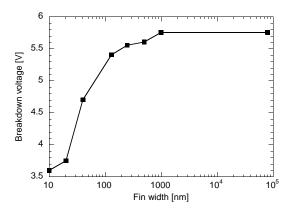

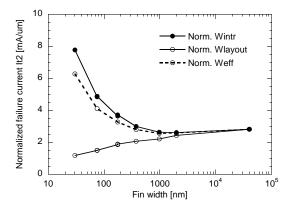

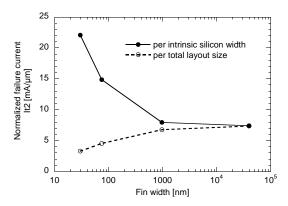

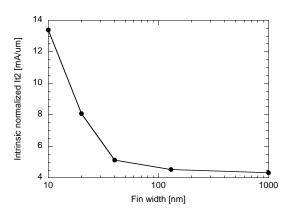

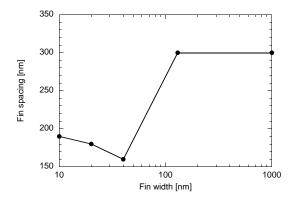

Wanneer de afhankelijkheid van  $It_2$  ten opzichte van  $W_{fin}$  bekeken wordt in

Figuur 0.5: TLP-IV curves voor N-type FinFET in bipolaire mode met verschillende gate lengtes voor zowel smalle (400 fins van 30 nm  $W_{fin}$ ) als brede (enkelvoudige 40  $\mu$ m) structuren.

Figuur 0.6: Genormalizeerde faalstroom  $It_2$  als functie van de gate lengte voor smalle en brede fin N-type FinFET structuren in bipolaire mode (links). Genormalizeerde  $It_2$  als functie van de fin breedte voor FinFET structuren met 75 nm gate lengte in bipolaire mode (rechts).

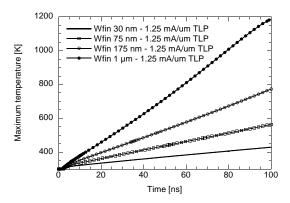

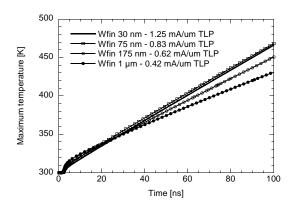

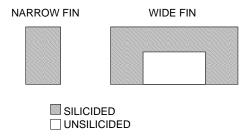

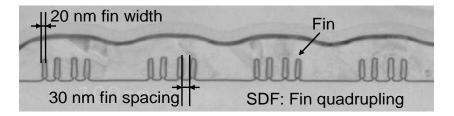

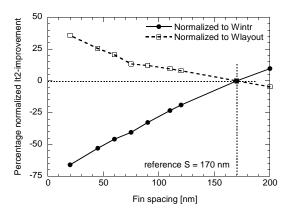

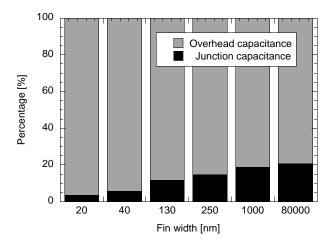

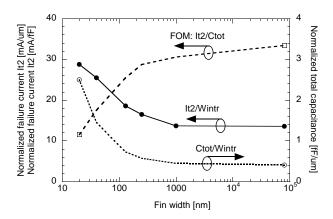

Fig. 0.6 (rechts), is er een duidelijk verschillende trend merkbaar afhankelijk van welke normalizatie gehanteerd wordt. Zowel voor NMOS als PMOS structuren stijgt de intrinsieke  $It_2$  wanneer de fin breedte  $W_{fin}$  vermindert. Deze verbetering is te verklaren door een betere koeling van smalle fins, in vergelijking met brede fins. Aan de andere kant verslechtert de layout efficientie van  $It_2$  bij smallere  $W_{fin}$ , doordat de fin-spacing S overhead een steeds groter deel van de layout oppervlakte in beslag neemt (Fig. 0.4).

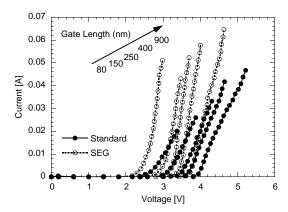

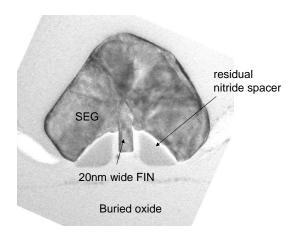

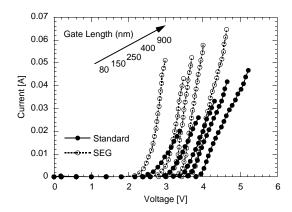

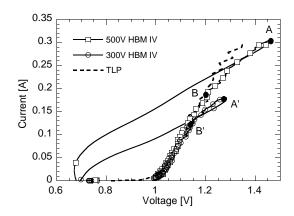

Selective Epitaxial Growth (SEG) is standaard nodig om de toegangsweerstand van de FinFET transistoren te verminderen. Door hiervan gebruik te maken wordt het siliciumvolume van de source en drain landing pads vergroot, alsook het volume van het gedeelte van de fins tussen de landing pads en de gate, zie Fig. 0.4. Dit resulteert in ongeveer een verdubbeling van  $It_2$ , die gepaard gaat

Figuur 0.7: TLP-IV curves van N-type FinFET structuren in bipolaire mode als functie van gate lengte voor wafers geprocessed met en zonder SEG. De structuren hebben een fin breedte van 25 nm en 225 fins in parallel.

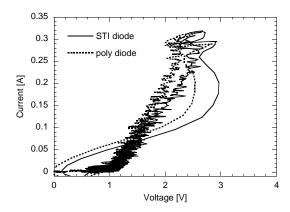

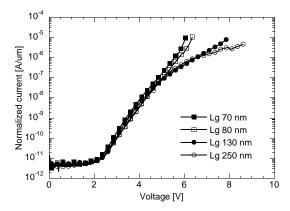

met een drastische vermindering van de aan-weerstand  $R_{on}$ , zoals te zien is in de TLP-IV curves van NMOS FinFET transistoren in bipolaire mode in Fig. 0.7.

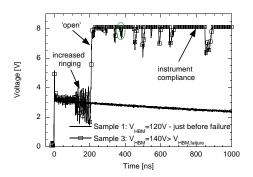

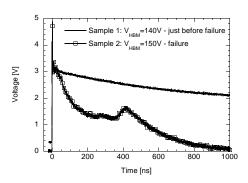

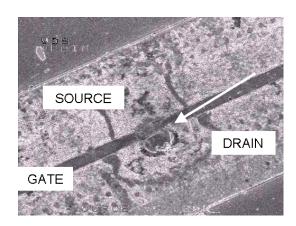

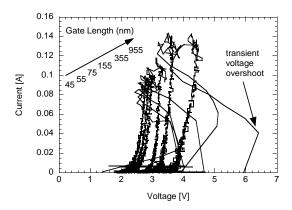

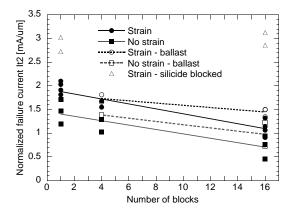

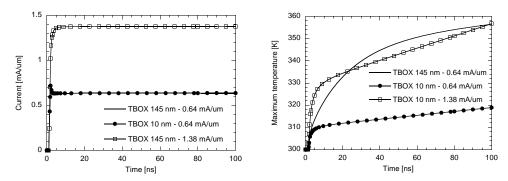

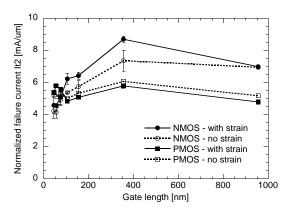

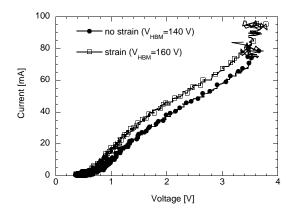

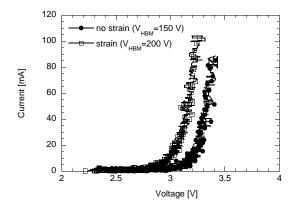

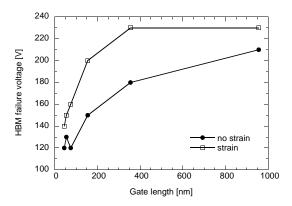

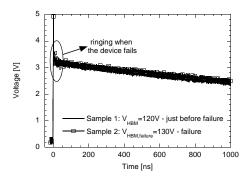

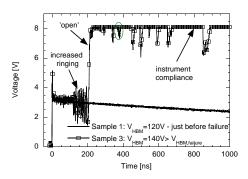

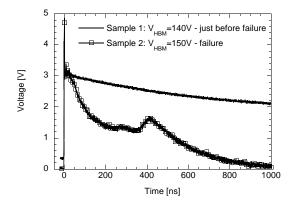

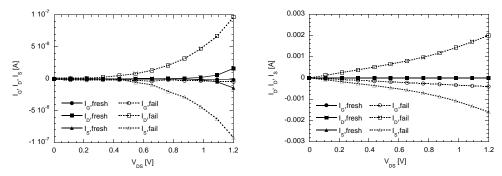

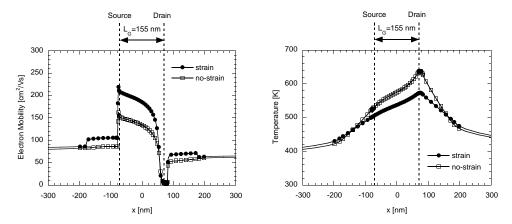

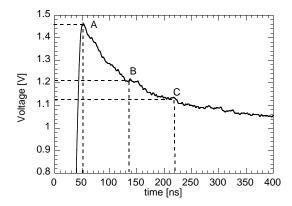

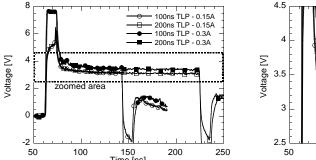

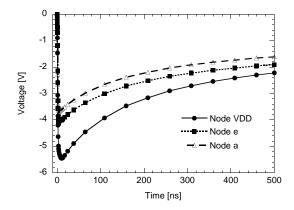

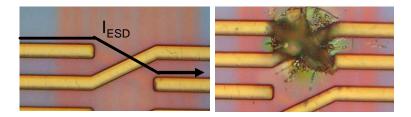

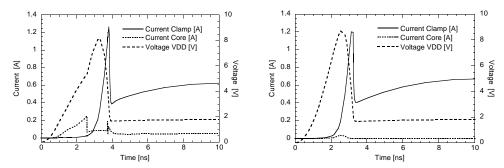

Ook het gebruik van stress om de mobiliteit van de transistoren te verbeteren heeft een meetbare invloed op het ESD gedrag van de FinFET transistoren. In Fig. 0.8 worden de HBM spanningsgolven vlak voor en na faling weergegeven voor transistoren in bipolaire mode zonder stress (links) en met stress (rechts). Zonder stress is er bij faling eerst een oscillatie meetbaar op de spanningsgolfvorm, todat deze divergeert naar een hoog-resistieve 'open' conditie. Deze spanningsoscillaties duiden op een hoge instabiliteit rond het falingsstroomniveau. Bij faling van een groepje fins zal eerst de spanning dalen doordat er lokaal een kortsluiting tussen source en drain gevormd wordt. Omdat het aantal fins bij faling eerder beperkt is, zal de hoge stroom die vervolgens door deze kortgesloten fins vloeit, deze fins opblazen, zodat ze 'open' worden. Hierdoor zal de spanning terug stijgen. Vervolgens faalt het volgende groepje fins (oscillaties), totdat uiteindelijk alle fins 'open' zijn. Bij het gebruik van stress faalt de structuur op een hoger HBM stress niveau, en ook het falingsmechanisme is anders. Bij faling daalt de spanning tot een 'kortsluiting' doordat er meer fins tegelijkertijd falen.

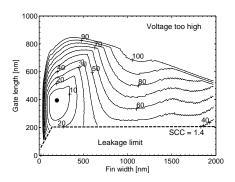

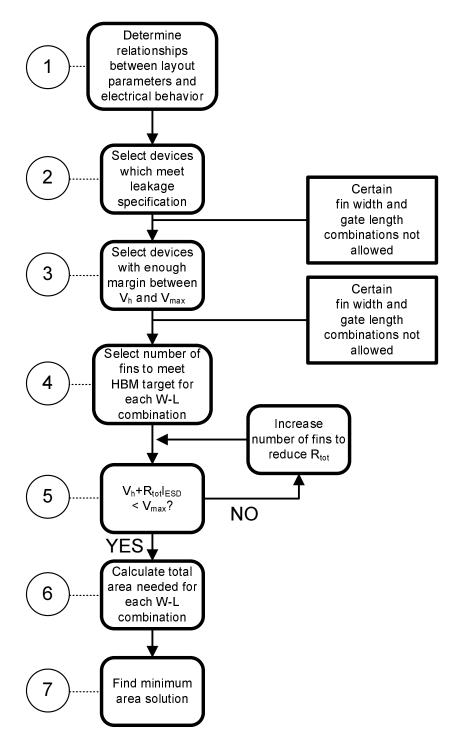

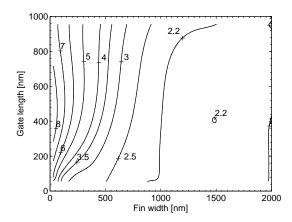

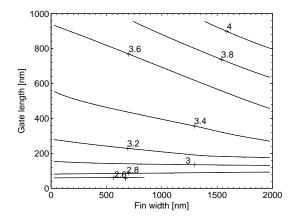

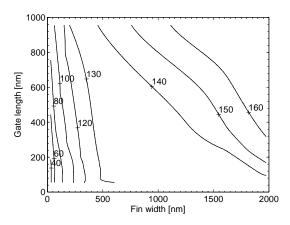

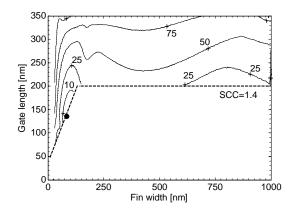

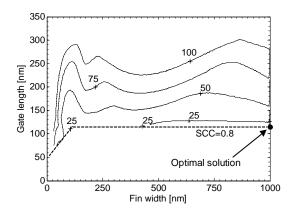

Door de complexe afhankelijkheid van de verschillende ESD performantie parameters (lekstroom, houdspanning, aan-weerstand en faalstroom) van de geometrische en process parameters is het nodig om gebruik te maken van een ontwerpmethodologie om een optimale ESD oplossing te bekomen die rekening houdt met de verschillende randvoorwaarden. Deze ontwerpmethodologie gebruikt de geëxtraheerde ESD performantie parameters uit de beschikbare meetdata als input. Door middel van lineaire interpolatie kunnen de ESD

Figuur 0.8: HBM-spanningsgolfvorm voor en tijdens faling van een FinFET structuur zonder stress (links) en met stress (rechts) in bipolaire mode met 75 nm gate lengte. Wanneer de structuur zonder stress faalt, groeit eerst de oscillatie op de spanningsgolfvorm totdat ze divergeert naar een hoog-resisitieve 'open' conditie (links). Wanneer de structuur met stress faalt daalt de spanning naar een 'kortsluiting' (rechts).

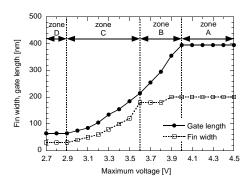

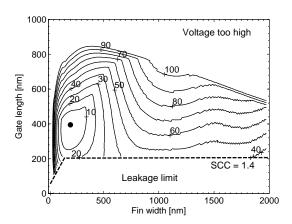

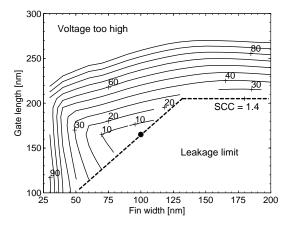

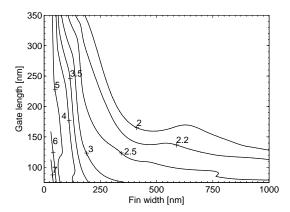

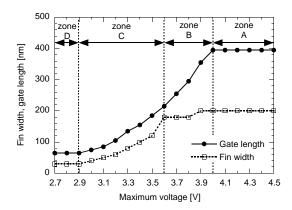

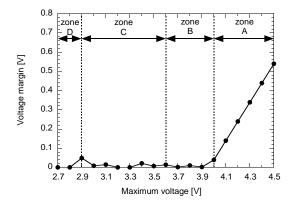

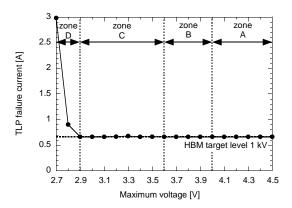

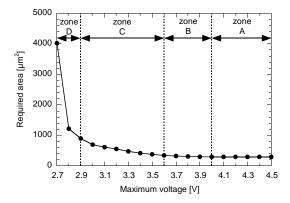

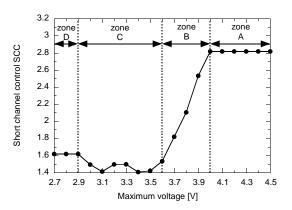

Figuur 0.9: Percentage van vergrootte oppervlakte vergeleken met de optimale oplossing (punt) dat voldoet aan de opgelegde ontwerp limieten van 1 kV HBM, 4 V  $V_{max}$  en zeer goede controle over de korte-kanaaleffecten (SCC>1.4) in bipolaire mode (links). Afhankelijkheid van de optimale  $L_g$  en  $W_{fin}$  als functie van  $V_{max}$  (rechts).

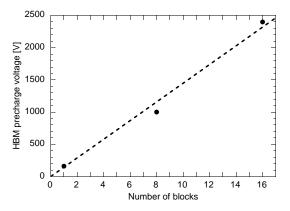

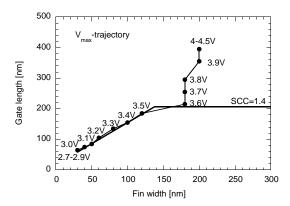

performantie parameters bepaald worden voor de verschillende geometrische en process parameters. Op basis van een wiskundige algoritme kan de optimale oplossing vervolgens bepaald worden. Fig. 0.9 toont links de ideale gate lengte en fin breedte combinatie (aangeduid door het punt) om een ESD specificatie van 1 kV HBM en maximaal 4 V spanningsval te halen met de kleinst mogelijke layout. De ideale oplossing is dus niet een structuur met hele smalle of hele brede fins, maar ergens tussenin. Wanneer van dit optimum afgeweken wordt vergroot de benodigde layoutoppervlakte om aan de randvoorwaarden te voldoen heel snel, waarmee het nut van de ontwerpmethodologie bewezen wordt. Verder zorgt deze ontwerpmethodologie ook voor een dieper inzicht. Wanneer bijvoorbeeld voor een 1 kV HBM specificatie de maximale toegelaten

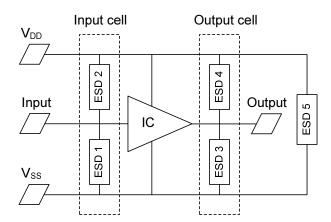

Figuur 0.10: Basis van on-chip ESD bescherming. Het circuit is een lage ruis versterker (LNA) die gebruikt wordt als demonstrator. ESD1-3 zijn de ESD beschermingsstructuren.

spanning verminderd wordt van 4.5 tot 2.7 V, kan men in Fig. 0.9 (rechts) verschillende zones onderscheiden hoe de optimale gate lengte en fin breedte zich moeten gedragen om tot het optimum te komen.

Al deze resultaten tonen aan dat de ESD gevoeligheid van FinFET structuren geen spelbreker is voor de introductie van FinFETs voor geavanceerde nanotechnologieën, zolang ESD reeds beschouwd wordt tijdens de technologieontwikkeling. Maar zelfs met deze kennis blijft het ontwerp van ESD bescherming voor FinFET technologie een uitdaging.

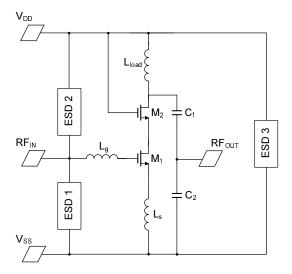

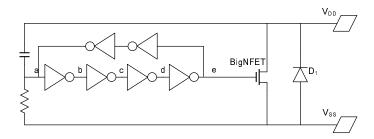

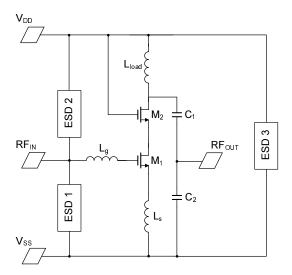

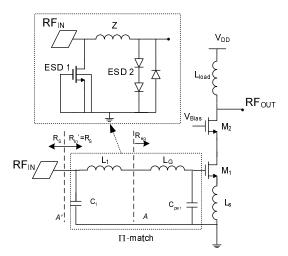

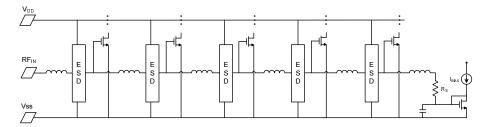

## ESD Bescherming voor Smalbandige RF CMOS Circuits

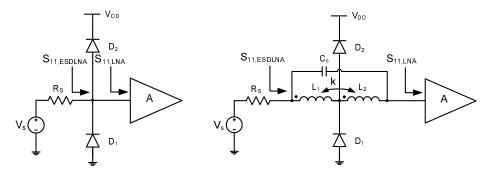

In een RF front-end, is de lage ruis versterker (LNA) één van de kritische elementen. Doordat hij via een antenne met de buitenwereld verbonden is, heeft de LNA ESD bescherming nodig. Deze ESD bescherming moet zodanig ontworpen worden dat de RF performantie van de LNA zo weinig mogelijk beïnvloed wordt. Een generieke ESD protectie wordt getoond in Fig. 0.10. Elementen ESD1 en ESD2 zorgen ervoor dat de ESD stroom van de RF input afgeleid wordt naar de voeding en grond. ESD3 zorgt voor ESD bescherming tussen voeding en grond.

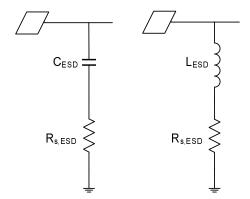

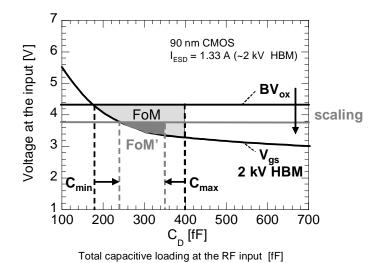

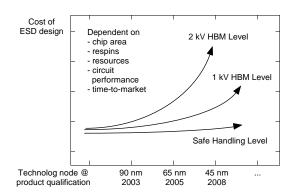

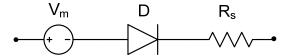

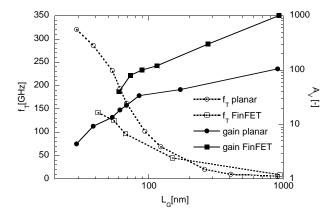

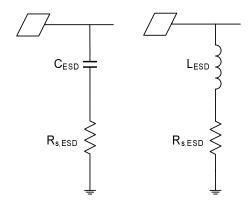

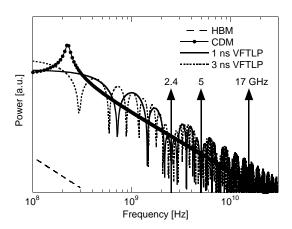

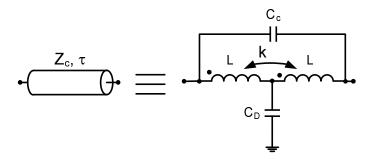

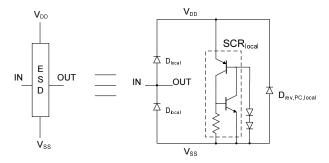

Om zo weinig mogelijk impact te hebben op de RF performantie van de LNA wordt traditioneel de capaciteit van de elementen ESD1 en ESD2 zo laag mogelijk gehouden. Een lagere capaciteit betekent echter kleinere ESD elementen en dus ook lagere ESD performantie. Het equivalente schema van een capacitieve ESD beschermingsstructuur wordt getoond in Fig. 0.11 (links). Bij

Figuur 0.11: Equivalent schema van capacitieve (links) ESD beschermingsstructuren, zoals diodes of grounded gate NMOS, en inductieve (rechts) ESD beschermingsstructuren.

stijgende RF frequentie zal de impedantie volgens (1) verminderen, waardoor de maximale toegestane capaciteit en dus grootte van de ESD structuur omwille van de RF specificaties van de LNA ook vermindert. Capacitieve ESD bescherming wordt dus moeilijker en moeilijker naarmate de RF frequentie hoger wordt, en uiteindelijk zelfs onbruikbaar.

$$|Z_{ESD}| = \left| R_{s,ESD} + \frac{1}{j\omega_{RF}C_{ESD}} \right| = \sqrt{R_{s,ESD}^2 + \frac{1}{\omega_{RF}^2 C_{ESD}^2}}$$

(1)

Men kan ook gebruik maken van inductieve ESD bescherming zoals getoond in Fig. 0.11 (rechts). De impedantie hiervan verhoogt met stijgende RF frequentie volgens (2), zodat deze oplossing beter wordt naarmate de frequentie hoger wordt. De spoel naar grond wordt toegevoegd als 'plug-and-play', dus zonder het oorspronkelijke RF ontwerp te wijzigen.

$$|Z_{ESD}| = |R_{s,ESD} + j\omega_{RF}L_{ESD}| = \sqrt{R_{s,ESD}^2 + \omega_{RF}^2 L_{ESD}^2}$$

(2)

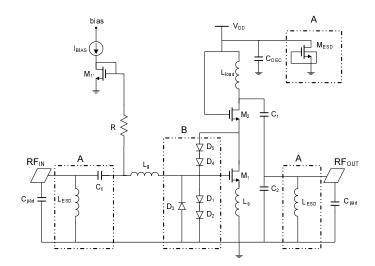

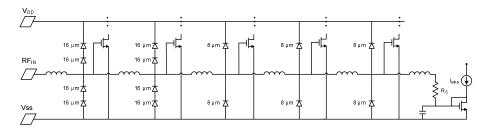

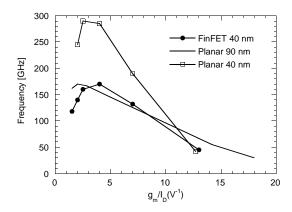

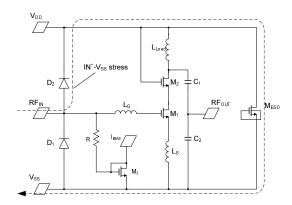

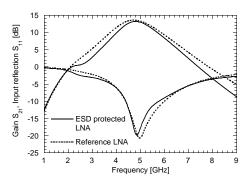

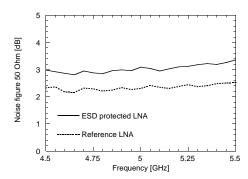

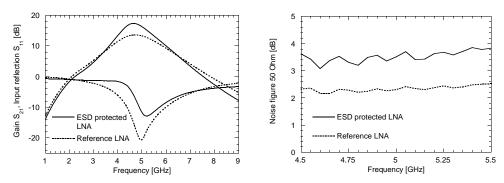

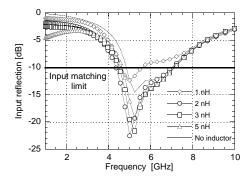

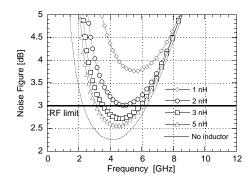

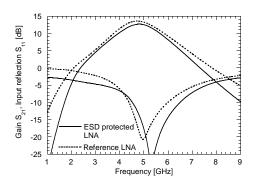

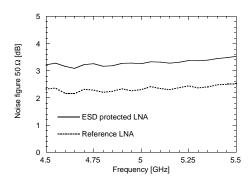

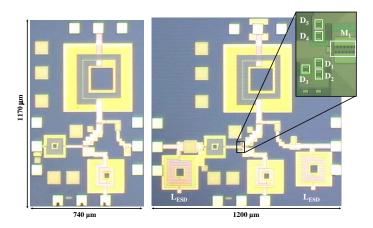

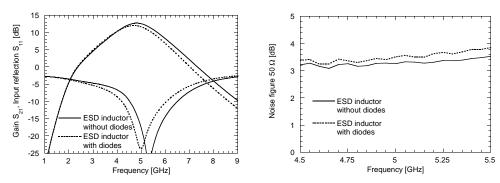

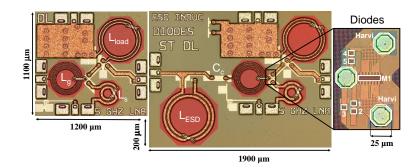

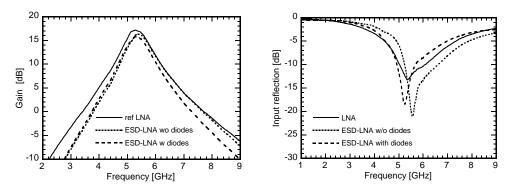

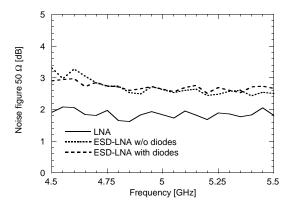

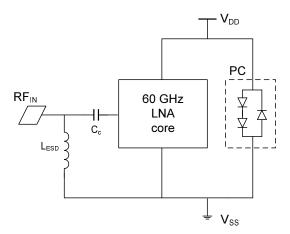

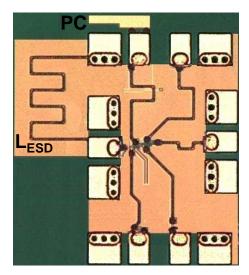

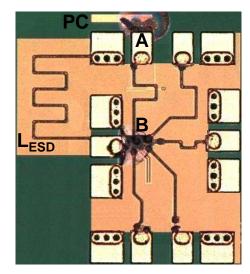

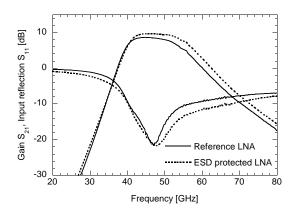

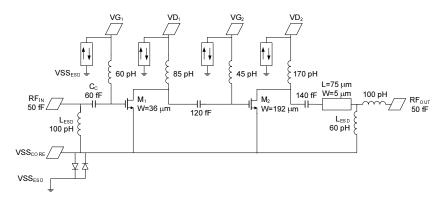

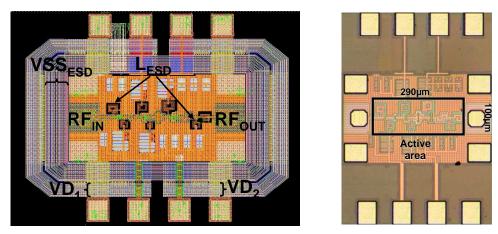

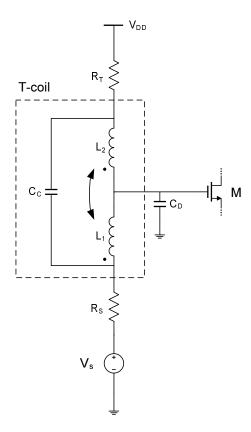

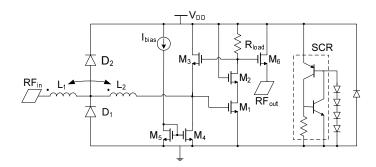

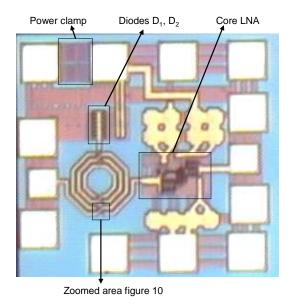

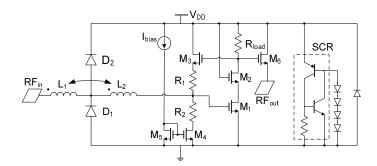

Om de limieten van capacitieve en het potentieel van inductieve ESD bescherming aan te tonen wordt een identieke 5 GHz LNA in een 90 nm CMOS technologie gebruikt als demonstrator. Het schema van de LNA met de inductieve ESD bescherming  $L_{ESD}$  wordt getoond in Fig. 0.12. De ontkoppelcapaciteit  $C_C$  is nodig in combinatie met  $L_{ESD}$  om de transistor  $M_1$  van instelspanning te kunnen voorzien. Door toevoegen van de klassieke dual diode bescherming of van de inductieve ESD bescherming worden de RF specificaties van de LNA gehaald. Er is echter een groot verschil in ESD performantie.

Figuur 0.12: Het schema van de lage ruis versterker met een spoel naar grond als ESD bescherming. Rechthoek A duidt de standaard ESD bescherming aan en B de extra ESD bescherming.

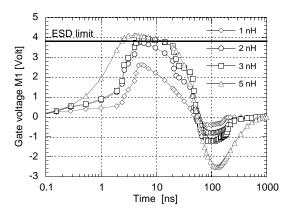

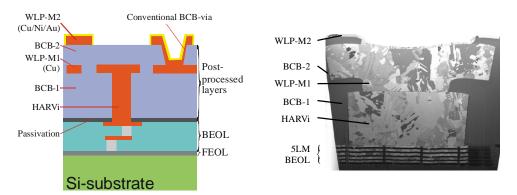

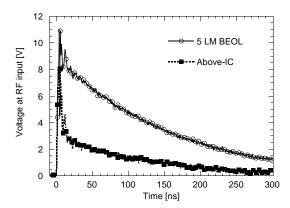

De LNA met dual diode ESD bescherming faalt bij 500 V HBM stress tussen  $RF_{IN}$  en  $V_{SS}$  omdat de maximale toegelaten spanning over het gate oxide van transistor  $M_1$  overschreden wordt. Door een spoel als ESD bescherming te gebruiken kan de ESD stroom in deze stress combinatie meteen van  $RF_{IN}$  naar  $V_{SS}$  gaan, zonder over de powerclamp  $M_{ESD}$  te hoeven gaan. Echter, wanneer deze ESD stroom door  $L_{ESD}$  gaat, wordt er een overspanning opgebouwd, die via de ontkoppelcapaciteit  $C_C$  op de gate van  $M_1$  gekoppeld wordt. Hierdoor kan de LNA beschermd worden tot 2.5 kV HBM. Door gebruik te maken van extra kleine diodes aan de gate van  $M_1$ , Box B in Fig. 0.12, wordt deze overspanning beperkt, en stijgt het HBM beschermingsniveau tot 5.5 kV met slechts minimale RF impact. Het HBM niveau kan verder nog verhoogd worden door gebruik te maken van Above-IC spoelen. Door hun hogere kwaliteitsfactor vermindert de overspanning en stijgt het HBM niveau tot 6 en >8 kV zonder en met extra diodes respectievelijk.

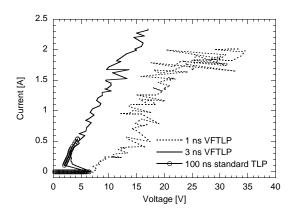

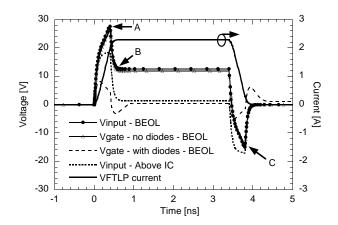

Omwille van de overspanningen die gegenereerd worden wanneer stroom door een spoel vloeit, is het nodig om naast HBM ook de CDM performantie van de inductieve ESD bescherming te bestuderen. Dit gebeurt aan de hand van onchip VFTLP metingen tussen de verschillende mogelijke pin-combinaties. Zo kunnen zwakke ESD paden opgespoord en gecorrigeerd worden. Een overzicht van de VFTLP resultaten tussen  $RF_{IN}$  en  $V_{SS}$  wordt gegeven in Tabel 0.1. De extra diodes verhogen de VFTLP performantie, net zoals bij HBM, terwijl gebruik van Above-IC zorgt voor ongeveer een verdubbeling van de VFTLP sterkte.

Tabel 0.1: Samenvatting van VFTLP meetresultaten (200 ps stijgtijd en 3 ns pulsbreedte).

| VFTLP $RF_{ m IN}+~V_{ m SS}$ - | Normal BEOL | Above-IC |

|---------------------------------|-------------|----------|

| No clamping diodes              | 0.9 A       | 1.7 A    |

| With clamping diodes            | 1.3 A       | 2.7 A    |

Tabel 0.2: Samenvatting van ESD meetresultaten van de 60 GHz LNA.

|           | $RF_{ m IN} + V_{ m SS}$ - | $V_{ m DD} + RF_{ m IN}$ - |

|-----------|----------------------------|----------------------------|

| HBM [kV]  | >8 kV                      | $6.3~\mathrm{kV}$          |

| VFTLP [A] | >10.6 A                    | 7.3 A                      |

Inductieve ESD bescherming is niet afhankelijk van de front-end, maar wordt voornamelijk bepaald door de back-end kwaliteit, die eerder constant blijft bij technologieschaling. Daarom wordt een even goed HBM beschermingsniveau, namelijk >5 kV, verkregen voor een 5 GHz LNA met inductieve bescherming, geïmplementeerd in zowel een 45 nm planaire als een 45 nm FinFET technologie. Bij gebruik van de klassieke dual-diode ESD bescherming zakt de ESD performantie van 2.5 kV voor de planaire technologie tot 850 V voor de FinFET technologie door de vermindering in sterkte van de ESD diodes.

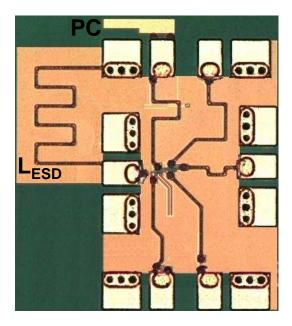

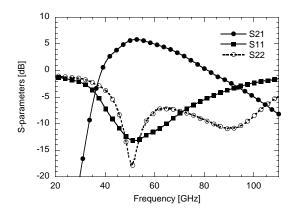

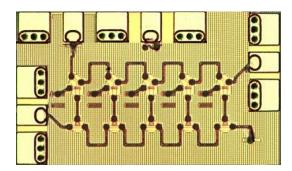

Door het verhogen van de RF frequentie kunnen spoelen met lagere inductantie gebruikt worden met minder wikkelingen, waardoor de benodigde oppervlakte verkleint alsook de serieweerstand. Doordat zowel de LdI/dt als de R\*I component van de overspanning verminderen, verbeteren zowel de HBM als de CDM performantie. Wanneer de RF frequentie hoog genoeg is, kan de spoel geïmplementeerd worden als een simpele  $\lambda/4$  microstriplijn die de RF ingang kortsluit naar de grond. Een voorbeeld hiervan wordt getoond in Fig. 0.13 voor een 60 GHz LNA. Extreem goede ESD resultaten, zowel HBM als VFTLP, kunnen bereikt worden. Een samenvatting van de meetresultaten wordt gegeven in Tabel 0.2.

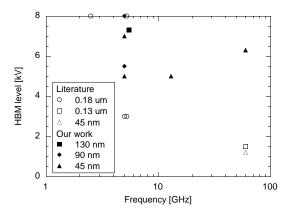

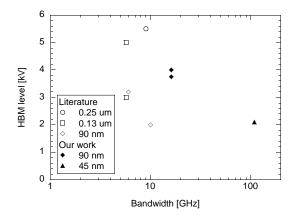

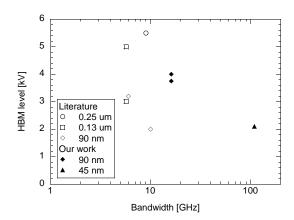

Door gebruik te maken van inductieve ESD bescherming en deze verder te optimalizeren met extra diodes en een Above-IC back-end, kan een zeer hoge ESD bescherming verkregen worden voor RF circuits met hoge werkingsfrequentie en geïmplementeerd in de meest geavanceerde CMOS technologieën. Het behaalde HBM resultaat als functie van de RF frequentie van onze circuits wordt vergeleken met de literatuur in Fig. 0.14. Het is duidelijk dat inductieve ESD bescherming de beste RF-ESD resultaten behaalt.

Tot 5 GHz kunnen de klassieke dual diodes gebruikt worden voor RF-ESD

Figuur 0.13: Micrograph van een 60 GHz LNA met  $\lambda/4$  microstriplijn als ESD bescherming.

Figuur 0.14: Vergelijking van ons werk (volle symbolen) met andere gepubliceerde smalband CMOS LNA resultaten (open symbolen). De HBM performantie [kV] is geplot als functie van RF frequentie [GHz].

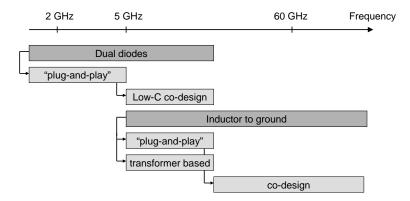

bescherming. Wanneer men deze wil blijven gebruiken boven 5 GHz moet men de parasitaire capaciteit mee in het RF ontwerp opnemen, de zogenaamde co-design aanpak, evenwel met een beperkte ESD bescherming als resultaat. Vanaf 5 GHz kan inductieve ESD bescherming gebruikt worden. Om geen extra oppervlakte te gebruiken voor de ESD beschermingsspoel, kan deze onder een RF matching spoel geschoven worden, waardoor een transformator gemaakt wordt. Deze aanpak vereist een complexer RF ontwerp. Naarmate

Figuur 0.15: Smalbandige RF-ESD beschermingsmethodologie als functie van applicatie frequentie.

de RF frequentie hoger wordt, wordt de benodigde oppervlakte van de ESD beschermingsspoel kleiner, zodat de eenvoudige spoel-naar-grond methode te verkiezen valt boven de transformator. Bij nog hogere RF frequenties kan het wenselijk zijn om de ESD spoel in het RF ontwerp op te nemen om zo bijvoorbeeld de extra bondpadcapaciteit weg te tunen. Een overzicht van de RF-ESD beschermingsmethodologie als functie van RF frequentie wordt weergegeven in Fig. 0.15.

## ESD Bescherming voor Breedbandige RF CMOS Circuits

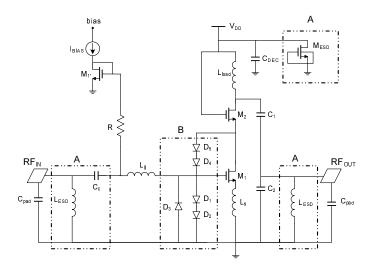

Breedband RF circuits worden meer en meer geïmplementeerd in CMOS, en daarom is er een nood voor gepaste ESD bescherming voor deze circuits. Smalbandige ESD oplossingen, zoals beschreven in de vorige sectie, kunnen niet gebruikt worden omdat ze slechts werken in een smalle band rond een bepaalde frequentie. De bestaande breedband RF-ESD oplossingen zijn beperkt in RF performantie, vermogenverbruik, ESD performantie of gebruiken te veel silicium oppervlakte. Daarom worden in dit hoofdstuk twee nieuwe breedbandige RF-ESD oplossingen gepresenteerd.

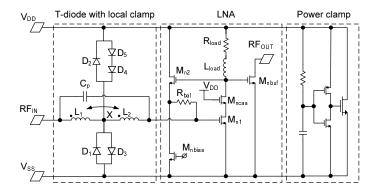

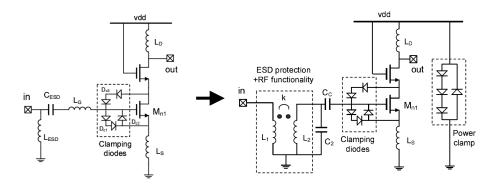

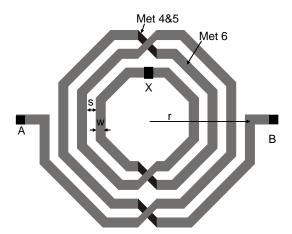

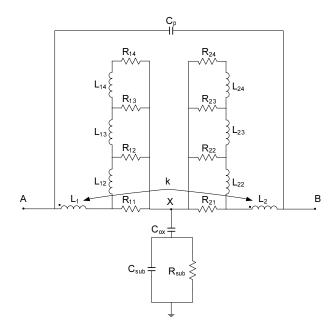

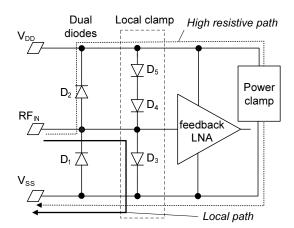

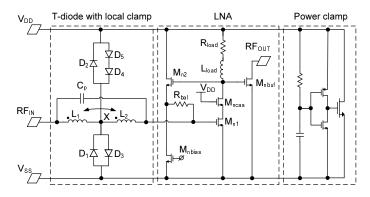

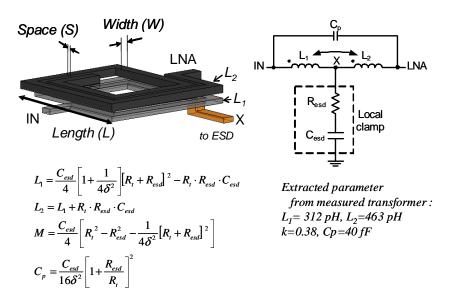

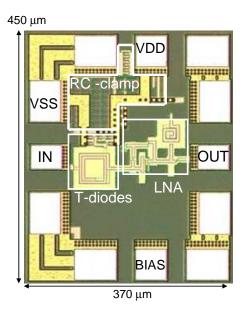

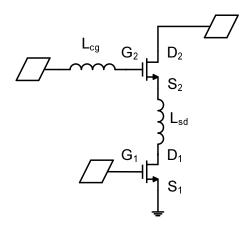

De capacitieve belasting van een klassieke dual diode ESD oplossing zorgt ervoor dat deze methode slechts beperkt gebruikt kan worden bij hogere RF frequenties, zoals besproken in de vorige sectie. Door gebruik te maken van een transformator rond de ESD diodes, kan hun parasitaire capaciteit onzichtbaar gemaakt worden over een hele brede frequentieband, de zogenaamde T-diode oplossing. Op deze manier wordt een artificiële transmissielijn gemaakt die zowel een ingangs- als een uitgangsimpedantie van 50  $\Omega$  heeft. Omdat op deze manier redelijk grote capaciteiten kunnen weggetuned worden, kunnen we zelfs gebruik maken van 'lokale clamping' aan de RF ingang, zoals getoond in Fig. 0.16. Diodes  $D_1$  en  $D_2$  vormen de klassieke dual diode oplossing, terwijl diodes  $D_3$ - $D_5$  ervoor zorgen dat de ESD stroom lokaal aan de RF-ingang kan

Figuur 0.16: Schema van ESD beschermde wideband RF LNA met T-diode en lokale clamping.

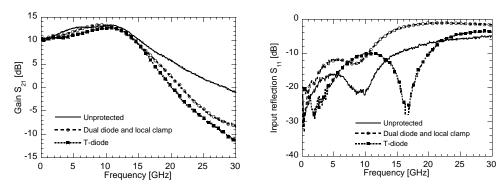

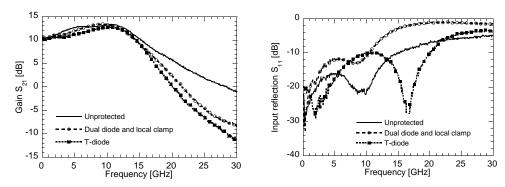

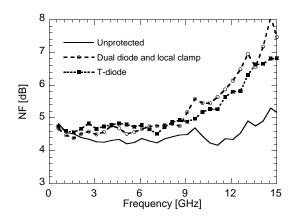

Figuur 0.17: Gemeten versterking  $S_{21}$  (links) en input matching  $S_{11}$  (rechts) van: onbeschermde LNA, LNA met dual-diode en lokale clamp ESD bescherming, en T-diode ESD bescherming met lokale clamp.

wegvloeien, zonder over de power clamp te moeten gaan. Het aantal diodes in serie van de lokale clamping hangt af van de benodige instelspanning voor de LNA.  $L_1$ ,  $L_2$  en  $C_p$ , Fig. 0.16, vormen samen met de ESD diodes de T-diode. Op deze manier wordt een DC-tot-16.1 GHz breedband LNA, geïmplementeerd in 90 nm digitale CMOS, beschermd tegen ESD.

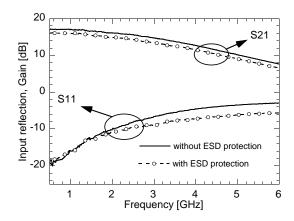

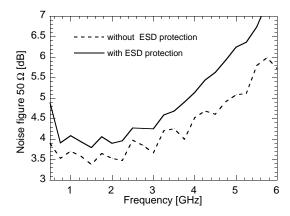

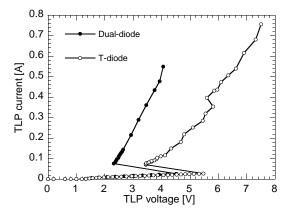

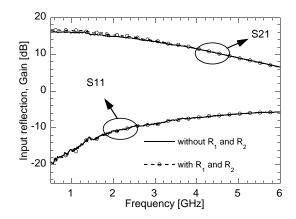

Wanneer men deze dual diode met lokale clamping gebruikt zonder de T-diode, degradeert de input matching bandbreedte met 3 GHz, ten opzichte van het onbeschermde circuit volgens Fig. 0.17 (rechts). Door gebruik te maken van de T-diode als ESD bescherming verbetert de input matching van de breedband LNA zelfs van 14.5 GHz voor de onbeschermde LNA tot 20.1 GHz, Fig. 0.17 (rechts), terwijl de versterking nagenoeg ongewijzigd blijft, Fig. 0.17 (links). De HBM performantie verbetert van 1.5 kV zonder lokale clamping tot 4 kV met lokale clamping voor stress tussen  $V_{DD}$  en  $RF_{IN}$ .

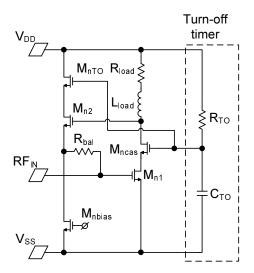

Bij bepaalde pin combinaties kan tijdens ESD stress een parasitair stroompad

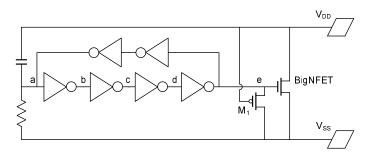

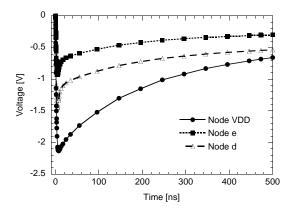

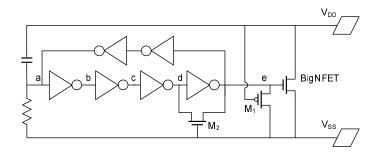

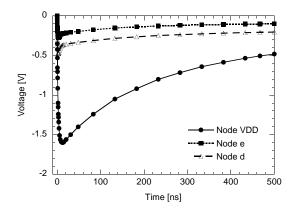

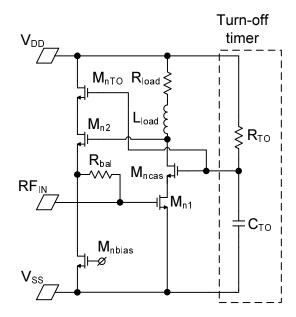

Figuur 0.18: LNA topologie met ESD afschakelcircuit.

gevormd worden door de LNA kern, bijvoorbeeld door de feedback transistor  $M_{n2}$  of de cascode transitoren  $M_{n1}$  en  $M_{ncas}$ , Fig. 0.16. Een elegante methode bestaat erin deze parasitaire paden uit te schakelen tijdens ESD door middel van een ESD afschakelcircuit, Fig. 0.18. De RC-timer  $R_{TO}$  en  $C_{TO}$  zorgen ervoor dat beide parasitaire stroompaden afgeschakeld zijn tijdens ESD stress. Deze methode kan eenvoudig geïmplementeerd worden en neemt geen extra plaats in, omdat in een RF circuit typisch heel veel ontkoppelcapaciteiten aanwezig zijn die gebruikt kunnen worden als  $C_{TO}$ .

Voor stress tussen  $V_{DD}$  en  $RF_{IN}$ , vormt de feedbackweerstand  $R_{bal}$  de zwakke schakel. Zelfs met lokale clamping vemindert de HBM performantie van 4 kV tot 2.25 kV door toevoeging van  $R_{bal}$ . De HBM sterkte wordt terug hersteld tot 4 kV door gebruik te maken van het extra afschakelcircuit. Een overzicht van de ESD resultaten wordt weergegeven in Tabel 0.3. Deze afschakelmethode is een algemene ESD beschermingstechniek die niet beperkt wordt tot het gebruik voor breedband RF circuits.

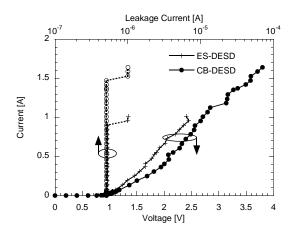

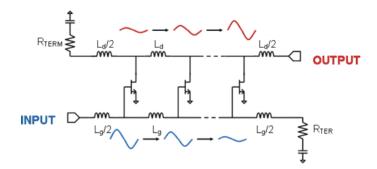

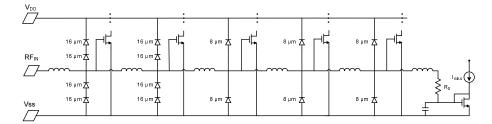

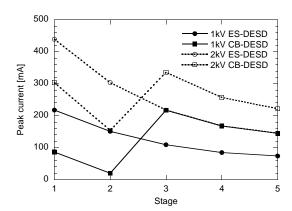

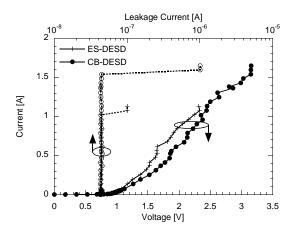

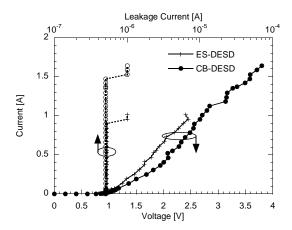

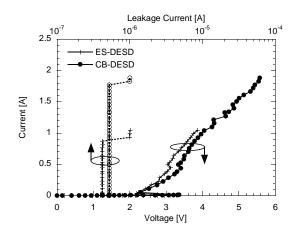

Een tweede breedband RF oplossing is een optimalisatie van de gedistribueerde ESD bescherming die typisch gebruikt wordt bij gedistribueerde versterkers (Distributed Amplifier DA). Bij dergelijke ESD bescherming worden er ESD componenten voorzien aan iedere versterkingstrap. Het geheel van de verschillende ESD componenten moet een voldoende ESD bescherming geven. Wanneer de ESD elementen in de verschillende trappen even groot genomen worden (Equally Sized Distributed ESD ES-DESD), kunnen de versterkingstrappen identiek ontworpen worden, maar de ESD efficiëntie vermindert bij iedere trap. Een optimalizatie hiervan maakt de ESD elementen in de eerste trap het grootste en verkleint deze bij iedere volgende trap. Een voordeel hiervan is

Tabel 0.3: Samenvatting van on-wafer HBM meetresultaten [kV].

| $R_{ m bal}$ | Local    | Turn-off | Turn-off | Turn-off | HBM [kV]                   | HBM [kV]                  |

|--------------|----------|----------|----------|----------|----------------------------|---------------------------|

|              | clamping | 500 ns   | 200 ns   | 20 ns    | $V_{ m DD}{+}RF_{ m IN}$ - | $V_{ m DD} + V_{ m SS}$ - |

| -            | -        | -        | -        | -        | 1.5                        | 3                         |

| -            | X        | -        | -        | -        | 4                          | -                         |

| X            | X        | -        | -        | -        | 2.25/2.4                   | 4.75                      |

| X            | X        | X        | -        | -        | 4                          | 7                         |

| -            | -        | X        | -        | -        | 3.75                       | 6.5                       |

| -            | -        | -        | X        | -        | 3.75                       | -                         |

| -            | -        | -        | -        | X        | 3.75                       | -                         |

Figuur 0.19: Schema van de gate transmissie lijn van de DA met CB-DESD bescherming.

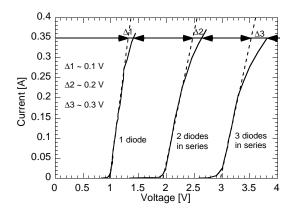

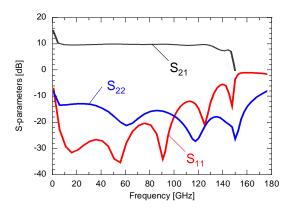

een betere algehele ESD efficiëntie, maar hierbij moet iedere versterkingstrap afzonderlijk ontworpen worden. Om het RF ontwerp zo eenvoudig mogelijk te houden en toch een betere ESD performantie dan bij ES-DESD te halen kan men een centraal gebalanceerde gedistribueerde ESD (Center Balanced Distributed ESD CB-DESD) strategie gebruiken. Hierbij worden de ESD diodes in de eerste twee versterkingstrappen dubbel zo groot gemaakt en met twee in serie geplaatst, zoals te zien is in Fig. 0.19. Op deze manier is de totale parasitaire capaciteit van de eerste twee trappen ongeveer even groot als in de laatste drie trappen en kunnen bijgevolg de versterkingstrappen identiek blijven. Deze oplossing is geïmplementeerd voor een 1-110 GHz DA met vijf trappen, in een 45 nm CMOS technologie met Above-IC back-end.

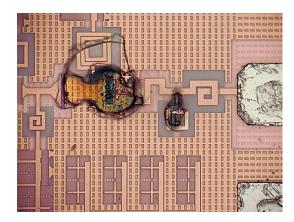

Omdat de eerste twee trappen twee diodes in serie hebben zal tijdens ESD stress de derde trap als eerste aangaan. Vervolgens wordt de ESD stroom verspreid over de vierde en vijfde trap, totdat de spanning aan de eerste trap hoog genoeg is zodat de twee diodes beginnen geleiden. Op dit moment nemen dan ook de eerste trap en uiteindelijk de tweede trap deel aan de ESD geleiding, zodat de ESD stroom over de vijf trappen verdeeld wordt. Doordat de stroom meer uniform verdeeld wordt over de verschillende trappen wordt een 65 % hogere faalstroom bekomen bij CB-DESD tijdens TLP metingen tussen  $RF_{IN}$ + en  $V_{DD}$ - vergeleken met ES-DESD, zoals te zien is in Fig. 0.20.

Figuur 0.20: TLP-IV meting voor stress tusssen  $RF_{IN}+$  en  $V_{DD}-$ . CB-DESD heeft 65 % verbeterde  $It_2$  ten opzichte van ES-DESD.

Figuur 0.21: Vergelijking van ons werk (volle symbolen) met andere gepubliceerde breedband CMOS LNA resultaten (open symbolen). De HBM performantie [kV] is geplot als functie van RF frequentie [GHz].

In Fig. 0.21 worden deze twee nieuwe breedband RF-ESD oplossingen vergeleken met de beschikbare oplossingen in literatuur. Met de T-diode en CB-DESD kan een heel goede ESD bescherming verkregen worden voor hele breedbandige RF circuits, zelfs geïmplementeerd in zeer geavanceerde CMOS technologieën.

## Conclusies

ESD is geen spelbreker voor de introductie van FinFET technologie, op voorwaarde dat een ontwerpmethodologie gebruikt wordt om het delicate layout optimum en de geschikte process opties te selecteren. Verder kunnen er ESD oplossingen geïmplementeerd worden voor smal- en breedbandige RF circuits die zowel een uitstekende RF als ESD performantie halen.

# Table of Contents

| $\mathbf{A}$ | bstra            | $\operatorname{ct}$                                   | vii       |  |  |  |

|--------------|------------------|-------------------------------------------------------|-----------|--|--|--|

| Li           | st of            | Acronyms                                              | ix        |  |  |  |

| Li           | st of            | Symbols                                               | xiii      |  |  |  |

| P            | ublica           | ation list                                            | xxviii    |  |  |  |

| N            | $\mathbf{ederl}$ | andstalige Samenvatting                               | xxix      |  |  |  |

| Ta           | able o           | of Contents                                           | xlvii     |  |  |  |

| 1            | Intr             | oduction                                              | 1         |  |  |  |

|              | 1.1              | Reliability in Advanced CMOS Technologies             | . 1       |  |  |  |

|              | 1.2              | Electrostatic Discharge in Micro-Electronics          | . 2       |  |  |  |

|              | 1.3              | Basic Concepts of ESD Protection                      |           |  |  |  |

|              | 1.4              | Basic ESD Protection Devices                          | . 5       |  |  |  |

|              | 1.5              | ESD Challenges for Technology Scaling                 | . 8       |  |  |  |

|              | 1.6              | ESD Challenges for Radio Frequency CMOS               | . 10      |  |  |  |

|              | 1.7              | Objectives of the Thesis                              | . 12      |  |  |  |

|              | 1.8              | Outline of the Thesis                                 | . 12      |  |  |  |

| <b>2</b>     | $\mathbf{ESI}$   | O Characterization and Analysis Techniques            | <b>15</b> |  |  |  |

|              | 2.1              | Introduction                                          | . 15      |  |  |  |

|              | 2.2              | Component-Level ESD Stress Models                     | . 16      |  |  |  |

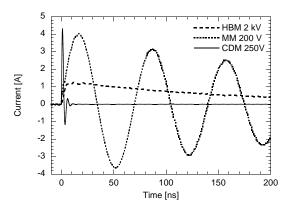

|              |                  | 2.2.1 Human Body Model (HBM)                          | . 16      |  |  |  |

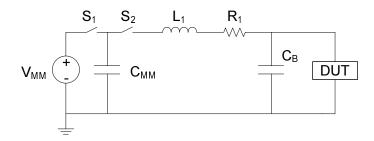

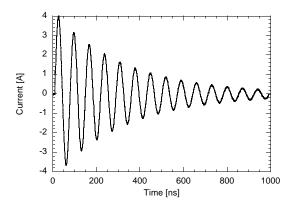

|              |                  | 2.2.2 Machine Model (MM)                              | . 18      |  |  |  |

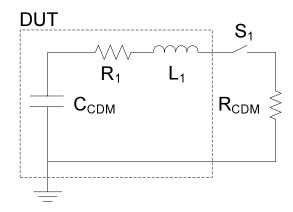

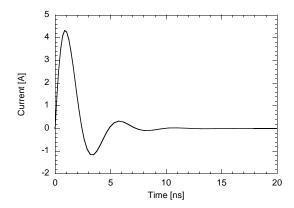

|              |                  | 2.2.3 Charged Device Model (CDM)                      | . 20      |  |  |  |

|              | 2.3              | System-Level ESD Stress Models                        | . 21      |  |  |  |

|              |                  | 2.3.1 IEC 61000-4-2                                   | . 22      |  |  |  |

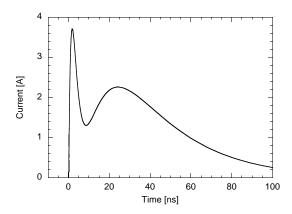

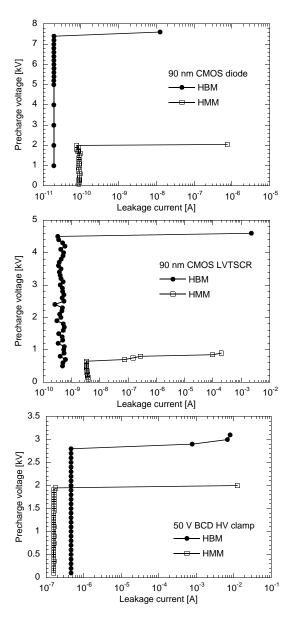

|              |                  | 2.3.2 Human Metal Model (HMM)                         | . 23      |  |  |  |

|              | 2.4              | Transmission Line Pulse Measurements (TLP)            | . 24      |  |  |  |

|              |                  | 2.4.1 Standard 100 ns TLP                             | . 26      |  |  |  |

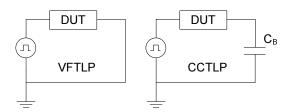

|              |                  | 2.4.2 Very Fast TLP (VFTLP)                           |           |  |  |  |

|              |                  | 2.4.3 Capacitive Coupled TLP (CCTLP)                  |           |  |  |  |

|              | 2.5              | Enhanced ESD Characterization and Analysis Techniques |           |  |  |  |

|              |                  | 2.5.1 Multi-level TLP                                 | . 31      |  |  |  |

|              |                  | 2.5.2 Transient analysis using TLP                    |           |  |  |  |

|              |                  | 2.5.3 HBM-IV                                          |           |  |  |  |

|              | 2.6              |                                                       |           |  |  |  |

| 3 | ESI            | ) Prot | ection in FinFET Technology                                               | <b>53</b> |

|---|----------------|--------|---------------------------------------------------------------------------|-----------|

|   | 3.1            | Introd | luction                                                                   | 53        |

|   | 3.2            | FinFE  | ET Technology                                                             | 54        |

|   | 3.3            | Norma  | alization Methodology                                                     | 55        |

|   | 3.4            |        | etrical Dependencies                                                      | 58        |

|   |                | 3.4.1  | MOS devices - parasitic bipolar mode                                      | 58        |

|   |                | 3.4.2  | MOS devices - active MOS-diode mode                                       | 80        |

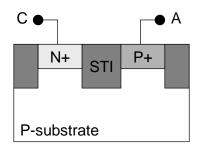

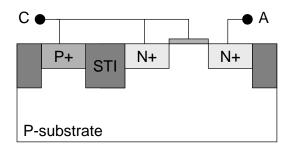

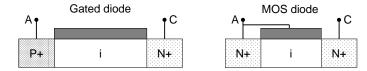

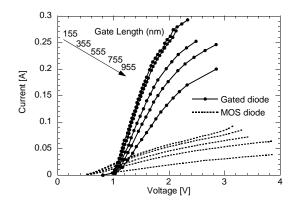

|   |                | 3.4.3  | Gated diodes                                                              | 82        |

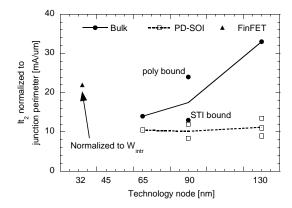

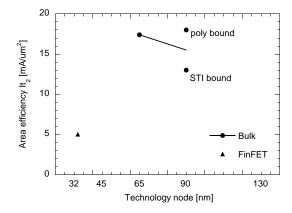

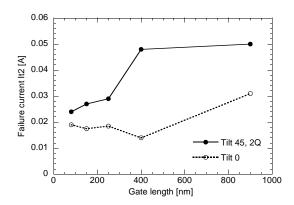

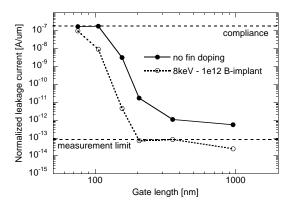

|   | 3.5            | Bench  | marking against Advanced CMOS Technology Nodes                            | 85        |

|   | 3.6            | Proces | ss Technology Dependencies                                                | 88        |

|   |                | 3.6.1  | Extension implants                                                        | 88        |

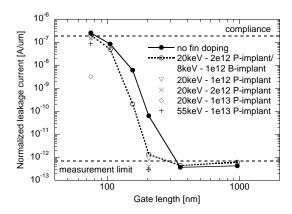

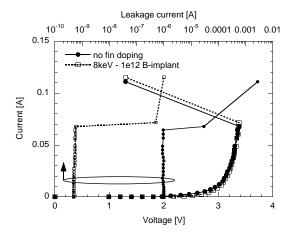

|   |                | 3.6.2  | Fin doping on wide fin devices                                            | 89        |

|   |                | 3.6.3  | Selective Epitaxial Growth                                                | 91        |

|   |                | 3.6.4  | Silicide Blocking                                                         | 95        |

|   |                | 3.6.5  | Strain                                                                    | 96        |

|   | 3.7            | Gated  | Diodes - RF Considerations, Transient Analysis and                        |           |

|   |                | Model  | ling                                                                      | 105       |

|   |                | 3.7.1  | RF considerations                                                         | 106       |

|   |                | 3.7.2  | Transient analysis and compact modeling                                   | 107       |

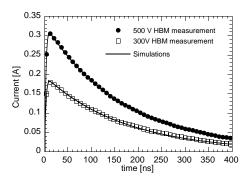

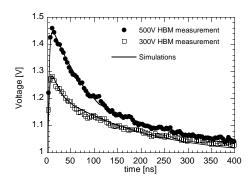

|   | 3.8            | Design | n Methodology                                                             | 117       |

|   |                | 3.8.1  | MOS devices - parasitic bipolar mode                                      | 118       |

|   |                | 3.8.2  | MOS devices - active MOS diode mode                                       | 125       |

|   |                | 3.8.3  | Optimization constraint trajectory                                        | 128       |

|   |                | 3.8.4  | Bidirectional power clamp                                                 | 132       |

|   | 3.9            | Concl  | usions                                                                    | 136       |

| 4 | $\mathbf{ESI}$ | ) Prot | ection for Narrowband RF CMOS Circuits                                    | 139       |

|   | 4.1            | Introd | luction                                                                   | 139       |

|   | 4.2            | Dual 1 | Diode Methodology                                                         | 145       |

|   | 4.3            | Codes  | ign Methodology                                                           | 147       |

|   | 4.4            | Induct | tor to Ground Methodology                                                 | 149       |

|   |                | 4.4.1  | Back-end of line (BEOL) inductor                                          | 150       |

|   |                | 4.4.2  | Above-IC inductor                                                         | 155       |

|   |                | 4.4.3  | VFTLP results                                                             | 158       |

|   |                | 4.4.4  | Overall comparison                                                        | 161       |

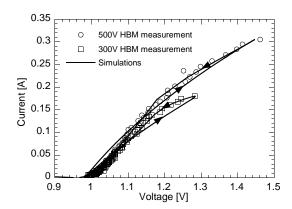

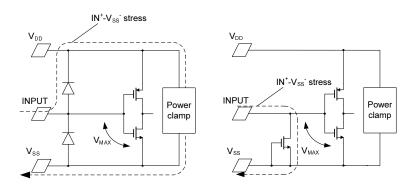

|   | 4.5            | Scalin | g Aspects of Inductor to Ground Approach                                  | 161       |